def_rain

Свой-

Постов

315 -

Зарегистрирован

-

Посещение

Весь контент def_rain

-

Да, скорости не большие. Но во втором варианте, (когда не последовательно проходит) настораживает что получаются большие ответвления от общей шины CLK. Может кто то поделится статейками или даташитами, где есть инфа по рекомендациям трассировки SPI?

-

Не то и не то. Подтягивающий резистор чтобы линию нагрузить, с целью избежать возможных наводок. Скорость небольшая, 100кГц

-

Как лучше трассировать CLK для SPI. Два варианта

def_rain опубликовал тема в Работаем с трассировкой

Здравствуйте. Требуется совет опытного практика. Разные мнения тоже будет интересно почитать. Есть плата, на ней 9 микросхем соединены по SPI. Рассмотрим общую картину на примере дорожки CLK. Есть два варианта трассировки: 1. Провести CLK последовательно (гребенкой) через все микросхемы и возле последней микросхемы поставить подтягивающий резистор. Но при этом плату нужно будет сделать 8-ми слойную и длинна этой дорожки CLK получается внушительной 260мм. 2. Разбить микросхемы на 3 группы (так удобнее на плате, микросхемы разные по назначению) и провести CLK звездой. При этом подтягивающие резисторы поставить в конце каждого из трех ответвлений звезды. В этом случае плата 6 слойная и дорожки по длинне в 2 раза короче. Какой вариант будет предпочтительнее? PS Дорожки веду исключительно во внутренних слоях. Возможны помехи, потому что в 20 мм над этой платой на стойках установлена вторая плата с большим количеством реле, которые коммутирую токи но несколько ампер AC и DC, также есть пусковые токи. Спасибо. -

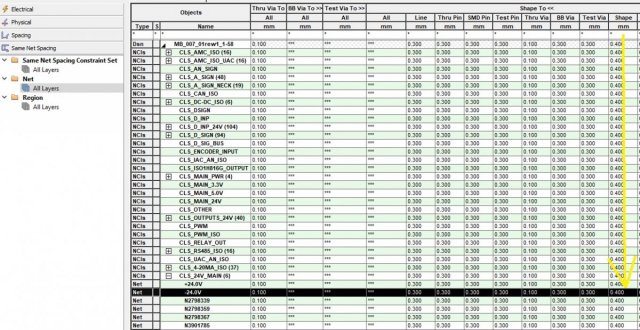

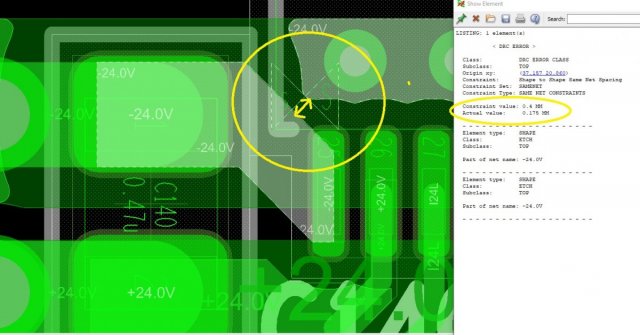

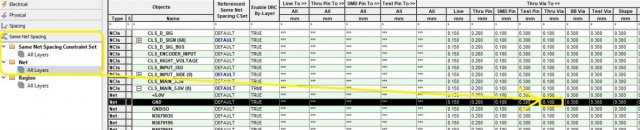

Здравствуйте, уважаемые. Быстрый вопрос по Same net spacing - Sape to Sape, настраиваю клиренс между двумя полигонами -24V (см. фото). В CM установил нужный клиренс в Same net, в Analisys Mode поставил галочки где нужно. Но зазор не изменился. При этом DRC срабатывает как нужно. Как увеличить зазор? Раньше таких проблем не было. PS Разобрался. Нужно к полигонам задать св-во Void same net.

-

У меня 17.2 с плавающей сетевой лицензией. Тормоза появляются в больших многослойных проектах, где полно крупных полигонов.

-

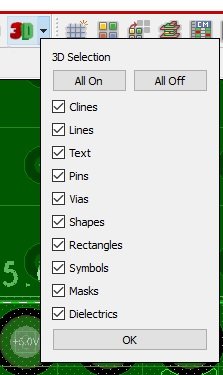

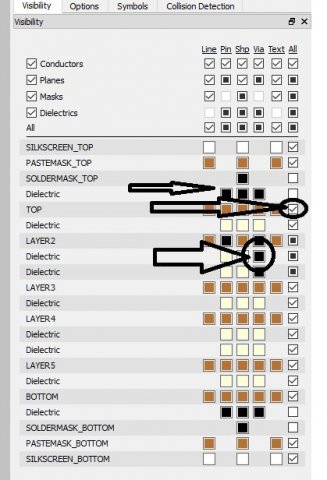

Никогда такого окна не видел. 1. Если вы имеете в виду то что будет отображено в 3Д CANVAS после того как откроется этот редактор, т.е. самому задать то что будет там изображено, то просто проставьте галочки в падающем меню (нажать на треугольничек) рядом с графической кнопкой 3D в PCB Editor. См. Рис1. 2. Если вы хотите выбрать то что будет экспортироваться в Степ из 3Д CANVAS, то проставьте галочки или скройте ненужные слои вручную прощелкав квадратики (скрыть компоненты во вкладе Symbols).

-

Спасибо, как всегда выручаете!

-

Товарищи, подскажите пожалуйста. Хотел создать Механический символ, нарисовал всё как хотел, но когда он сохранился, почему то оказался обычным символом с REFDES. Подскажите, можно ли как то сохранить(или конвертировать как то) его как механический символ. Перерисовывать не хочется.... Спасибо.

-

Спасибо, помогло! Что то сам не додумался...

-

Быстрый вопрос: Как продублировать дорожку которая идет от одного thru pin до другого thru pin на разных слоях ? PCB Editor не дает этого сделать, он просто перерисовывает эту дорожку удаляя её с предыдущего слоя. PS Делать с помощью shape не предлагать. Спасибо!

-

А Резонит справляется без вопросов с такими отверстиями. Да, я видел такие конструкции, это специальные площадки для жесткого крепления платы шурупами, винтиками. А via с ТОПа на БОТом по окружности, сделаны для того чтобы при сильной затяжке винта, этот винт не выдрал вот эту круглую медную площадку с платы. Может с первого раза он её и не повредит, но если пару раз прикручивать откручивать плату эта металлизация быстро сжёвывается. А если укрепить по периметру с помощью via, получается более надежный вариант.

-

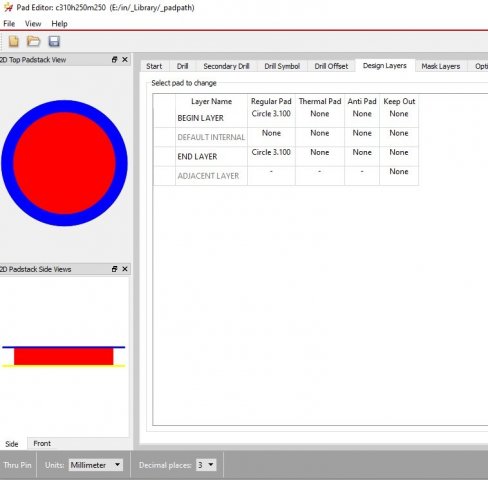

Если точнее, то получается нечто среднее. Нельзя сказать что без меди, т.к. она есть на ТОП и БОТ. Но и не полностью с металлизированное, т.к. на внутренних слоях её нет. Редактор допускает это сделать (Падстэк эдитор), значит и такой тип отверстий должен как то контролироваться в CM. Вот только как? Скажите, а с помощью Unused Pad Supression получается что будут удалены неиспользуемые площадки у всех объектов, за исключением тех у кого вручную будет установлено свойство ignore Unused Pad? Просто в моем случае, это опять ручная правка...

-

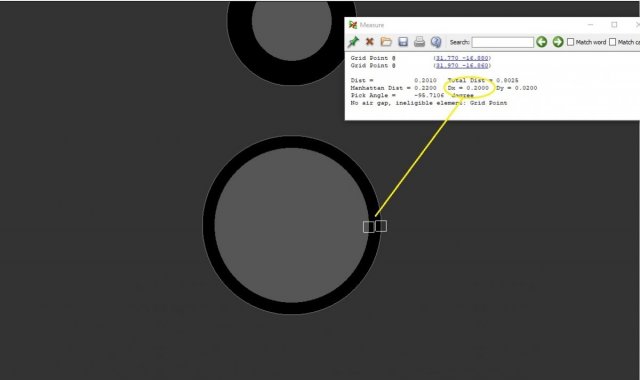

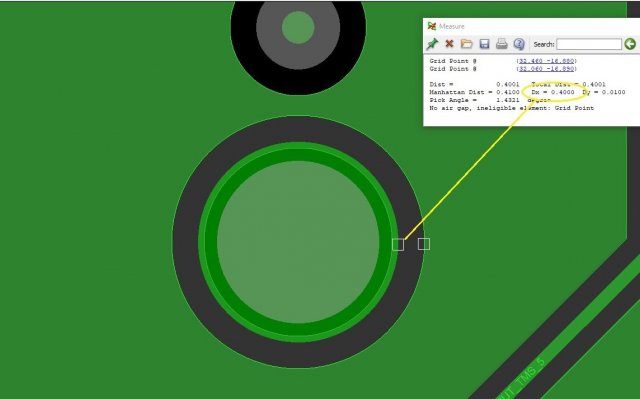

Да, я тоже так думал. Но этот способ тоже не сработал. Я задаю в CM клиренс shape to hole, но для конкретно этого отверстия правило не срабатывает. Хотя для других механических отверстий это работает. Я всё таки полагаю что здесь дело именно в том что сам падстэк создан без использования внутренних слоев и добавлен на многослойную плату. Но мне не нужны здесь внутренние окантовки вокруг отверстия, т.к. не будет электрических связей.

-

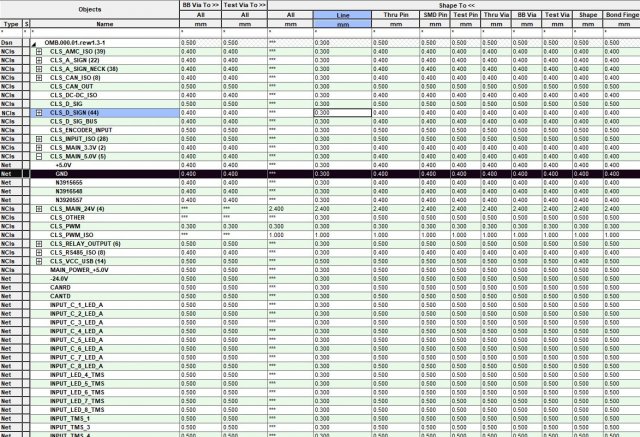

Товарищи, помогите разобраться. Суть вопроса как поменять отступ полигона от thru pin. Я знаю два способа: первый в CM; второй через индивидуальные свойства Property edit Однако, в моем случае клиренс во внутренних слоях почему то невозможно поменять через CM, только через Property edit. Через CM меняется только на внешних слоях (0.4мм). А хотелось бы всё автоматизировать и вообще разобраться. Ведь редактор сам устанавливает некий клиренс в 0.2мм для внутренних слоев (от hole до полигона), откуда он берет это значение? Есть зацепка, что данный thru pin сделан в padstack editor без внутренних слоев, хотя внутренние слоя фактически на плате есть. Это механическое, крепежное отверстие с металлизацией на топ и боттом. Меня не очень радует перспектива прописывать вручную каждый раз для всех этих отверстий в Property edit нужные значения отступов для внутренних слоев. Проще настроить один раз в CM и пользоваться из проекта в проект.

-

Здравствуйте. Может кто нибудь сталкивался с интересной тонкостью работы Capture, связанной с электрическим соединением двух компонентов друг к друг. Если их соединить без дорожки (Net alias), а просто Пин одного компонента к Пину другого ( при этом при трассировки платы всё в порядке, RATnets есть, дорожки провести можно), то перестает работать Backannotation для данного соединения до тех пор, пока в схеме не раздвинешь эти два компонента, что бы между ними появилась дорожка и не сделаешь заново нетлист. Другими словами, такую дорожку не получится переместить в какой нибудь класс (CLS) в CM, т.к. при последующем нетлисте, дорожка опять окажется без присвоенного класса. Я когда то давно, еще в 16.6 (сейчас стоит OrCAD PCB Des.Pro.17.2 с хотфиксами) тоже замечал такую неприятную особенность. Приходится постоянно контролировать это в Capture. Вот думаю, может это настраивается и где то есть галочка которая за это отвечает. Иначе я воспринимаю такую особенность просто как баг.

-

Действительно. Ваш способ работает. Спасибо!

-

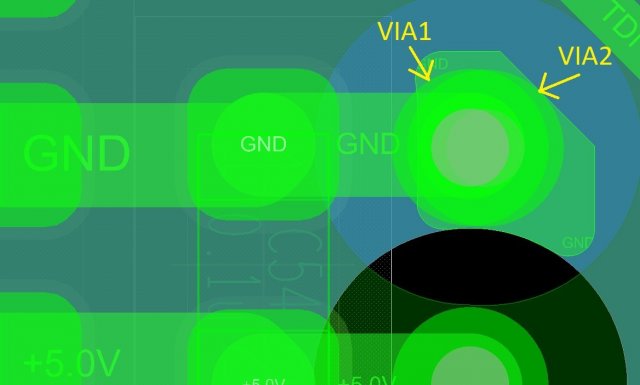

Здравствуйте. Не срабатывает правило для двух ВИА которые относятся к одной цепи если их наложить одно на другое (как на фото). Но здесь есть интересный момент, наличие DRC зависит от того как именно пересекаются ВИА: с нахлестом сверловки друг на друга или без нахлеста сверловки (см. фото). Если у ВИА сверловки пересеклись, то DRC не появляется (вопрос почему?), Если сверловки не пересеклись, то DRC как полагается есть. Констреинт настроен и в Analysis Mode стоит галочка Thru VIA to Thru VIA. Может быть кто нибудь подскажет как сделать так, чтобы DRC появлялось всегда когда случайно наложились ВИА друг на друга? Такие моменты на больших платах очень легко прозевать. Думаю как обезопасить себя от ошибок такого плана. Спасибо

-

Спасибо! Это было именно то что нужно.

-

А какой у Вас редактор? У меня в Manufacture нет Create Artwork. Я помню что в Аллегро там Гербер файлы можно сгенерировать... Но в OrCad PCB Designer Professional 17.2 Гербера делаются в Export - Gerber. И там я не вижу каких то инструментов чтобы можно было полигон скопировать в другой проект...

-

Здравствуйте. Подскажите пожалуйста по элементарному вопросу: как в OrCad PCB Designer Professional 17.2 скопировать полигон из одного проекта в другой? (Хот фикс один из последних) Раньше пользовался функцией sub drawing, но то был Аллегро насколько помню, да и версия 16.6. Сейчас этого инструмента что то не вижу нигде. Иногда крайне необходимо просто взять полигон класса BOARD GEOMETRY - CUTOUT и скопировать его в другой проект. Это сложные вырезы в плате с закруглениями по диаметру фрезы.

-

Работа сайта и сервера

def_rain ответил admin тема в Новости и обсуждения сайта и форума

Спасибо. Работает. Только в разы дольше чем раньше было. Как обычно, хотели сделать как лучше, а получилось как всегда... -

Работа сайта и сервера

def_rain ответил admin тема в Новости и обсуждения сайта и форума

Подскажите пожалуйста, как искать по разделам на форуме? Раньше было понятно, заходишь в нужный раздел, в подраздел и нажимаешь в нем поиск. Как сейчас, не понятно... -

Маленький и быстрый вопросик, товарищи. Один вариант решения знаю, но считаю его неподходящим для проекта в целом. Нужно сделать однослойную платку, на которой только выводные компоненты. Т.е. вся топология платы с дорожками и контактными площадками на БОТТоме, а на ТОПе только шелкография. Выводные компоненты из своих библиотек, с пинами заточенными под многослойку. Т.к. у Пинов металлизация сверху и снизу, то в Cross-section невозможно удалить проводящий слой TOP. Получается что сделать полноценный однослойный проект не выходит. Вариант решения есть такой, что бы просто не отдавать в производство Гербера металлизации на ТОПе. Вот я думаю, может есть встроенное в Аллегро решение для таких случаев?

-

Здравствуйте. Есть задача разработать дискретный логический вход с гальванической развязкой. Проблема для меня в очень широком диапазоне напряжения для этого входа: от 20 до 400 В постоянного и переменного 50Гц напряжения. И таких входов 8 штук. Данная задача должна быть реализована на печатной плате, т.е. размеры должны быть как можно компактнее, по возможности. Подобные входа я делал на оптопарах, допустим в случае если на вход предполагается подавать как постоянное, так и переменное напряжение, то есть смысл использовать оптопару TLP182. Однако в случае если входной сигнал будет по верхней границе диапазона (400М AC DС), то токоограничивающий резистор по входу оптопары должен быть мощным, т.е. внушительного размера, чтобы избежать сильного нагрева. Поэтому я задумался, какие есть еще альтернативные варианты решения для таких входов? Поделитесь пожалуйста мыслями по этому поводу. Спасибо.