yuravg

Свой-

Постов

63 -

Зарегистрирован

-

Посещение

-

И снова про Reset

yuravg ответил Flip-fl0p тема в Языки проектирования на ПЛИС (FPGA)

Да, в пределах клокового домена, как любой другой синхронизированный сигнал -

И снова про Reset

yuravg ответил Flip-fl0p тема в Языки проектирования на ПЛИС (FPGA)

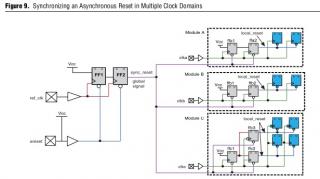

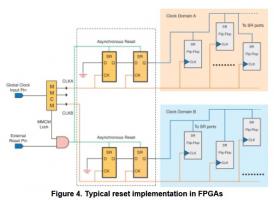

Я не вижу разницы (кроме уровня) (из an545.pdf) Оформите это как отдельный модуль и используйте в каждом модуле где требуется пересинхронизация сброса -

Не работает проект

yuravg ответил go2winner тема в Языки проектирования на ПЛИС (FPGA)

Причиной может бить использование защелки вместо тригера -

Спасибо В общих чертах задача такая: переносное устройство подключается на время <5сек, входной поток 800Mbps собирается, обрабатывается и выдается по ethernet и оптике (уже работающая часть). В новую версию девайса надо добавить передачу по wifi (не медленнее 802.11ac 867, где можно полагаться на скорость передачи данных 433) . Поскольку сборкой, обработкой в выдачей занимаются плис(ы), то хотел wifi (совершенно мне не знакомую часть) поместить в плис. По этому и написал в уже поднятую тему 'wifi на плис' (автора темы интересовала также реализация для адаптера, а не только роутра). Сейчас пробую понять во что выливается софт собственного адаптера в плис, например с tusb1310a или возможность использования CYUSB301X и т.п. Подскажите подобные решения на процессоре и свободный софт. Возможно оптимальный для меня вариант -это процессор с wlan на борту, типа BCM4356, а Combo Module Sterling-LWB5 выглядит вообще привлекательно(в нем правда только 433Mbps), но не понятно как к этому подступиться.

-

в предыдущем посте я задал конкретные вопросы, знаете что ответить/поправить - прошу, а флудить незачем

-

Хотелось бы содержательного ответа, о шагах которые нужно пройти К примеру идем intel вижу интерфейсы usb, pice (sdio), берем например Wireless-AC 8265, как его подключить? какие есть ip для работы с ним, и есть ли они. Или надо покупать ip c pcie и самому писать инициализацию (документация на Wireless-AC 8265 покупается отдельно?) и т.п. Можно ссылочку

-

Тема для меня новая, и правильно сформулировать вопрос не могу, а Ваша подсказка не имеет ни какого отношения к теме fpga + wifi ни моему вопросу. За minipcie, спасибо

-

Дайте пожалуйста ссылок на примеры, или описание в общих чертах, что такое "настройки софта". А вообще, хотелось бы оценить, что потребуется для создания клиента с wifi не хуже IEEE 802.11ac

-

переписать в виде localparam f2 = int' ((2**(coeff_dw - 2))*123/1000);

-

Скрипты

yuravg ответил Faton_11 тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Установите интерпретатор tcl - Activetcl и запускайте с помощью tclsh (или wish для gui) -

поддерживаю вот например разбираясь с OrCAD_Capture_TclTk_Extensions.pdf (SPB_xx\tools\capture\tclscripts\) отсутствие хелпа по командам, усложняет написание расширений (вернее я забросил эту попытку совсем). Подскажите все-таки что-нибудь про команды (например команда alias, без аргументов, открывает окно funkeys, мелочь а приятно :rolleyes: )

-

Модуль SPI и Signal Tap

yuravg ответил sonycman тема в Среды разработки - обсуждаем САПРы

Кстати, убедитесь, что стробирован rst, из приведенного кода это не ясно. -

Поищите по словам: Parameterized Interfaces and Reusable VIP (part1 part2 part3) Вам надо будет переписать driver и sequencer, а формирование сигналов помещается в интерфейс. В приведенных примерах реализация без burst, но добавить его не сложно. В результате получите универсальный компонент для разной ширины адреса, данных, burst (я делал такой для avalon)

-

Модуль SPI и Signal Tap

yuravg ответил sonycman тема в Среды разработки - обсуждаем САПРы

На мой взгляд код написан грамотно, даже через чур (ситраксис "posedge clk, posedge rst", 1'b0, выравнивание и т.д.). Отдельные always или общий always для разных регистров - никак не влияет на работу Проблема может быть в самом подключении signaltap, посмотрите в timequest, до и после подключения signaltap, может увидите проблему(если timequest используется) -

Settings/Analysis & Syntesis/More Analysis там галки Removes redundant LCELL и Registers в положение Off