-

Постов

217 -

Зарегистрирован

-

Посещение

Весь контент Kostochkin

-

SGPIO Master Interrupt

Kostochkin опубликовал тема в Форумы по интерфейсам

Здравствуйте. Веду разработку SGPIO Master. Вопрос по прерываниям. У SGPIO Master есть регистры которые он получает по шине APB от APB Master. В регистрах есть настройки прерываний. Как я понял прерывание записывается в статусный регистр, и говорит о том, что данные от устройства получены. Мне не понятно следующее: 1. Регистры настройки прерываний. Можно настроить прерывание по переднему или заднему фронту, или по уровню сигнала. Вопрос по уровню(фронту/спаду) какого сигнала настраивается прерывание? 2. Регистр Маски прерываний. Как я понял тоже относится к прерыванию, как работать с этой маской ? Если данные на приеме изменились, то прерывание? 3. Статусный регистр. Туда надо записать, что прерывание произошло, пишем "0", чтобы отчистить этот флаг прерывания мастер шины APB туда же должен записать "1". Верно? Благодарю. -

Здравствуйте.

Я - разработчик FPGA, Москва.

Меня заинтересовало предложение о работе "FPGA Developer, Copenhagen, DK".

Что нужно делать? Послать резюме работодателю на почту? Или через вас?

Какой уровень английского требуется? Свободный разговорный?

Благодарю.

-

Благодарю.

-

Нет, допустим есть файл sdc c распиновкой, на этапе синтеза пины не проверяются. Мне надо, чтобы этот файл анализировался только на этапе имплементации. Если что-то изменить, то не надо заново делать синтез, а только имплементацию. Благодарю.

-

quartus 17.1 файл sdc

Kostochkin опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Использую quartus 17.1. Как в quartus файл констрейнов sdc исключить из синтеза? Благодарю. -

Благодарю.

-

Здравствуйте. Я работаю в основном в Vivado. У меня такой вопрос, есть ли в Quartus аналог (* use_dsp48 = "yes" *) как в Vivado? Если есть, то как записывается? Если нет, то как в RTL прописать использование dsp в quartus? Благодарю.

-

Вот пример `timescale 1ns / 1ps package pack_rx; typedef struct packed { logic [31:0] m0; logic [15:0] m1; logic [7:0] m2;} STR_A; endpackage : pack_rx module rx_t import pack_rx::STR_A; #() ( input logic clk, input logic data_vd, input logic [15:0] data, output logic data_out ); STR_A STR_PAR; logic [7:0] state; logic r_data_out; initial begin r_data_out = 1'b0; state = 0; end always @(posedge clk) begin if (data_vd) begin state <= state + 1; case (state) 2:begin STR_PAR.m0[31:16] <= data; end 3:begin STR_PAR.m0[15:0] <= data; end 4:begin STR_PAR.m1 <= data; end 8:begin STR_PAR.m2 <= data[15:8]; end default:; endcase end else begin if ((STR_PAR.m0 == 32'h00001100) & (STR_PAR.m2 == 8'h05)) r_data_out <= 1'b1; else r_data_out <= 1'b0; end end assign data_out = r_data_out; endmodule

-

systemverilog structure

Kostochkin опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте. В модуле на systemverilog есть структура, объявленная в package: typedef struct packed { logic wen_fifo; logic [31:0] data_fifo_in; logic rd_fifo; logic [31:0] data_fifo_out; logic afull; logic fempty; logic wen_queue; logic rd_queue; logic qempty;} STR_FIFO; В симуляции все работает. В quartus 17.1 в signaltap я вижу, что структура почему-то не заполняется, хотя fsm отрабатывает верно, и ничего не оптимизированно. На systemverilog пишу недавно. Может я что-то упустил. Благодарю. -

TCP сессия

Kostochkin опубликовал тема в Форумы по интерфейсам

Здравствуйте. Такой вопрос, 1. Как понять, что два пакета относятся к одной tcp сессии? У них должны совпадать ip адреса источника и отправителя и должны совпадать порты источника и отправителя? Этого достаточно? 2. Как формировать поле Sequence Number (SN) в пакете tcp? SN - стартовый номер + кол-во всех посланных tcp байт в сессии. Значит надо взять Sequence Number от предыдущего посланного пакета и прибавить к нему tcp payload от предыдущего посланного пакета? Благодарю. -

vivado xilinxd

Kostochkin ответил Kostochkin тема в Среды разработки - обсуждаем САПРы

Благодарю -

vivado xilinxd

Kostochkin опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Подскажите, где в vivado посмотреть daemon xilinxd какого-нибудь ip-core ? Благодарю. -

OFDM передатчик, принцип работы

Kostochkin ответил Kostochkin тема в Алгоритмы ЦОС (DSP)

Благодарю всех за ответы. -

OFDM передатчик, принцип работы

Kostochkin ответил Kostochkin тема в Алгоритмы ЦОС (DSP)

Хорошо, если у меня битовый поток на входе с частотой 1МГц, 64 выборки, значит длина символа равна 64 мкс? Какая тогда будет частота несущего колебания? как ее подобрать или рассчитать? -

OFDM передатчик, принцип работы

Kostochkin ответил Kostochkin тема в Алгоритмы ЦОС (DSP)

Благодарю. А почему часть DDS лишняя? Выполняется в аналоговом тракте? И всё же хочу еще спросить. Длина одно символа равна целому числу периодов синусоиды или косинусоиды. А какое число периодов лучше брать за один символ? 1? -

OFDM передатчик, принцип работы

Kostochkin опубликовал тема в Алгоритмы ЦОС (DSP)

Здравствуйте. Я новичок в теме ЦОС. Но мне интересна данная тема. Хотел бы спросить знающих людей по поводу работы передатчика OFDM, без использования блоков коррекции ошибок. Передатчик состоит из модуля serial-to-parallel, допустим 16QAM, IFFT, допустим на 64 точки, DDS, два умножителя и сумматор. Преобразуем 1битный поток в 4битный поток с частотой в 4 раза ниже. 16QAM согласно сигнальному созвездию преобразует 4бита в пару числел I, Q значения которых могут быть: -3/-1/1/3. Далее накапливаем 64 пары чисел I, Q и подаём их на модуль IFFT и на выходе тоже имеем 64 пары чисел I, Q. Теперь последовательно одно за другим эти пары чисел умножаем на сгенерированный в DDS синус и косинус. Частота sin и cos должна быть намного ниже, чем частота битового потока на входе в передатчик (эта частота рассчитывается). На выходе имеем последовательно 64 значения (Q*sin + I*cos). Так же нужен защитный интервал перед каждым символом, длиной 1/8 или 1/16 от длины символа. Это конец каждого символа, например 1/8 от длины, копируется и вставляется в начало символа. В приёмнике защитный интервал отбрасывается. Если что не правильно, прошу поправить. Вопрос такой, а какие поворачивающие коэффициенты надо брать для блока IFFT? И какой размерности числа I, Q надо подавать на модуль IFFT? Надо ли перед подачей чисел I, Q на модуль IFFT умножать их на коэффициент для 16QAM c = (1/√ 10)? Благодарю. -

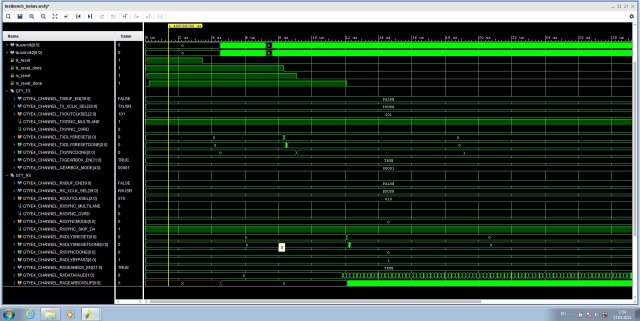

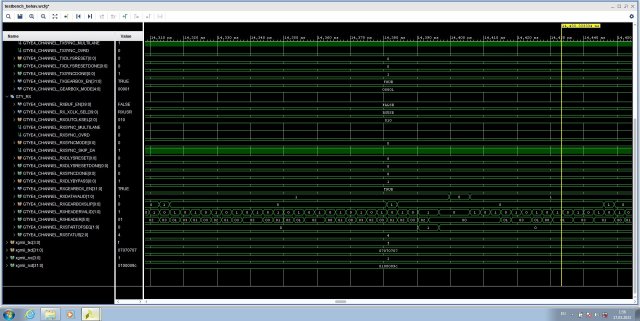

Здравствуйте. Xilinx, US+. Есть ядро PCS 10Gbase-r 32бита для трансивера PHY. В симуляции в vivado 2018.2 работает, выход трансивера замыкаю на вход, получаю на шине RX xgmii пакеты, посланные с TX xgmii. Теперь перегенерировал трансивер и установил байпасс TX и RX вместо эластичных буферов и соответственно синхронные gearbox, синхронизация в автоматическом режиме. Сделал стейт машину bitslip для RX как указано в мануале. Клоки rxuserclk и rxuserclk2 подключил к txuserclk и txuserclk2, установил TX master bypass, RX - slave bypass, установил параметры, как указано в мануале. После того как пришел tx_reset_done дожидаюсь поднятия GTYE4_CHANNEL_TXSYNCDONE. Следом опускаю rx_reset, жду rx_reset_done, начинается синхронизация по bitslip. Но в симуляции выравнивание через bitslip не происходит, постоянно сыпятся неверные преамбулы. Функцию битслип делаю так: если пришла верная преамбула, инкрементирую счетчик верных преамбул, если пришла неверная преамбула, сбрасываю счетчик верных преамбул, поднимаю GTYE4_CHANNEL_RXGEARBOXSLIP на один такт, жду 16 тактов и всё заново. Синхронизация при достижении счетчиком верных преамбул 64. Но этого не происходит. Где-то какой-то рассинхрон. Может кто этим занимался, подскажите что я упустил? Прилагаю картинки. Благодарю.

-

Здравствуйте. Xilinx, US+. Есть ядро PCS 10Gbase-r 32бита для трансивера PHY. В симуляции в vivado 2018.2 работает, выход трансивера замыкаю на вход, получаю на шине RX xgmii пакеты, посланные с TX xgmii. Теперь перегенерировал трансивер и установил байпасс TX и RX вместо эластичных буферов и соответственно синхронные gearbox, синхронизация в автоматическом режиме. Сделал стейт машину bypass для TX и bitslip для RX как указано в мануале. Клоки rxuserclk и rxuserclk2 подключил к txuserclk и txuserclk2, установил TX master bypass, RX - slave bypass, установил параметры, как указано в мануале. После того как пришел tx_reset_done дожидаюсь поднятия GTYE4_CHANNEL_TXSYNCDONE. Следом опускаю rx_reset, жду rx_reset_done, начинается синхронизация по bitslip. Но в симуляции выравнивание через bitslip не происходит, постоянно сыпятся неверные преамбулы. Функцию битслип делаю так: если пришла верная преамбула, инкрементирую счетчик верных преамбул, если пришла неверная преамбула, сбрасываю счетчик верных преамбул, поднимаю GTYE4_CHANNEL_RXGEARBOXSLIP на один такт, жду 16 тактов и всё заново. Синхронизация при достижении счетчиком верных преамбул 64. Но этого не происходит. Где-то какой-то рассинхнон. Может кто этим занимался, подскажите что я упустил? Прилагаю картинки. Благодарю.

-

Благодарю вас за ответы.

-

Благодарю.

-

Да, точно, такого сигнала нет, перепутал. Значит, надо просто дождаться правильной преамбулы какое-то время (я думаю тактов 12-16), и если она не пришла, то опять поднять bitslip. Благодарю.

-

xilinx 10G baser функция bitslip

Kostochkin опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Есть вопрос по поводу реализации функции bitslip трансивера GTY для 10G baser, кодировка 64/66. При принятии неправильной преамбулы 66-битного слова (2'b11 или 2'b00) надо поднять на 1 такт сигнал bitslip = 1'b1, для того чтобы чуть задержать десериалайзер. Получить от трансивера slipdone. Вопрос а сколько минимум нужно держать паузу(в тактах) между получением slipdone и поднятием bitslip? Или можно сразу поднимать bitslip после slipdone, если опять на приёмнике есть неправильная преамбула? Благодарю. -

Благодарю за ответ. А вот если стоит задача сделать dpll, с допустим системной частотой 1ГГц, входной частотой от 1 до 100МГц, и выходной частотой от 1 до 100МГц, входная и выходная частота заданы как параметры. Желательно с минимальным джиттером. Можно сделать dpll на HDL по описанию, которое вы дали(фазовый детектор на D триггере и ДПКД), или есть более лучшее решение? Если есть, то какие, если не секрет? Благодарю. И второй вопрос, везде на схемах DPLL после ФД рисуют LOOP FILTER, фильтр НЧ(например FIR). Я не очень понял, принцип действия фильтра, ведь сигнал у нас однобитный..? Благодарю.

-

Здравствуйте, меня заинтересовала данная тема. Вы пишите, что фазовый детектор с "окном синхронизации" при совпадения фронтов 2.048MHz внутри окна коэф. делителя 42+43+43, но они же не всегда будут совпадать, а во время не совпадения какие? 42+42+43 и 43+43+43? тогда всё равно теряется точность. Или я не правильно понял. Благодарю.

-

Благодарю