-

Постов

217 -

Зарегистрирован

-

Посещение

Весь контент Kostochkin

-

И еще вопрос, можно ли в quartus(у меня 18.1) сгенерировать библиотеки для симулятора active-hdl? Если да, то как? Благодарю.

-

Благодарю. Что такое CDR - я понимаю. И все равно не понимаю, откуда взять reference clock для CDR.

-

srtatix10 transceiver

Kostochkin опубликовал тема в Работаем с ПЛИС, области применения, выбор

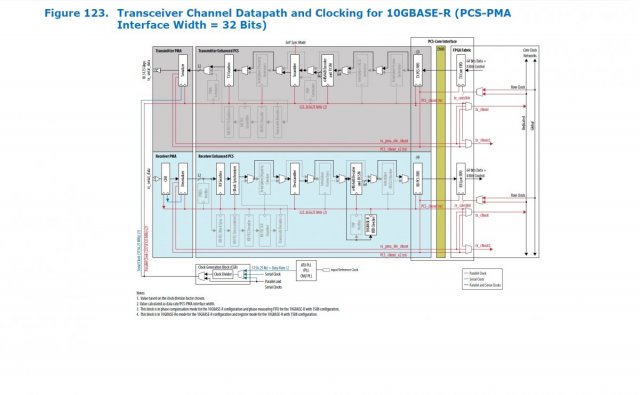

Здравствуйте. Пытаюсь на stratix10 cделать ядро 10g base-r. Для начала сгенерировал трансивер для 10g-base-r, сгенерировал ATX PLL, сгенерировал reset controller. ATX PLL выдает один клок - tx_serial_clk0(5156.25МГц) для трансивера. Мне не понятно откуда мне притянуть в трансивер следующие клоки: 1: rx_cdr_refclk0 (644.53125МГц) - это отдельный пин, или надо ставить pll, или вытащить откуда-то? 2: tx_coreclkin (156.25МГц) и rx_coreclkin (156.25МГц) - эти клоки надо сделать из tx_clkout и rx_clkout, только не пойму как правильно это сделать, через pll? Подскажите пожалуйста, с альтерой раньше не работал. Благодарю. -

На готовом 10gbase-r я уже подымал ethernet, только на xilinx.

-

И еще как лучше моделировать такие вещи? В quartus есть встроенный симулятор? или надо пользоваться modelsim? Если да, то для modelsim надо в quartus сгенерировать библиотеки, правильно я понимаю? Благодарю.

-

Так я и спрашиваю, может есть каие-то примеры или что-то похожее, чтобы ускорить разработку..

-

Да, написать свое ядро 10gbase-r для aria 10.

-

altera 10G трансивер

Kostochkin опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Стоит задача написать свое ядро для 10G трансивера на aria 10 для работы с ethernet. Я работаю с xilinx, поэтому спрашиваю. Вот документ: "Intel® Arria® 10 Transceiver PHY User Guide" - как я понял это описание трансивера. Этого документа хватит, или стоит еще какие-нибудь полезные доки почитать? Если да, то какие? Благодарю. -

Благодарю.

-

В этой статье проект на плис пишется на python и верифицируется на python. А меня интересует как готовый проект на HDL верифицировать на python.

-

python + FPGA

Kostochkin опубликовал тема в Вопросы системного уровня проектирования

Здравствуйте. У меня такой вопрос : Как верифицировать verilog проект для плис, используя python? Написать тестбенч на python и подключить к нему все файлы verilog? Или в python создается только файл (txt например) входных воздействий, и его надо подключить к тестбенчу в modelsim? Если так, то как проверить результат моделирования при помощи python? Или в python пишется и проверяется testbench, конвертируется в verilog и используется в modelsim? Благодарю. -

Разработка проектов FPGA

Kostochkin ответил Kostochkin тема в Ищу работу

Актуально, также готов работать с lattice. -

Lattice Diamond

Kostochkin ответил Kostochkin тема в Среды разработки - обсуждаем САПРы

Благодарю. -

Lattice Diamond

Kostochkin ответил Kostochkin тема в Среды разработки - обсуждаем САПРы

Вы хотите сказать, что в файле констрейнов устанавливаешь дифференциальный тип для пары, а в проекте использовать положительный пин? -

Lattice Diamond

Kostochkin опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте, с lattice работаю в первый раз. У меня стоит Diamond 3.11. Мне нужен дифференциальный входной буфер. Никак не могу найти. Есть IB - обычный входной буфер, а мне нужен дифференциальный. Как он называется? и где можно посмотреть примеры примитивов? Благодарю. -

Active-HDL 10.5

Kostochkin ответил Kostochkin тема в Среды разработки - обсуждаем САПРы

Попробовал, на другой машине, все работает. Какие-то проблемы в операционной системе наверно. Всех благодарю. -

Active-HDL 10.5

Kostochkin ответил Kostochkin тема в Среды разработки - обсуждаем САПРы

Прочитал. Я понял, что Active-HDL Lattice Edition должен работать по лицензии от Lattice Diamond, которую я скачал с сайта lattice. Diamond работает на этой лицензии, но при запуске Active-HDL Lattice Edition требует лицензию и не запускается. -

Active-HDL 10.5

Kostochkin опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Установил lattice diamond 3.11. В него входит active-hdl 10.5, но без лицензии. Подскажите как быть? Благодарю. -

Благодарю.

-

ПЛИС LATTICE

Kostochkin опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. С плис lattice никогда не работал. Но возможно предстоит. Как я понял, среду разработки можно скачать бесплатно с их сайта. Вопрос1: есть ли в lattice примитивы аналоги xilinx IODELAY и IOBUFDS ? Если есть, то где можно скачать pdf с их описанием? или хотя бы их названия.. Вопрос2: есть ли в среде разработки lattice аналог xilinx chip scope? Если есть, то как называется? Благодарю. -

Благодарю.

-

Здравствуйте. Как в verilog приравнять все биты регистра переменной длины к 1 ? Есть вариант без for? В vhdl так : a <= (others => '1');

-

Благодарю.

-

20 точек на период меня устраивает, пока. И решение Accum <= Accum + 89128 + 42 * Freq_Data - тоже, только мне надо более точно задавать частоту синусоиды. Правильно ли я понимаю, что для этого мне надо увеличить размерность аккумулятора? Благодарю.

-

Зачем 14-16 бит фазы? А где взять такую таблицу от 4000 до 16000 значений? Благодарю