-

Постов

217 -

Зарегистрирован

-

Посещение

Весь контент Kostochkin

-

System verilog двумерный массив

Kostochkin опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте. Подскажите, пытаюсь сделать pipeline, logic [(DATA_WIDTH-1):0] r_data_pipeline [(TAPS-1):0]; logic [(DATA_WIDTH-1):0] data_in; always @(posedge clk) begin r_data_pipeline <= '{TAPS{r_data_pipeline[(TAPS-2):0],(data_in)}}; end но компилятор Aldec выдает ошибку: Error: VCP2852 sv/fir_filter.sv : (68, 1): Incompatible types at assignment: .r_data_pipeline[$left(r_data_pipeline,1)-0*$increment(r_data_pipeline,1)]<logic[DATA_WIDTH-1:0]> <- r_data_pipeline[TAPS-2:0]<logic[DATA_WIDTH-1:0]$[TAPS-2:0]>. Подскажите, как правильно записать? Благодарю. -

Благодарю всех. Буду проверять

-

Благодарю. Я толкаю 0х07070707 и пакет раз в секунду. Вопрос такой. Нужно включать режим test pattern generation? Когда включать? Или это не обязательно?

-

Да, udp пакет(64 байта), примерно раз в секунду

-

Здравствуйте. vivado 2018.2. Имеется плата с плис xcvu9p. Есть порт SFP+. В плис собираю ядро 10G/25G Ethernet Subsystem v2.4 в режиме 10G pcs/pma 32 bits. При моделировании в vivado все прекрасно работает при замыкании дифф пары tx на rx. В железе при замыкании в SFP+ tx на rx не работает, на приеме xgmii: xgmii_rxc = 0x1; xgmii_rxd = 0x0100009C; Также: user_rx_reset = 1; user_tx_reset = 1; stat_rx_local_fault = 1; stat_tx_local_fault = 1; Сингалы user_rx_reset и user_tx_reset приходят от самого трансивера. Сингалы stat_rx_local_fault и stat_еx_local_fault приходят от софтовой части IP core. sys_reset держу в 1 примерно через 16мкс, потом сбрасываю в ноль. Может кто работал с этим ядром? Благодарю.

-

Благодарю всех.

-

Да, ты прав..

-

Ethernet Преамбула

Kostochkin опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Здравствуйте. Меня интересует вопрос об ethernet преамбуле. Стандартная преамбула 0x55_55_55_55_55_55_55_D5, длина 8 байт. Если я буду генерировать пакеты с длиной преамбулы не 8, а 7 байт: 0x55_55_55_55_55_55_D5, это будет критично для стандартного приемника, или нет? Можно ли так делать для передачи пакетов по сети? Благодарю. -

Схема программатора xilinx

Kostochkin опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Где можно найти схему программатора xilinx platform cable usb II, DLC10 ? Пытаюсь починить. 5В с usb есть, компьютер программатор видит. Но нет питания 1.2В и 1.8В на плисе sp3. Наверно сгорел стабилизатор. Может у кого-нибудь есть принципиальная электрическая схема этого программатора. Благодарю. -

Благодарю, как я понял этот мост соединяет различные hard части кристалла. Благодарю, наверно вы правы.

-

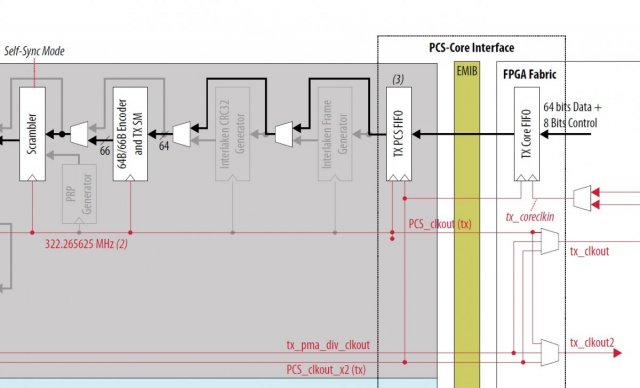

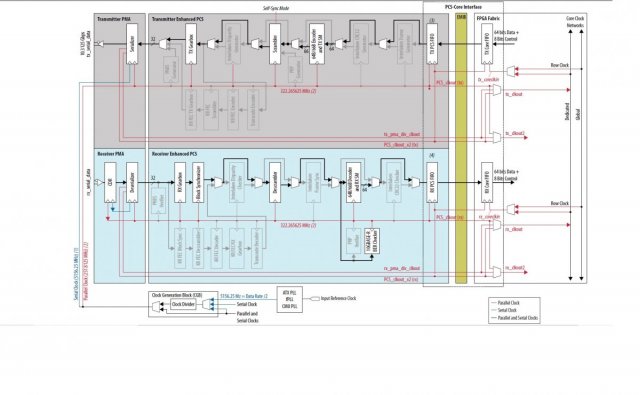

На схеме два фифо, TX CORE FIFO и TX PCS FIFO, клок xgmii 156.25МГц и данные xgmii входят в TX CORE FIFO. Из TX PCS FIFO выходят данные 32бита на частоте 322.265625МГц. А между этими фифо данные передаются на удвоенной частоте PCS_clkout_x2 = 644.53125МГц. Там стоит мост EMIB. Так и должно быть? 156.25МГц -> 644.53125МГц -> 322.265625МГц. Мне это не понятно. И что такое этот мост EMIB? Благодарю.

-

Нет на 32, получается PCS_clkout = 322.265625МГц, PCS_clkout_x2 = 644.53125МГц. Не понятно тактование tx_pcs_fifo и rx_pcs_fifo, со стороны PCS эти fifo тактируется 322МГц, а со стороны user logic 644МГц... Согласно схеме. Как-то странно, или я что-то не понимаю.

-

Здравствуйте. Вопрос такой. Вот схема ip-core 10gbase-r для stratix10. Меня интересует частота клока PCS_clkout_x2(tx) и PCS_clkout_x2(rx). Нигде не могу найти. Подозреваю, что частота такая же как и у PCS_clkout(tx) = PCS_clkout(rx) = 322.265625МГц. Но хотелось бы знать точно. Вроде разобрался, PCS_clkout_x2 =PCS_clkout *2 = 644МГц. Но тогда не понятно тактование tx_pcs_fifo и rx_pcs_fifo, со стороны PCS эти fifo тактируется 322МГц, а со стороны user logic 644МГц... Может в схеме опечатка и user logic этих fifo тактируется от tx_pma_div_clkout, rx_pma_div_clkout... Как я понял (tx/rx)pma_div_clkout = 156.25МГц при 10gbase-r. Благодарю.

-

Я делал так: асинхронный регистр -> синхронный регистр -> функция грея -> синхронный регистр. Здесь я имел в виду последний регистр.

-

Можно через 2, хуже не будет:)

-

Если честно, не смотрел ваш код, работаю на VHDL, но у меня была такая же проблема. После принятия счетчика байт через функцию Грея в другом клоковом домене, надо этот счетчик пропустить через триггер, а потом использовать.

-

Благодарю. Для stratix10 есть корка 10g base-r low latency. Исходники не посмотришь, все закрыто, но наверно это то, что нужно для начала. Пойду по простому пути, для начала. Если не устроит, тогда надо будет генерить корку в режиме PCS Direct, и писать PCS самому.

-

Конкретно меня интересует latency. Чтоб была как можно меньше.

-

Благодарю. Получается, что в startix10 уровень PCS не soft, а hard? Я думал он soft. Значит, если я напишу свой soft PCS, он шустрей, чем готовый hard работать никак не будет, верно?

-

Из PCS выходит xgmii. Мне нужен свой собственный уровень PCS. Соответственно для этого мне нужно сгенерировать трансивер 10g base-r без PCS.

-

А как в quartus сгенерировать голый трансивер в режиме 10G base-r? Для stratix10. Я имею в виду трансивер 10G base-r только PMA уровень, без уровня PCS. Я делаю так : ip catalog -> transciever phy -> l-lite/h-lite transceiver phy intel srtatix10 fpga ip. Здесь можно выбрать настройки, но в сгенерированном ядре присутствует уровень PCS, а мне надо сгенерировать без него, только PMA. Если был бы открытый код еще ладно, но pcs полностью закрыт. Подскажите, благодарю.

-

Благодарю всех.

-

Опять вопрос. Есть плата со stratix10 и qsfp28. Надо реализовать 10g-base-r. Как это физически сделать? Как я это понимаю: Вместо qsfp28 вставить sfp+ b и использовать одну диф. пару вместо 4. В трансивере надо указать какую именно диф. пару я использую. Правильно? Благодарю.

-

Благодарю, нашел. Благодарю.

-

Да есть, благодарю.