Drumbl

-

Постов

19 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Drumbl

-

-

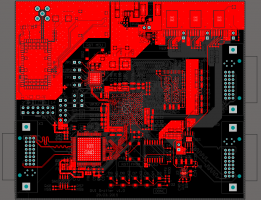

Всем спасибо! Учел ваши замечания по поводу термобарьеров и глухих отверстий, убрал, но не везде! =))) Плату отправили в производство посмотрим что они ответят!

-

а где-то термобарьеры вообще противопоказаны. например на sma.

Не знаю я подключил SMA разъем, как пишут в камасутре на 3G модуль. И там есть термобарьеры, у модуля своя отдельная земля соединяется в одной точке с общей.

Производство выбрать не могу, производство в Европе! Попробую узнать про глухие отверстия! Но надеюсь делаю!

Еще вопрос как обозначить на каких проводниках нужно выполнить конроль импеданса?

-

Ох уж эти любители термобарьеров

- ладно бы еще термобарьеры были хорошие, так же нет. Узнаю элементы "знакомых" библиотек которые наверно есть "почти у всех"- скопированные без оценок и критики.

- ладно бы еще термобарьеры были хорошие, так же нет. Узнаю элементы "знакомых" библиотек которые наверно есть "почти у всех"- скопированные без оценок и критики.Что не так с термобарьерами?

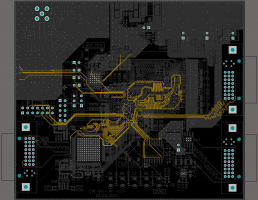

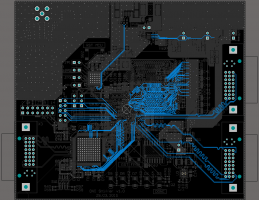

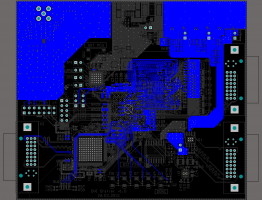

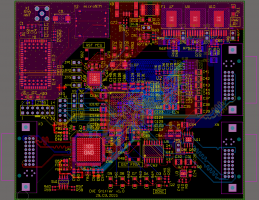

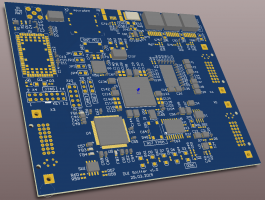

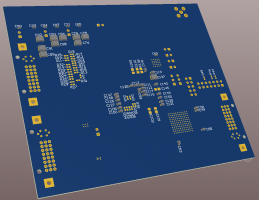

Что-то мне кажется память чрезмерно "затянута" и не оптимальна. Верхний слой вообще не использован, зато на остальных сплошные петли... Ну и как обычно - наверное здесь хватило бы и 6-ти слоев, но не видя питаний трудно это утверждать.По поводу слоев! Производство на котором будет изготавливается ПП делает толстый препрег для 6 слоев, с толстыми диэлектриками дороги выходили по 0.4мм, поэтому было решено взять 8 слоев.

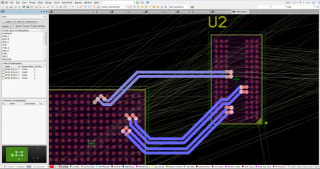

Да согласен длинновато вышло! Выравнивал по мануалу от Xilinx учитывая задержки в ПЛИСине и задержки с которыми должны приходить сигналы в память. И опять же длинные дороги получились из-за толстых диэлектриков, площадь больше занимают. Хотя может я что то не так понимаю.

В таком масштабе все равно ничего понять нельзя, тем более что Вы не показали слоев земли и питания и общую структуру платы.Что касается глухих отверстий:

- каждый тип надо вывести отдельным файлом DRILL

с описанием - с какого и на какой слой.

Формат лучше всего миллиметровый 4:4

Правда, я не очень понял, зачем Вам глухие отверстия в этом дизайне?

Там что, есть BGA с шагом менее 0.8 мм?

Да, скрины ужасные, не знаю как в альтуме вывести jpg, если знаете подскажите, или другой способ подскажите. Выведу.

В слоях питания вообще ни чего не разобрать, поэтому не скинул. Под высокоскоростными цепями лежат сплошные земля и питание. Все проводники DDR под питанием и землей, разрывов нет, так же и под дифф. парами.

Глухих отверстий мало, глухие отверстия это плохо? DDR шаг 0.8, это критично?

По поводу формата я так и думал,эээээххх придется помучиться!

Всем спасибо!

-

-

Kaligooola, спасибо!

bigor, что за программа в которой рассчитывались дорожки и стек? Где взять? Хочу такую же!

:rolleyes:

:rolleyes: -

По количеству слоев требуемой платы можно грубо так прикинуть: берем от края количество сплошных рядов шаров по периметру (без учета разделительного ряда, по центру иногда есть разделение обычно для питания) и прибавляем 2. Например 6 рядов шаров + 2 получаем 8-слойку. А далее смотрим, позволяет ли схема, идеология сократить это кол-во слоев. Иногда можно сократить на 1 ... 3 слоя, но это редкость. Начинаем разводить из центра чипа, обычно это питание, земли и далее к крайним рядам.

Это все здорово, но у меня есть дифф пары на ddr3, поэтому я думаю разводку лучше начать с них. И вообще сначала память развести, а потом остальное. И главное сейчас с импедансом разобраться.

-

Опубликовано · Изменено пользователем Drumbl · Пожаловаться

Значит нужно менять производителя печатных плат? Мои данные верны?

-

Приведите параметры, которые в Сатурн забиваете. Вообще, трассировка DDR3 - это отдельная большая тема. И по ней куча аппноутов.

Начните с этого:

http://www.fujitsu.com/us/Images/SPBG_GDC_..._en_r2.0_AN.pdf

Спасибо почитаю!

Данные для Saturn (Conductor Impedance): W=0.46mm, H=0.22mm, Er=4.2, BCW=18um, PT=35um, PC=Microstrip

-

Опубликовано · Изменено пользователем Drumbl · Пожаловаться

-

Нужно конечно. Там частоты уже от 1 до 2+ ГГц, без импедансов никуда. Плюс остальные ограничения в топологии - fly-by, длины/задержки, ограничения в свапе данных...

Достаточно рассчитать или нужен и расчет и контроль импеданса? В чем суть fly-by и что такое свап данных, это тоже обязательно?

-

Вопросы: Нужно ли соблюдать импеданс(Characteristic impedance) для DDR3? Нужно ли его контролировать или достаточно рассчитать?

-

Опубликовано · Изменено пользователем Drumbl · Пожаловаться

Ещё раз! =))) Читал на форумах что Altium может расчитывать дорожки по заданному волновому сопротивлению или это бред? Илия что то не так понял! Я этим САПРом 2 дня пользуюсь, естественно всех тонкостей не знаю!

-

Читал что половину из выше сказанного может расчитать Altium! Так ли это?

-

Опубликовано · Изменено пользователем Drumbl · Пожаловаться

Не знаю 256 пинов у ПЛИС которую мы выбрали (возможно заменим на другую), половина из них питание и земли, неужели нужно более 2х или 3х сигнальных слоев?

-

Не надо в слоях земли-питания прокидывать сигнальные трассы. Даже НЧ. Плохо кончится.

Присылайте описвние требований к импедансам, поможем структуру подобрать

и расчет волновых сопротивлений сделать.

Т.е. что нас интересует:

- одиночные проводники - какие варианты импеданса нужны

- дифф.пары - какие варианты импеданса нужны

Пришлите описание конкретного BGA, скинем пример трассировки и определим нужное число сигнальных слоев.

Консультант: Грихин Максим Николаевич

На самом деле хотлось бы самому научиться делать расчеты =)) не поделитесь опытом?

-

Ну в принципе я и думал что минимум на 4 слоях разводить придется, ладно, спасибо! Буду пробовать и читать мануал!

-

Ну нарисовать, развести, какая разница? Дальше в контексте должно быть понятно, что я имел ввиду! Схема пока разрабатывается, будет использоваться ПЛИС из серии Artix7, там пинов около 250-300, не думаю что для этого нужно 10 слоев.

Так мне и не сказали как правильно, раскидывать слои? Можно просто ссылкой в мануал послать!

-

Опубликовано · Изменено пользователем Drumbl · Пожаловаться

Друзья, помогите! Необходимо создать ПП с применением ПЛИС в BGA корпусе + прикрутить к этому память, DVI разъем и 3G модуль!

Вопрос в расположении элементов на плате и правильном разведении печатных проводников. Перечитал уже множество статей по этому вопросу и понял что необходимо как минимум 4 слоя, 1 сигнальный (внешний), 2 земляной (внутр.), 3 питание (внутр.), 4 сигнальный (внеш.).

Тут возникает вопрос еще: т.е. внутренние слои использовать только для земли и питания, и по ним нельзя прокидывать сигнальные линии, или можно, но только НЧ, а ВЧ по внешним слоям?

А если понадобится ещё слой где его лучше расположить?

Раньше не приходилось разрабатывать такие печатные платы надеюсь на помощь!

Блин случайно не там создал тему :krapula: простите! Как можно перенести?

falc56

в ISDN/G.703/E1

Опубликовано · Изменено пользователем Drumbl · Пожаловаться

Всем привет! Подскажите, это последняя версия PEF2256 H Version 2.2 (Rev. 1.1, June 2005)?