Vadim_nsk

Свой-

Постов

226 -

Зарегистрирован

-

Посещение

-

Но у меня вопрос не по теме, но по FPGA. Может лучше отдельный топик создать? Заметил такую вещь. В борде, под которую создан проект стоит чип xc7z020clg400-1, в котором нет сериалайзеров, они ведь только в чипах x15, x30, x45 и т.д. Но по сигналам видно, что применяются сериалайзеры и сигнал восстанавливается по опорной частоте и по 4-м фазам 0, 90, 180, 270 градусов. Я полагал, что в простых FPGA стоят два триггера, работающие по двум фронтам как в 6-м семействе. Я не прав?

-

Ура! Все получилось!

-

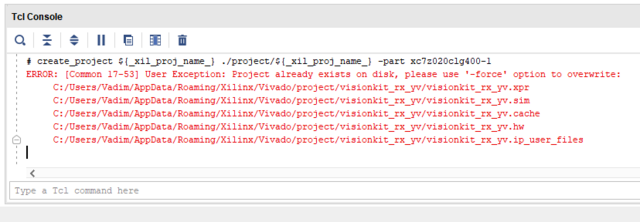

Попробовал из консоли TCL, тоже ничего не выходит: pwd D:/Users/Vadim/Documents/projects/github/CameraLinkVisionKit_microZED/cameralink_rx/project visionkit_rx_prj_yv_v19_1.tcl --help invalid command name "visionkit_rx_prj_yv_v19_1.tcl" Везде статьи о том как писать скрипты на TCL и как запустить скрипт из графического интерфейса без параметров. А как запустить его из консоли или с GUI, но с параметрами не могу найти. Подскажите пожалуйста кто знает...

-

Спасибо, скачал А как правильно указать параметры для запуска скрипта тикля? ну, не нужен мне проект с таким путём Он потом ругаться будет, что не нашел исходники, а ищет он их по относительным путям. Конечно же их нет там, где он создает проект.

-

А в каком документе описан процесс создания и описания проекта на тикле?

-

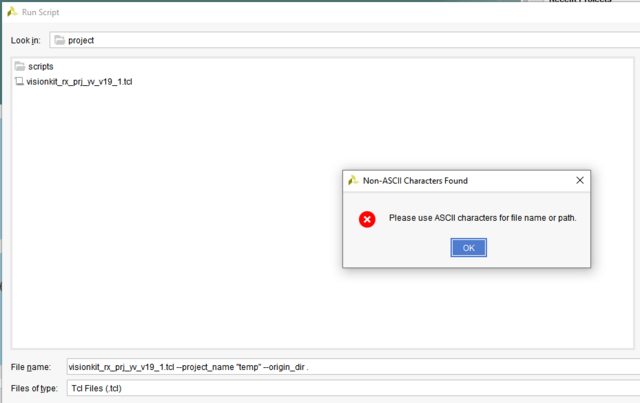

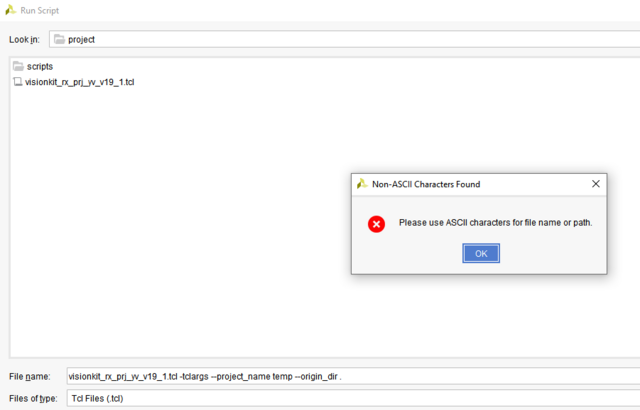

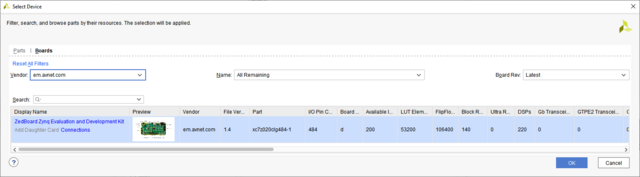

Подскажите пожалуйста как этому товарищу по имени VIVADO указать параметры? Он вроде бы подсказку выводит даже: puts "$script_file -tclargs \[--project_name <name>\]" Но и так не получается Как это правильно написать? Имя проекта задать "temp", а в качестве текущего каталога указать ".". Просто он мне выдает ошибку, что не может найти файл, показывая путь в домашнюю директорию. Хотя это возможно из-за: # set_property -name "board_part_repo_paths" -value "/home/Xilinx/vivado-boards-master" -objects $obj WARNING: [Board 49-91] Board repository path '/home/Xilinx/vivado-boards-master' does not exist, it will not be used to search board files. В самом скрипте я подменил ему название платы и чипа (на ту, что вивада позволяет мне выбрать): create_project ${_xil_proj_name_} ./project/${_xil_proj_name_} -part xc7z020clg484-1 -force set obj [current_project] set_property -name "board_part" -value "EM.AVNET.COM:ZED:PART0:1.4" -objects $obj но вот далее идет: set_property -name "board_part_repo_paths" -value "/home/Xilinx/vivado-boards-master" -objects $obj по идее, раз плата указана имеющаяся у меня в системе, она то должна быть описана. В общем, не понятно пока, как это работает.

-

Переустановил заново VIVADO 2019.1, выбрав все, что он позволил выбрать. Все равно пишет: "ERROR: [Board 49-71] The board_part definition was not found for em.avnet.com:microzed_7020:part0:1.2. The project's board_part property was not set, but the project's part property was set to xc7z020clg400-1. Valid board_part values can be retrieved with the 'get_board_parts' Tcl command. Check if board.repoPaths parameter is set and the board_part is installed from the tcl app store." Т.е. такой платы в стандартной поставке нет?

-

Нет конечно :-) я дитя комфорта, привык к большим вендорам, где все включено. Нетлист генерится в GowinIDE при синтезе?

-

Я хотел модернизировать уже установленную VIVADO, добавив платы. Просит логин и бреет по нему, т.к. санкции. Сейчас качаю полный дистрибутив, чтобы заново поставить offline. Но смущает другое. У меня есть примерно 6 плат в VIVADO 2019, чуть больше в 2022, но помнится их было гораздо больше. А что если такой платы все же не будет?

-

Есть вот такая плата: CameraLink Vision Kit В описании есть ссылка на GitHub на проект для VIVADO 2019.1. Но самого проекта нет, есть только файл TCL. При его запуске, платформа пытается его создать. Но проблема в том, что в моем дистрибутиве нет такой платы и создание проекта завершается ошибкой. Пробовал подсунуть похожую плату, но результат тот же. Как поступают в подобном случае профи, протестующие против размещения в репозитории файлов проекта и использующие TCL, CMAKE и пр.? Я всего-то хотел глянуть что там в этом проекте, но даже файла BD нет, видимо он также создается и на тикле добавляются в него компоненты и описываются связи между ними. Или может есть у кого полный дистрибутив, включая описание данной платы и он согласится просто создать проект и завернуть в архив?

-

Ну, на VHDL я около 19 лет работаю, а с AHDL и VERILOG только начинал знакомство с FPGA 20 лет тому назад. Сейчас уже тяжеловато воспринимается. И все это время работал с ActiveHDL, т.к. Mentor те же годы назад показался крайне недружелюбным. Видимо потому что он под Linux изначально написан, своя специфика интерфейса. Пару лет назад пришлось поработать с Altera (ранее имел дело только с Xilinx), и там был старый квартус 11 + Mentor. Тяжко, но уже более менее рабочий вариант. Если это единственный вариант остаться в рамках VHDL, попробую его. Все проще, чем освоить новый язык. спасибо. Да, так гораздо удобней.

-

Удалось кому-нибудь собрать библиотеку симуляции на VHDL под ActiveHDL. Делаю как описано в: https://www.aldec.com/en/support/resources/documentation/articles/2189 Когда указываю VERILOG-файлы, все собирается, но тогда из VHDL не видны примитивы. Вернее, rPLL почему-то видится, а вот что-то посложнее, вроде FIFO_SC уже не могу подключить, полагая, что такой примитив недоступен для симуляции. Не знаю куда он выливает логи, но ругается примерно так: Ни одного файла на VHDL не удалось добавить в библиотеку... :-( Для rPLL добавил сам файл библиотеки в проект, но для FIFO_SC это не срабатывает Содержание синтезированного файла FIFO_SC.vhd довольно странное для меня, но ничего другого я не вижу: Как симулировать простой проект в ActiveHDL не знаю. А как сделать <code><> в сообщении сжимаемый, чтобы не был таким огромным?

-

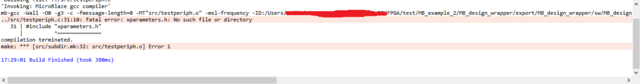

Вот тут нашел ответ на свой вопрос, если кому интересно: https://support.xilinx.com/s/question/0D52E00006jpcvVSAQ/fatal-error-xparametersh-no-such-file-or-directoryxilinx-platform-definition-filexpfm-is-removed-after-building-the-project?language=en_US Зашел в Makefile сгенерированного компонента и внес указанные правки. Было так: COMPILER= ARCHIVER= CP=cp COMPILER_FLAGS= EXTRA_COMPILER_FLAGS= LIB=libxil.a RELEASEDIR=../../../lib INCLUDEDIR=../../../include INCLUDES=-I./. -I${INCLUDEDIR} INCLUDEFILES=*.h LIBSOURCES=*.c OUTS = *.o libs: echo "Compiling myip..." $(COMPILER) $(COMPILER_FLAGS) $(EXTRA_COMPILER_FLAGS) $(INCLUDES) $(LIBSOURCES) $(ARCHIVER) -r ${RELEASEDIR}/${LIB} ${OUTS} make clean include: ${CP} $(INCLUDEFILES) $(INCLUDEDIR) clean: rm -rf ${OUTS} Стало так: COMPILER= ARCHIVER= CP=cp COMPILER_FLAGS= EXTRA_COMPILER_FLAGS= LIB=libxil.a RELEASEDIR=../../../lib INCLUDEDIR=../../../include INCLUDES=-I./. -I${INCLUDEDIR} INCLUDEFILES=*.h LIBSOURCES=$(wildcard *.c) OBJECTS = $(addsuffix .o, $(basename $(wildcard *.c))) ASSEMBLY_OBJECTS = $(addsuffix .o, $(basename $(wildcard *.S))) libs: echo "Compiling simple_adder..." $(COMPILER) $(COMPILER_FLAGS) $(EXTRA_COMPILER_FLAGS) $(INCLUDES) $(LIBSOURCES) $(ARCHIVER) -r ${RELEASEDIR}/${LIB} ${OBJECTS} ${ASSEMBLY_OBJECTS} make clean include: ${CP} $(INCLUDEFILES) $(INCLUDEDIR) clean: rm -rf ${OBJECTS} ${ASSEMBLY_OBJECTS} Файл лежит в: ...\ip_repo\myip_1.0\drivers\myip_v1_0\src\Makefile

-

Снова проблема... Сгенерировал свой ip, все оставил по умолчанию, даже название "myip". Генерируется битстрим, делается экспорт платформы. Но Vitis IDE в упор не видит xparameters.h. Я полагаю, что именно из-за myip, т.к. когда я его удаляю из BD, то все собирается, генерируется на выходе ELF. При этом, он не ругается на содержимое заголовочного файла, а пишет, что не может его найти, хотя он находится в BSP (не знаю как это в новых терминах называется). Захожу в testperiph.c, жму на #include "xparameters.h" и среда в него заходит, т.е. он есть и она его "видит", но: Чтобы зря не тратить ваше время на гадания, сразу приложу архив проекта. Может глянете, у кого есть время? https://drive.google.com/file/d/1o4zL8GqBPubgvcgljmpcYFZbnmoiGITc/view?usp=sharing

-

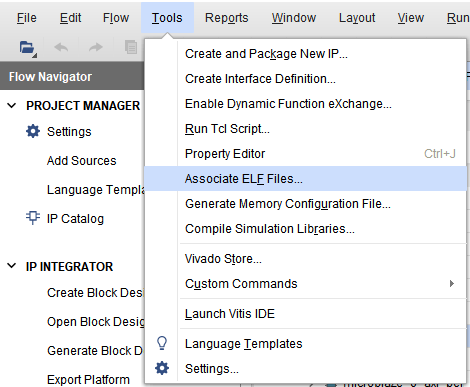

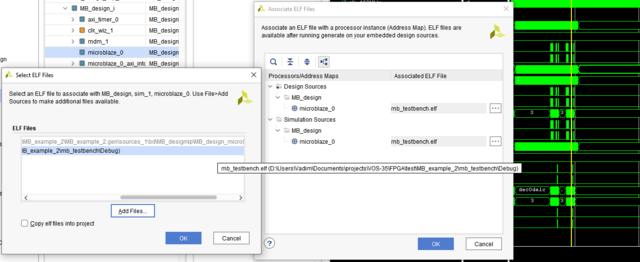

Живое общение творит чудеса. Во-первых, ELF у меня не попадал в симуляцию, т.к. я его просто добавлял в проект, а надо указать в: на фоне видна времянка работы AXI-шины, т.е. работает пример тестирования периферии. Ну и вишенка на торте. copy-past в действии, в приведенном ранее тестбенче глупейшая ошибка, не заменено имя компонента, для которого описывается архитектура тестбенча. И вот вроде бы куча примеров создания проекта, но то ли часть скринов отсутствует ввиду их очевидности, то ли так разнятся версии VIVADO, но делал все по этим примерам, а результат получал отличный от приводимого...