Aleksei_Rostov

-

Постов

313 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Aleksei_Rostov

-

-

Можно

На сколько я знаю, на Xilinx форуме одному человеку таки удалось запустить что то похожее на {raw ethernet without TCP/IP} на XEmacPs_xxx.

Полистав даташит на emacps и dmaps, понял что работа для реализации raw udp сводится к настройке через регистры изернета и дма, а далее операции чтения/записи с помощью sgdma, и контрольные регистры emacps

-

Опубликовано · Изменено пользователем Alexey_Rostov · Пожаловаться

зависит от того насколько полно вы хотите поддержать стэк.нужны ли вам DHCP, ARP, Ping... и прочее...

просто данные по UDP передавать можно с голой ПЛИС, маки такого уровня лежат открыто в интернете.

Передача udp и возможно ещё arp на аппаратном маке zynq. Подобные задачи на софтовых маках решал. Причём только передача пакетов.

-

когда загоняются скоростью LwIP обычно переписывают, из коробки там много жрущих удобств.

Без LwIp обойтись можно ? У кого нибудь получалось работать с драйвером EmacPs?

-

Куда? Хочу посмотреть.

Забыл))

Вопрос еще такой: на отладочной плате есть еще один гигабитный ethernet на zynq кристалле, как вариант можно использовать и его. Скорость необходима около 600-700 Мбит\с. Кто нибудь разгонялся до такой скорости используя lwip? Речь идет о UDP передаче.

-

2 Alexey_Rostov

под рукой нет DS на этот PHY, но в теории, из Clause 28 IEEE 802.3 specification, user-part не используется: вам надо только удостоверится что опорная частота на PHY подаётся, хардварный сборс уложился в рамки написанные в DS и вторая сторона на кабеле работает как надо. А дальше внутри PHY логика сама разбирается согласно Auto-Negotiation Flow.

Хотя думаю желательно конечно чтобы была частота на RGMII TX-clk, TX-ctrl == 0 и RGMII RX не болтались в воздухе (мир не идеален :) ).

(я так понимаю у вас чип - 1512?)

Чип 88E1512 даташит прикрепляю. Осциллографом проверил питающие напряжения VDDO и клок 25 МГЦ от кварца. Спасибо! пока разбираюсь.

-

Немного - это сколько ?

Более 20 мс.

Меня интересует вопрос: какие входные сигналы обязательно должны присутствовать в rgmii для auto negotiation? Только tx clock и tx ctrl?

-

Здравствуйте! Подскажите пжл какие могут быть причины, препятствующие запуску трансивера Marvell 88e5512. Запускаю gigabit Ethernet, интерфейс rgmii. Читаю регистры трансивера без проблем. Контрольный регистр при сбросе сохраняет значение 1140. Что означает режим autonegotiation is enable, скорость 1000, normal operation mode. Трансивер при запуске немного держу в ресете, потом вычитываю контрольный и статусный регистр трансивера. Auto negotiation не проходит и Линк не устанавливается. Попытка после ресета сделать рестарт auto negotiation также к запуску не приводи

Значение статусного регистра: 7949. Что означает extended capability, able to perform auto negotiation, mf preamble suppressing, extended status information in reg 15 и тд. Следует ли работать с другими регистрами для запуска микросхемы или достаточно ресета?

-

Каким образом приходят данные - это пока не столь важно. У меня сейчас в приоритете разобраться именно с записью в DDR. Потом, если я правильно понял назначение системы, эти данные приходят на комп.

Но суть в чём. Да, Вы правы, в моём случае используется второй вариант. Ну и логика мне понятна, кроме... что такое BBT? И как правильно настроить прерывания?

Оговорился BTT - bytes to transfer. Регистр куда пишите количество данных для транзакции.

Вырезки со своего кода скидываю в файл. Там регистрация CDMA и системы прерывания.

Когда это сделаю, мне надо будет с помощью ChipScope убедиться (пока не знаю, каким образом), что данные записываются как надо.Рылся в разных источниках, сейчас в голове немного каша, так что прошу помочь немного разобраться с записью.

Можно вывести старт транзакции например по нажатию кнопки. Сигналы которые хотите посмотреть выводите в чипскоп. Записываете проект в ПЛИС для загрузки его при подаче питания. И через программатор подключаете чипскоп. Дальше стартуете транзакцию по нажатию кнопки. В Чипскопе анализируете.

-

Здравствуйте.

Я в данный момент пробую разобраться, как записывать и считывать данные на/с DDR3. В целом задача состоит в том, что с АЦП поступают данные, которые затем я и хочу записать на DDR-ку. В XPS ещё до меня была уже собрана схема таким образом, что запись/чтение производится посредством CDMA.

Мне же нужно в SDK написать такой код, чтобы данные записывались в память. Я что-то написал, но пока что временно нет возможности проверить, правильно ли и будет ли вообще это работать.

Если необходимо, то работаю я с Virtex-6 (xc6vlx240t).

Код прилагается (не весь, а только основная часть):

int XAxiCdma_Run (XAxiCdma *InstancePtr, u16 DeviceId) { XAxiCdma_Config *CfgPtr; int Status; int SubmitTries = 1; /* Retry to submit */ int Tries = NUMBER_OF_TRANSFERS; int Index; /* * Initialize the XAxiCdma device. */ CfgPtr = XAxiCdma_LookupConfig(DeviceId); if (!CfgPtr) { print("XAxiCdma_LookupConfig failed!\n"); return XST_FAILURE; } Status = XAxiCdma_CfgInitialize(InstancePtr, CfgPtr, CfgPtr->BaseAddress); if (Status != XST_SUCCESS) { print("XAxiCdma_CfgInitialize failed!\n"); return XST_FAILURE; } /* * Setup the interrupt system */ // Status = SetupIntrSystem /* * Enable all (completion/error/delay) interrupts */ XAxiCdma_IntrEnable (InstancePtr, XAXICDMA_XR_IRQ_ALL_MASK); for (Index = 0; Index < Tries; Index++) { Status = CDMATransfer (InstancePtr, BUFFER_BYTESIZE, SubmitTries); if (Status != XST_SUCCESS) { //DisableIntrSystem (IntcInstancePtr, IntrId); return XST_FAILURE; } } /* * Test finishes successfully, clean up and return */ XAxiCdma_IntrDisable(InstancePtr, XAXICDMA_XR_IRQ_ALL_MASK); return XST_SUCCESS; }static int CDMATransfer (XAxiCdma *InstancePtr, int Length, int Retries) { int Status; Done = 0; Error = 0; printf("Start Transfer \n\r"); /* * Try to start the DMA transfer */ Done = 0; Error = 0; /* * Flush the SrcBuffer before the DMA transfer, in case the Data Cache * is enabled */ Xil_DCacheFlushRange ((u32)SourceAddr, Length); Status = XAxiCdma_SimpleTransfer (InstancePtr, (u32)(u8 *) (SourceAddr ), (u32)(DestAddr), Length, Cdma_Callback, (void *)InstancePtr); if (Status == XST_FAILURE) { printf ("Error in Transfer \n\r"); return 1; } }Вот. Посмотрите, пожалуйста, и скажите, может, я где-то ошибся или что-то упустил?

Заранее спасибо.

Вы не указали каким образом данные от АЦП приходят в вашу систему с Микроблейзом.

Можно решить так. Берете DMA со входом stream и выходом memory mapped. Вход подключен к АЦП, выход к DDR. Тогда можно обойтись и без микроблейза (все зависит от того, что дальше будете делать с данными в DDR).

Другой вариант. Свой модуль + CDMA + DDR. Скорее всего как и у вас. С CDMA проще работать через записи в регистры CDMA. Логика простая: записываете данные в три регистра: source, destanation и BBT. Все! Транзакция пошла. Плюс работа с прерываниями.

-

Добрый день. Скажите пжл кто нибудь поднимал ethernet на zynq через армовский мак + трансивер? Интересует реализация без lwip, просто работа со встроенным дма и мак. Если поднимали, то какова максимальная скорость UDP?

-

Здравствуйте! Аналогичная просьба сменить ник на Alexey_Rostov. Спасибо

-

Опубликовано · Изменено пользователем farbius · Пожаловаться

У АЦП есть спецификация по входному импендансу. Оставляя вход неподлключенным вы ее нарушаете. Sample&Hold capacitor практически висит в воздухе и не меняет зарядаПростите не понял про спецификацию и входное напряжение на канале. Взаимосвязь. Если я ничего не подаю то есть просто шум в каждом канале ацп. Подал напряжение на один только канал, на других каналах появились отсчеты причём не только в младших разрядах. Каждый канал содержит на входе RC цепочку

То есть обязательным условием является нагрузка всех каналов?

-

А посмотрите у "восьми канального АЦП" нет ли конвейера с данными? Может после "переключения" Вы еще читаете данные со "старого" канала...

И еще. Моделсим умеет представлять данные как аналоговые, это будет удобнее смотреть, чем в виде HEX-значений...

Конвеера нет. Там мультиплексор кот я управляю

Картинки из сигналтаба специально вывел все каналы

-

Здравствуйте. Возник вопрос по восьми канальному АЦП max 10 development board.

Задействую только одно ядро АЦП. Частоту тактирования выбираю 500 кГц. Подаю постоянное напряжение 2.5 В на каждый канал поочередно.

При этом на незадействованных каналах значение АЦП также увеличивается.

Вот выход АЦП в SignalTab когда на каналах нет входного сигнала

А вот подаю на третий канал постоянное напряжение 2.5 В

При этом на 5, 6, 7 каналы на выходе также почти по 2.5 В.

Если подаю на другие каналы картина аналогична, только заметно влияние на соседние каналы.

Как развязать каналы между собой? Похоже что мультиплексор в АЦП при переключении подхватывает напряжение с соседних каналов.

Частоту тактирования уменьшал, не помогло. Опорное напряжение для АЦП internal.

-

Если Ваша прошивка запускается, то проблема не очень похожая. Но о Вашей проблеме я уже слышал на Альтеровском форуме.

Вот например:

Эту ветку читал. Собрал ацп без ниоса. Взял ядро и написал автомат для вычитывания каналов. Все работает без проблем . В том числе и из флеш. Stewart Little скинул проект кот пишется во флеш и работает. Взял из проекта sof файл и сненерил pof. Ацп из флеш запускается. Свой же проект запустить не могу. Уверен что просто где то торможу.остальные ядра работают. Такое впечатление что не сбрасывается при запуске pll для ацп. Поставлю сигнал тап проверю

-

Слишком мало информации.

Ваш NiosII выполняет код из ОЗУ или из флэша?

Что в настройках девайса в квартусе и OnChip Flash в Qsys'е?

Что в настройках bsp?

И т.д. и т.п.

upd

Запрещен ли вотчдог?

Не думаю что дело тут в том откуда выполняется код. Остальные ядра работают без проблем. Создаю pof с помощью generate mem init в eclipse, на hex файл указываю в on chip memory. Полученный pof пишу в флеш. То есть схема internal configuration и запись в cfm

-

Здравствуйте. Возможно кто нибудь уже сталкивался: max10 dev board 10max50DAE ядро АЦП.

Загружаю sof потом elf АЦП работает, формирую pof c meminit, зашиваю во флеш, и при подаче питания все ядра работают кроме ацп.

Проблема аналогична:

http://www.alteraforum.com/forum/showthread.php?t=52062

http://www.alteraforum.com/forum/showthread.php?t=51978

-

Разобрался.

Оказывается, ножку CONF_DONE(как и все остальные конфигурационные) нельзя использовать как user_IO сразу. А только через несколько милли,микро...секунд после старта. До этого на ножке должна быть чистая подтяжка. Несмотря на то, что я включил все эти ноги "use as user IO".

Здравствуйте. Можно по подробнее о решении? Похожая проблема на development board с 10max50DA. Только не запускается с pof файла АЦП. При этом sof работает без проблем

-

Товарищи подскажите пжл как быть с triple speed Ethernet ядром чтобы time limited обойти?

-

-

TSE, как и любой MAC считает только FCS Ethernet пакета, может заменять MAC адрес в данных на адрес, который забит в регистрах контроллера. Для приёмника проверяет/удаляет FCS пакета, отбрасывает пакеты с битой FCS, есть возможность настроить фильтрацию MAC адресов. Контрольная сумма UDP не обязательна (по желанию) можно нулями забить. Не помню уже сколько можно выжать из софтового стека, для большого потока использовал железную реализацию UDP (передаёт поток 655.36 Mb/s, можно и выше).

спасибо за ответ. Еще есть вопрос: UDP Offload это просто примочка для дополнения пакета служебной информацией? doom13 может есть сишный мэйн для запуска всего этого добра? буду очень признателен

-

Ищите по форуму, была тема для Cyclone III. Ещё возможно понадобится железный UDP offloader - на Altera Wiki есть пример реализации и тут где-то был.

Нет там никакой навороченной работы с регистрами, максимум вставка MAC адреса, удаление FCS, фильтрация (надо-не надо) и т.д. Основная задача ложится на DMA - бросает данные в/из памяти.

Насколько помню для УДП контрольная сумма подсчитывается причем не только FCS по всему пакету но и на других уровнях (имею ввиду с UDP header и еще одна с IP header) их тоже Ниосом считать или tse автоматом рассчитывает все суммы? Такой софтовый UDP как посмотрел по форуму до 100 Мбит\с обеспечивает?

-

Опубликовано · Изменено пользователем farbius · Пожаловаться

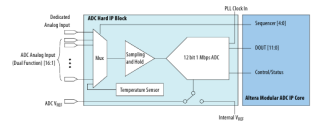

Система будет выглядеть так:передача - Tx Packet Data Memory -> SgDMA MM2ST -> TSE

приём - TSE -> SgDMA ST2MM -> Rx Packet Data Memory

Ищите по форуму, была тема для Cyclone III. Ещё возможно понадобится железный UDP offloader - на Altera Wiki есть пример реализации и тут где-то был.

Нет там никакой навороченной работы с регистрами, максимум вставка MAC адреса, удаление FCS, фильтрация (надо-не надо) и т.д. Основная задача ложится на DMA - бросает данные в/из памяти.

зачем там SgDMA? Просто чтобы мемори маппед в стрим переделать? CDMA не подойдет именно Sg нужен?

-

Здравствуйте.

Может кто подскажет варианты решения след задачи. С MAX 10 Development Kit послать UDP пакеты через ethernet.

Есть Simple Socket Server и для этой платы. Раньше на stratix II подобную задачу решил расковыряв Simple Socket Server пример, при этом остался на Micro Os.

Хотелось бы максимально упростить систему для UDP пакетов. При этом соединение плата -- ПК типа точка точка. Никаких ARp запросов ненужно.

Кто нибудь собирал систему с Nios + TSE + buffer для UDP пакетов + например ДМА? В системе просто осуществляется настройка PHY и далее работа с драйверами TSE?

Или там навороченная работа с регистрами TSE ядра?

MicroBlaze is under RESET что это и с чем его едят?

в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Опубликовано · Пожаловаться

Проверьте RESET для микроблейза. рекомендую вывести на кнопку или свитчер. В настройках SDK попробуйте программатор выбрать не автоматически, а например Digilent progr cable если вы работаете через миниUSB.