-

Постов

1 266 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Flip-fl0p

-

-

7 минут назад, Мур сказал:

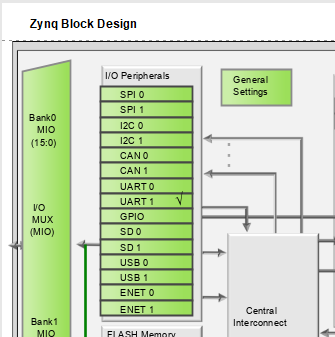

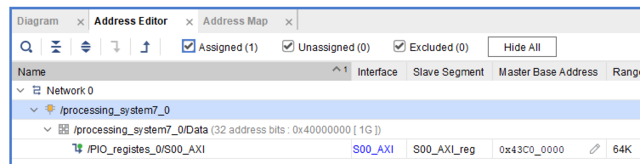

Приветствую корифеев! Очередная непонятка касательно распределения адресов в простеньком проекте (развитие указивки от https://habr.com/ru/articles/535226/)

Я решил схитрить, чтобы Витис мне позволил подключить сишные библиотеки в болванку "Hello World".(Иначе только пустой проект!)

и вставить UART1 (MIO 12 и 13). Но в редакторе адресов этот дополнительный адрес не появился! Только тот, что руками правил по мурзилке...

В чем дело, народ?? Я не буду знать расположение его UART регистров... Подскажите, в чем секрет? В чем необходимость его регистры прятать?

Эта карта адресов - для всего того, что висит на AXI4 шине.

А процессорный уарт управляется по-другому.

-

Тут проблема в том, что камера выдает данные медленнее чем идет один период развертки экрана. Даже при разрешении экрана 640*480. Без накопления кадра в кадровом буфере нормально выдать картинку мне кажется нереальным. Более того, даже одного буфера может быть мало для нормального вывода. Минимум 2 буфера. А в идеале полноценная тройная буфферизация. Я когда игрался с этой камерой именно так и выводил изображение. Но само по себе изображение шумное. По-хорошему надо ещё и обработку изображения делать. Ну или я недостаточно изучил даташит на камеру и не совсем корректно настроил её.

-

Посчитайте скорость развертки экрана и скорость поступления данных от камеры.

-

Без кадрового буфера работать не будет. А в идеале тройная буфферизация.

-

7 минут назад, Мур сказал:

Спасибо за понятный ответ!..

Да, с этим можно жить. Ну а в пределе, когда на борту есть MCU , можно финтить по-всякому! Другое дело затраты времени. И цейтнот вынуждает "искать пятый угол".

Именно дампы! Сам случайно заметил такую возможность у КВА. Радовался, потому как мечта была рядом (но с железом!) у МоделСим такой дружественной возможности документирования раундов нет, а очень бы помогло!

У Хилых не только крутой логический анализатор (ILA), который можно по-разному конфигурировать, и при должной сноровке автоматизировать скриптом. Местами может быть неудобно. Но на самом деле я переучился с signal_tap и вполне доволен жизнь. Теперь signal_tap кажется неудобным. У Хилых очень удобные виртуальные вводы\выводы (VIO) которые позволяют вручную вводить\выводить значения внутри проекта. При должном желании на основе этого можно даже стенды для дебага изделий делать, в случае если нет времени на разработку полноценных рабочих мест. Так-же есть JTAG to AXI, который позволяет через JTAG считывать память\записывать память через AXI интерфейс, что очень круто помогает в разработке.

И самое главное дофига всего можно написать на TCL. А сколько возможностей есть, если уметь пользоваться инструментом... Один режим внесения инженерных изменений, когда вы в уже в размещенном проекте изменяете часть дизайна. В плане возможностей софта Xilinx впереди планеты всей.

-

1 минуту назад, Alex77 сказал:

вивадо по умолчанию требует чтоб все порты топ модуля были явно привязаны к пинам. другими словами помогает не накосячить.

Накосячить не страшно, если FPGA недорогая. А если это какой-нибудь кристалл за несколько десятков вечнозеленых енотов, то накосячить страшно.

Удивительно, что вместо того чтобы сделать правильно, человек применяет костыли, чтобы сделать неправильно. Тем более сделать правильно - работы на пару минут. Не вижу сложности в том, чтобы добавить констрейн на ножку.

-

Возможно вы добавили PLL c кривыми настройками. Или клок с PLL не заходит на глобальное тактовое дерево. Создайте PLL через wizzard.

-

37 минут назад, Maverick_ сказал:

Vivado: Set VHDL-2019 or VHDL-2008 for all .vhd files

To tell Xilinx Vivado to compile a VHDL file using the newer VHDL-2019 or VHDL-2008 revisions in the GUI, you can go to Project Manager->Sources->Compile Order, right-click the .vhd file, and select Source File Properties. Then, you can click the Type property and change the VHDL revision using the dialog box. You have to right-click every single file to make the change.But you can easily change the VHDL revision of every single file in your project to 2019 by entering this command in the Vivado GUI’s Tcl Console:

set_property FILE_TYPE {VHDL 2019} [get_files *.vhd]

Or set all .vhd files to 2008 with this Tcl command:set_property FILE_TYPE {VHDL 2008} [get_files *.vhd]

Знаю про этот костыль. Однако есть нюанс. Он ищет все файлы .vhd В том числе и сгенерированные автоматом. Я не моду дать гарантии, что данная команда не сломает что-либо в авто-генерированном мусоре. А учитывая, что в Vivado и так полно всяких "фич", от которых проект может сломатья - то я не рискую так делать. Может и зря.

-

5 минут назад, andrew_b сказал:

Не знали что? Что из того, что я написал, явилось для вас новостью?

Там всё правильно написано. Но есть нюанс.

Когда я читаю код и вижу список чувствительности

process (clk)я понимаю, что это в этом процессе будет описан синхронный триггер.

Когда я вижу

process (reset, clk)я понимаю, что это описан синхронный триггер с асинхронным сбросом.

Когда я вижу

process (all)я ожидаю увидеть комбинаторику, типа

process (all) begin y <= x1 or x2 or x3 or x4; end process;А если в таком процессе внезапно оказывается триггер, то у меня возникают сомнения в квалификации автора кода и в качестве самого кода. Это то же самое, как и

process (clk, reset, ce, x) begin if (rising_edge (clk)) then if (reset = '1') then y <= '0'; elsif (ce = '1') then y <= x; end if; end process;Можно в вписок чувсвительности вписать все сигналы, но зачем? Чтобы что? Профита это никакого не даёт, а даже наоборот.

На что вы тратите те секуды, которые сэкономили на написании all вместо правильного списка чувствительности?

Полностью поддерживаю. Еще у VHDL 2008 есть нюанс при работе с Vivado. Заключается в том, что там нет возможности каждый VHDL файл рассматривать как версию 2008. Это надо дополнительно руками указывать. Неудобно. А вообще все проблемы со списком чувствительности из-за непонимания, как он работает.

-

Весь код неправильный. На ПЛИС так писать нельзя. За такой код бить по рукам нужно.

-

Бездумное применение Variable - может сломать код. Обьявлять счетчик как Variable - полюбому проблема именно в этом.

-

1 час назад, Maverick_ сказал:

ответ же на

🙂

Ну так я понял. Только где здесь полу-асинхронный ? Тута обычная цепочка триггеров. 😁

-

18 часов назад, Maverick_ сказал:

вот взято с темплате vivado2019.1

для verilog

для vhdl

Так это обычный синхронизатор.

-

2 часа назад, Burenkov сказал:

Попробуйте SPI_READY через два триггера пропустить перед использованием. Может быть s_spi_ready_1 оказывается в метастабильном состоянии

Добавлю, что этого мало. Еще бы правильно констрейнами, или атрибутами подсказать синтезатору, что тут цепочка CDC триггеров.

-

1 час назад, yes сказал:

если запретили использовать SV для тестбенча, то я даже не стал спорить о вкусах 🙂

но если серьезно - если вызов симулятора из make или из "регрессионного скрипта" - то в случае ошибки симулятор возваращает не 0, а еррор-коде, что разваливает эти make и скрипты. так что, я считаю, что требование законное.

возможность есть (не знаю в каком стандарте VHDL ее добавили, но легко гуглится) меня интересовало, кто без гугления знаетusestd.env.finish; Есть готовые процедуры -

-

23 часа назад, jenya7 сказал:

signal fpga_outputs : std_logic_vector(40 downto 0) := ((0 downto 19) => '1', others => '0');

А ничего, что у вас нет диапазона 0 downto 19 ?

-

Так объявите их как дифф сигнал. Вы этого не сделали.

-

Тема создана 16 августа. Сегодня 23. Считай неделя прошла.

Вопросы автору:

1. Вы скачали и подключили модель памяти ?

2. Вы прочитали даташит на память ?

3. Вы поняли как работать с динамической памятью ?

-

А зачем вообще использовать этот SDRAM контроллер ? Не проще ли кастомный тогда ? Или это hard IP ?

-

В 28.07.2023 в 21:04, sazh сказал:

rx_aligner

А можно поподробнее ? ))) Все время приходилось своими силами выравнивать клок путем динамического сдвига фазы. Неужели можно это не делать теперь ?

-

Прежде чем принимать поток по 8b/10b - неплохо было бы сделать битовую синхронизацию. Ошибки могут быть не только из-за неправильной работы декодера, но и из-за неправильного положения фронта клока. Вообще можно скачать готовое ядро 8b/10b от Xilinx. У них есть разные варианты в том числе и на основе блочной памяти.

-

1

1

-

-

Начните с бумаги и карандаша и ластика. Рисуете схему на бумаге. Потом переносите её на код. Большинство вопросов отпадает уже на этом этапе.

-

57 минут назад, Koluchiy сказал:

Вопрос: при отсутствующих ILA оказывают ли mark_debug влияние на синтез?

Скорее всего да. Ибо часто бывало так, что не подключая ни одну ILA к проекту, но оставляя линии помеченными mark_debug проект собирался со слаками. Удалив атрибуты mark_debug, но при этом больше не внося никаких изменений в код - собирался с огромными запасами по слкам.

Обработка помех на пути сигнала

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

Обычный фильтр анти дребезга.