rash230691

Участник-

Постов

33 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о rash230691

-

Звание

Участник

- День рождения 23.06.1991

Информация

-

Город

Array

-

DVI и TimeQuest

rash230691 ответил rash230691 тема в Языки проектирования на ПЛИС (FPGA)

Я хочу максимально компенсировать разницу в длине дифф пар. Приемник у меня конечно может и простой, но в нем конкретно прописаны длины синхронизирующих последовательностей, но вот от компиляции к компиляции результат не стабилен, он может "поймать" синхронизацию, а может и не принять -

DVI и TimeQuest

rash230691 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

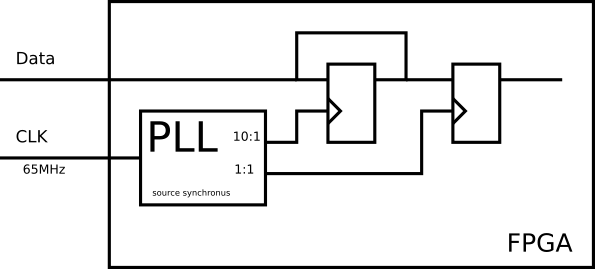

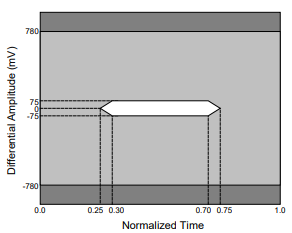

Доброго всем! Имеется плата с кривым разводом DVI и как следствие кривым приемом данных по этому самому DVI. Решил поправить данную ситуацию с помощью TimeQuest, но, скорее всего из-за малого опыта, у меня это не удалось. Схема всего этого безобразия во вложении, вкратце поясню: данные со скоростью 650 Mbps поступают в сдвиговый регистр 1:10, далее уходят на пиксельной частоте в обработку PLL имеет тип source synchronous, умножает входную частоту на 20, первый выход делит на 2, второй на 20 имеется простой блок подстройки фаз PLL, который ориентируется на входные данные Все что я знаю о источнике сигналов - глазковая диаграмма из спецификации на интерфейс(во вложении, диаграмма нормализованная) Имея сей стартовый набор данных, я набросал ограничений: Описал входную частоту Описал виртуальную частоту со сдвигом 180 градусов(center aligned) Объединил их в одну группу Задал задержки относительного виртуальной частоты Собственно к чему все это... Просьба "оценить" написанные ограничения, да и от советов по приему и десериализации данных сигналов не откажусь -

Согласно документации, если Vccpd банка 3а посажен на 2.5В, цепи jtag(TMS, TDI) платы должны быть подтянуты к в Vccpd(2.5В) Сейчас же они подтянуты к 3.3В на плате. Вопрос: долго ли будет жить(будет ли вообще) JTAG ПЛИС запитанный от 3.3В при эксплуатации.

-

JTAG cyclone 5

rash230691 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток! Имеется Cyclone 5, пины JTAG располагаются в 3А банке, Vccpd_3а = 2.5V. Пины JTAG(TMS и TDI) подтянуты через резисторы к 3.3В, на 4 пин разьема также подаётся 3.3В. Интересует Ваше мнение по двум вопросам: можно ли так делать и стоит ли менять на 2.5В? Надеюсь на конструктивный диалог. -

Прошивка флэшки

rash230691 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток всем! Имеются ли способы прошить EPCS на прямую не pof файлом(~15 минут), а чем-нибудь более оперативным. Через плисину и jic не получится прошить. Спасибо за внимание -

Замечательно что специальный, тоже на него зарился, но сказали что нужен стандартный, что б с проводами меньше проблем было, так что увы =(

-

Только отечественное =( а 8p8c заменить чем-то сложно, СНЦ туда не впихнуть(плюс по ТУ у большинства 3МГц, я все понимаю что можно больше, но документ есть документ)

-

Отечественный разъем

rash230691 опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Доброго времени суток! Обращаюсь к знатокам ОЭБ: кто может подсказать, есть ли у нас разъемы и трасформаторы под 100мбитный ethernet? Можно в сборе. СНЦ и прочие цилиндры не предлагать, нужен референсный дизайн(опять же наличие диодов не критично) Спасибо за внимание -

Необходимо сохранить постоянную составляющую сигнала

-

Входной буфер АЦП на отечественных ОУ

rash230691 опубликовал тема в Вопросы аналоговой техники

Доброго времени суток! Передо мной стоит следующая задача: организовать входной буфер перед АЦП 5101НВ015 ф.Миладр на отечественной элементной базе =( Вкратце о сигнале: дифференциальный, полоса 40 МГц, напряжение сигнала – в диапазоне от минус 2 до 2В. Проблемы: 1) Не найдено ни одного отечественного дифференциального ОУ, соответственно было принято решение собирать из обычных ОУ что-то похожее на дифф. (схема эквивалента бралась из книги analog devices) 2) Найден был ОУ ф. Пульсар, работающий на биполярном питании, что так же не устроило заказчика. Есть ли вообще отечественные ОУ с однополярным питанием с единичным усилением на данную полосу? Может кому-то вопросы покажутся простыми и не достойными обсуждения, но я все время занимался только ПЛИС и достаточно далек от аналоговой техники. Спасибо за внимание -

Благодарю P.S. Удалите этот топик как позорный

-

Verilog + Modelsim

rash230691 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Доброго времени суток, форумчане! Бьюсь третий день на следующей проблемой: module SF_main_vlg_tst(); parameter h_p = 5; parameter size = 1024; reg clk; reg reset; reg start; reg signed [15:0] image_re; reg signed [15:0] image_im; reg signed [15:0] signal_re; reg signed [15:0] signal_im; // wires wire eop_o; wire sop_o; wire valid_o; wire [15:0] source_real; wire [15:0] source_imag; reg signed [15:0] image_re_mem [size-1:0]; reg signed [15:0] image_im_mem [size-1:0]; reg signed [15:0] signal_re_mem [size-1:0]; reg signed [15:0] signal_im_mem [size-1:0]; integer i = 0; event fin_sim; event init_done; event file_read_finish; initial begin $readmemb("LFM_re.dat",signal_re_mem); $readmemb("LFM_im.dat",signal_im_mem); $readmemb("LFM_image_re.dat",image_re_mem); $readmemb("LFM_image_im.dat",image_im_mem); end always @(init_done) begin for(i = 0; i < size; i = i + 1) begin @(posedge clk); signal_re = signal_re_mem[i]; signal_im = signal_im_mem[i]; $monitor("[%d]=[%d]",i,signal_re); end signal_re <= 0; signal_im <= 0; ->file_read_finish; end always @(posedge valid_o) begin for(i = 0; i < size; i = i + 1) begin @(posedge clk); image_re <= image_re_mem[i]; image_im <= image_im_mem[i]; end image_re <= 0; image_im <= 0; end always @(posedge start) begin ->init_done; @(posedge clk) start = 1'b0; end initial begin start = 0'b0; repeat(10)@(posedge clk); start = 1'b1; @(file_read_finish) repeat(3000)@(posedge clk); ->fin_sim; end SF_main #(size,16) i1 ( .ch1_imag(signal_im), .ch1_real(signal_re), .clk(clk), .eop_o(eop_o), .image_re(image_re), .image_im(image_im), .reset(reset), .start(start), .sop_o(sop_o), .valid_o(valid_o), .source_real(source_real), .source_imag(source_imag) ); always @(fin_sim) $stop; initial begin reset = 1'b0; repeat(2)@(negedge clk); reset = 1'b1; repeat(1)@(negedge clk); reset = 1'b0; end initial begin:clk_desc clk <= 1'b0; forever #(h_p) clk = ~clk; end endmodule Имеется такой тестбенч, но вот результаты его я объяснить не могу и, соотвтственно, изменить поведение в нужное русло так же не могу. Результаты ниже в аттаче. Как видно - первый раз вычитывается каждое второе значение из памяти, при повторном же - все. Собственно вопрос: что это? и как на это повлиять? Благодарю за внимание -

И вновь TimeQuest

rash230691 ответил rash230691 тема в Среды разработки - обсуждаем САПРы

Премного благодарен -

И вновь TimeQuest

rash230691 опубликовал тема в Среды разработки - обсуждаем САПРы

Доброго времени суток, уважаемые форумчане! Сложилась такая ситуация, что необходимо срочно въехать с нуля в работу с TimeQuest. Начиная с того - зачем это нужно, и заканчивая(заканчивая ли?) описанием констрейнов под crossdomain. Книги, статьи любая текстовая информация. Язык предпочтительный - Русский, если англ. то не критично. Кто чм может помочь? Благодарю за внимание. -

Аналоги ПЛИС

rash230691 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго времени суток, уважаемые форумчане! В данный момент ищем альтернативные ПЛИСы для сравнения, но из-за кривости рук(или сайта, у Альтеры как-то проще) не могу найти таковых. Имеются таковые: EP3SE50 EP3SE80 EP3SE110 EP3SE260 Не могли бы помочь подобрать аналоги у Xilinx? Спасибо