Adv

-

Постов

120 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Adv

-

-

-

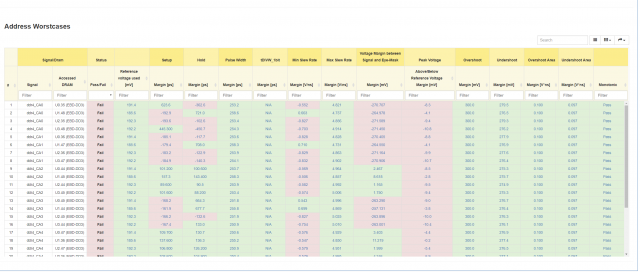

Да. И - ещё очень много ошибок в осциллограммах при просмотре лога. Их просто небыло. Смотрел по файлам вручную.

-

Именно! Там - указание Vref не дало ничего. Подозреваю ошибку в скрипте.... Падало на нём.

-

-

Попробую, займёт нек. время. Отвечу результат.

-

Никак.... Смотрю на обилие возможностей модификации параметров контроллера- памяти делается нехорошо. Промазать - раз плюнуть.

МОжно его в модели ВХОДА дописать..... Но - неправильно это наверное.

Самое противное - шину данных и стробы - нет вопросов. усё идёт...

-

-

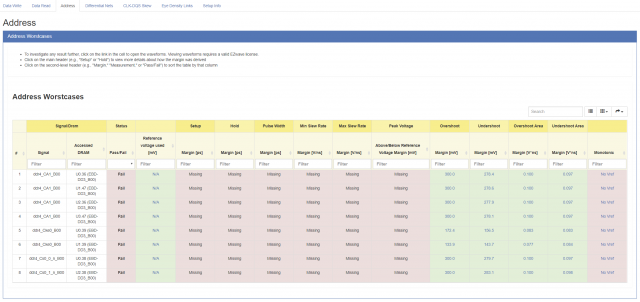

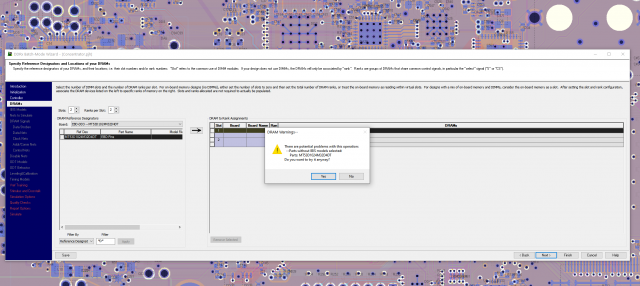

Нашёл! В режиме Board надо было просто переключить поле RefDes/ У меня там стояло DD а переключить надо на эти самые U. СПАСИБО!

-

21 минуту назад, PBO сказал:

2.6

По-моему - что-то с представленим самого ЕBD. Так как для EBD-MT53D1024M32D4DT (мой случай) НЕ ВИДНО внутренних die этих самых U0, U1 и т.д.

-

11 минут назад, PBO сказал:

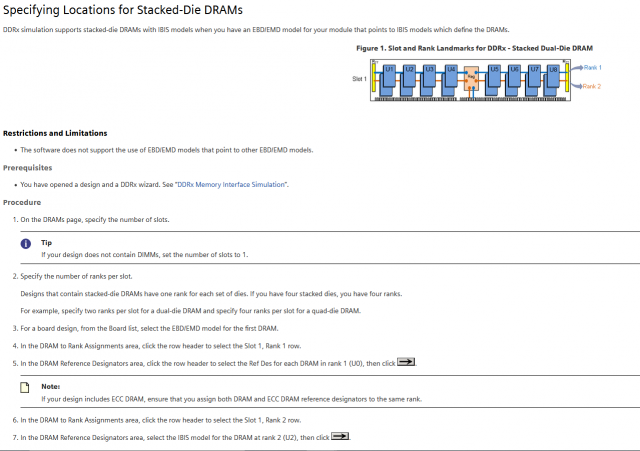

Все имена пинов в файле .ebd должны совпадать со всеми именами пинов вашего устройства. Если имена контактов отличаются (1,2,3 против A1, B1, C1), то модели будут назначены неправильно. Кроме того, все модели в разделе [Reference Designator Map] должны быть доступны в каталогах библиотеки.

Спасибо за цитирование гайда..... ВСЕ возможные методы я пробовал. Если знаете как - подскажите пооперационно. Модели - фирменные. Ошибок с пинами в них нет.

-

9 минут назад, PBO сказал:

EBD модели назначить через меню Models > Assign Models/Values by Referenec Designator или Models > Assign Models/Values by Part Name

назначаются. Только - при DDRx Batch wizard выдаёт сообщение что моделей собственно памяти - НЕТ. Файл пинами - есть. И все попытки назначить что-то не увенчались успехом.

-

Доброго времени суток!

Кто-нибудь использовал модели .ebd? Если да - то подскажите как это правильно делать в HyperLynx DDRx batch simulation.

Заранее благодарю.

С уважением Adv.

-

Поясните, пожалуйста, фразу "в 7 раз лучше".

Частота была 30 МНz, а стала 210 МHz?

Или slack был -0.700, а стал -0.100?

последнее. Результат колебался от -1.905 (худший) до -0.205 (лучший)

Зы. открыл. Посмотрел ещё раз - -0.259

-

Вы компом хвастаетесь? :rolleyes: Вы смотрели использование квартусом памяти ядер? Он даже этого то толком проглотить не может, у меня 32 Гб - выкинутые деньги, и 16 хватило бы, 2 ядра - за уши, квартус второе даже нагрузить не может. Так что прогресса не ждите покаместь.

Ну чего сразу так-то... Каждому овощу - свой фрукт.

вот результаты работы с квартусом 16.0.2.222 для сложного проекта:

По сравнению с 8(16 логических) ядерным с 96ГБ – короче приблиз.на 35-40 минут. НО! Ресурсы – 60(120 логических) ядер боле сем на 23 процента не используются! Т.е. – средняя загрузка – 12 процентов. Память более 43ГБ тоже не используется (Из 256ГБ имеющихся).

ИТОГО: с 3ч 12 мин до 2ч 21мин и надо выбросить нек. время на паузы между перезапусками – 35-40 мин чистого опережения.

ВЫВОД: при одиночной компиляции за ресурсами гнать не стоит. Баланс овчинка-выделка – только до 128ГБ и 8-16 физических ядер….. У меня получается так.

ИНОЕ дело - использование DSE. Результаты:

Вещь здоровая, и вполне рабочая. Правда , есть трудности с запуском/выключением на первых порах (не всё там так ка в видео- или в примерах). В этом месте (вариации в ходе синтеза) надо сразу сказать - ЖУТЬ - до 100 процентов мощности процов в моей "байде"

и до 75% памяти. При фиттере такого нет. Там есть до 98% долго но не так резко , и память выше 49% не ходит.

Эмоции....

Однако - общее - 3ч 43 мин на 6-ть проектов в одновременной компиляции. Из них 5-ть проектов заканчиваются прибл. в тоже самое время (2ч 34 мин) что и ОДИН проект, если его отдельно компилить!!

И - получается потом один их них, в котором временные параметры прибл. В 7 раз (!!) лучше, чем у среднего.

Так что всё - для своего круга задач. У каждого - он разный, и далеко не всё то, что хорошо одному можно рекомендовать всем.

С уважением и извинениями за моногословность.

Зы. "байда" - 60 физических (120 логических) ядер конфигурируемая до 6 Тб ОЗУ (96 х 64ГБ) при частоте 2.8 ГГц. Было выставлено ограничение не более 256ГБ для этой работы.

-

На счёт BluePrint скажу одно - мысли были хорошие, а пока получается "как всегда"..... Работаю с последней Арией и раз пять пробовал это самое чудо. Да, быстро. Да, всё раскладывает.

Правда - лично у меня после этих процедур фиттер так и не прошёл. Ни разу. Ошибки.

Пока так. Совсем не так, как в презентации. Ждать надо. Полагаю доделают. Бета же!

-

Я правильно понимаю, что повреждено ядро с Uniphy? Или имеется в виду что-то другое?

Да, оно .

-

Так а как с лекарством быть для QII v13.0 и OpenCL ?

На сервере... Без CL.... пока....

-

А с 7кой как?

Виснет ли текстовый редактор?

Виснет ли при компиляции?

Нормально, вроде. А вот что с упаковкой памяти - пока не понял. Старый проект что в 11, что в 12, что в 12.1 - нормально. А в 13 пишет, что число блоков M9K больше, чем в чипе.... Нонсенс.

И - вдогонку - во всех версиях старше 11.1 "повреждено" (т.е. неудачно исправлено) ядро DDR3 (это не касается AltmemPHY!) Из-за этого часть старых систем неработоспособна. В 13 - кроме упаковки памяти почему-то не передаются параметры для моста Half_rate_bridge .

-

А контроллер использовался от 12.1?

-

:1111493779:

Доступен на альтеровском http.

Самое печальное - он НЕПРАВИЛЬНО генерирует мосты в QSYS..... Все системы, где в качестве ОЗУ используется DDR3 (т.е. без внутренней памяти для этой цели) и какой-нибудь мост между ним и процом (например Half_Rate или Clock_Crossing). И - усё....приехали. Почти все старые системы НЕ РАБОТАЮТ после перегенерации.Ну, кроме простейших, где всё включено напрямую, а частоты - никакие. И замечаний или ошибок - в рапорте нет. Просто компилятор выбрасывает процессор из системы. Сразу видно по кол-ву элементов и памяти в конце синтеза. Даже дальше идти ненадо. А суппорт говорит просто - а в дизайне нет критических ошибок! Значит - всё в порядке...

Des00 полностью прав. Жаль.

-

Да..... Презанятные (если это вообще можно сказать) документы.....

Но, вот эта строчка лично меня повергает в..... ну, в тихий шок, что ли... :

The researchers assertion is that with the discovery of a security key, a hacker can gain access to a privileged internal test facility typically reserved for initial factory testing and failure analisis.

(из документа Victor http://www.microsemi.com/documents/corpora...C3%20053112.pdf )

Значит, следует понимать, что этот подход типичен для производителей?? И других FPGA тоже??

Просто других пока - не пробовали "на зуб" ?? Как у поэта - это как же вашу мать, извиняюсь, понимать???

-

http://www.mosys.com/userfiles/file/MoSys_BE1_PB.pdf

Посмотрите, когда есть время. Может, кому и понадобится.....

-

Конечно полностью, причем файл test3c40_8_1200mv_85c_v_slow.sdo реально есть, только вот похоже он из модулей внутри состоит, и модуля для altdq нет...

В RTL не симулирует, проект в графике, а ему (моделсиму) как я понимаю, надо HDL.

Именно!!

Перейдите в языковое описание проекта - и усё должно пойти..... (Что - само - не гарантирую....). И ещё - Ква иногда выбрасывает "ненужные" модули.... С Моделсимом хорошо отлаживать написанные проекты - их только синтезируют (или вообще - доверяют Моделсиму и полностью создают/работают в его среде) и лишь потом - в "железо", т.е Ква, и т.д......

-

Коллеги, хоть напишите, что, мол, делали так, работает... Непонятно то ли софт у меня глючный - переставить, то ли еще что...

Простите - вопрос - а Вы после добавления компонента (altdq) полность проводили компиляцию?? Имею ввиду - до конца, до получения файлов прошивки?? Или только синтез??

Дело в том, что я вижу в приведенных Вами логах только то, что этого самого компонента нет в файлах реальных задержек (.vo или .sdo)........

Можете провести эксперимент - отключите эти самые реальные задержки и посмотрите, симулируется или нет.

Использование EBD моделей памяти в HyperLynx DDRx batch simulation

в Siemens EDA - Xpedition, PADS (ex. Mentor)

Опубликовано · Пожаловаться

Да. Визард не менял. Модели - тоже не менял. Старую - снёс. Настройки в СТАРОЙ уже не покажу (картинками), не смогу. Логи посмотрю. Займёт нек. время. Навёрстывать надо. Неделю потерял в песок.