jenya7

Участник-

Постов

3 718 -

Зарегистрирован

-

Посещение

Весь контент jenya7

-

Проблема с PLL

jenya7 ответил jenya7 тема в Работаем с ПЛИС, области применения, выбор

я когда кликаю в дереве проекта на моддуле PLL появляется wizzard и я вижу все настройки. у модуля ADC есть внутренний PLL, но почему то в другом проекте он не компилируется как аппаратный PLL. я думал может модуль ADC как то криво компилируется но я не получаю никаких ошибок пока не добавляю эту строку в процессе сканирования каналов. Сделал такой эксперимент. Вернул строку Adc1State <= ST_START_CONV; и в следующем состоянии убрал adc1_com_valid <= '1'; when ST_START_CONV => --adc1_com_valid <= '1'; Adc1State <= ST_WAIT_FOR_DONE; и всё компилируется. сигнал adc1_com_valid это начало конвертации канала. то есть если убрать эту строку то внутренний PLL ADC модуля реализуется фитером как то иначе? что за жесть? -

Проблема с PLL

jenya7 ответил jenya7 тема в Работаем с ПЛИС, области применения, выбор

там же блок - if - else. если одно условие - иди направо, другое условие - иди налево. и потом - как это влияет на решения фитера создать ещё один PLL? -

Проблема с PLL

jenya7 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Есть проект с MAX10 10M50SAE144I7G. Добавил в проект модули PLL и ADC с уже существующего проекта с таким же FPGA. component pll is port ( inclk0 : in std_logic := '0'; c0 : out std_logic; c1 : out std_logic; c2 : out std_logic; c3 : out std_logic ); end component; component adc_qsys is port ( adc_1_command_valid : in std_logic := '0'; -- adc_1_command.valid adc_1_command_channel : in std_logic_vector(4 downto 0) := (others => '0'); -- .channel adc_1_command_startofpacket : in std_logic := '0'; -- .startofpacket adc_1_command_endofpacket : in std_logic := '0'; -- .endofpacket adc_1_command_ready : out std_logic; -- .ready adc_1_response_valid : out std_logic; -- adc_1_response.valid adc_1_response_channel : out std_logic_vector(4 downto 0); -- .channel adc_1_response_data : out std_logic_vector(11 downto 0); -- .data adc_1_response_startofpacket : out std_logic; -- .startofpacket adc_1_response_endofpacket : out std_logic; -- .endofpacket clk_clk : in std_logic := '0'; -- clk.clk reset_reset_n : in std_logic := '0' -- reset.reset_n ); end component; ----------------------------------------------------------------------------------------------------------------- U_SYS_PLL : pll port map ( inclk0 => OBE_CLK, c0 => s_pll_clk_120M, c1 => s_pll_clk_100M, c2 => s_pll_clk_30M, c3 => s_pll_clk_10M ); U_SYS_ADC : adc_qsys port map ( clk_clk => s_pll_clk_10M, reset_reset_n => '1', adc_1_command_valid => adc1_com_valid, adc_1_command_channel => adc1_com_channel, adc_1_command_startofpacket => adc1_com_startofpacket, adc_1_command_endofpacket => adc1_com_endofpacket, adc_1_command_ready => adc1_com_ready, adc_1_response_valid => adc1_resp_valid, adc_1_response_channel => adc1_resp_channel, adc_1_response_data => adc1_resp_data, adc_1_response_startofpacket => adc1_resp_startofpacket, adc_1_response_endofpacket => adc1_resp_endofpacket ); Всё скомпилировалось без проблем. Я добавил процесс сканирования всех каналов каждые 100 мс. И тут фитер генерирует ошибку Он почему то генерирует два PLL а на самом деле есть один. Начал убирать куски кода в процессе и нашел что если убрать всего одну строчку Adc1State <= ST_START_CONV; то всё компилируется. when ST_SELECT_CHAN => adc1_ena <= '0'; chan := chan + 1; if (chan > 8) then Adc1State <= ST_WAIT_FOR_TRIG; else case chan is when 1 => adc_chan := "00001"; when 2 => adc_chan := "00010"; when 3 => adc_chan := "00011"; when 4 => adc_chan := "00100"; when 5 => adc_chan := "00101"; when 6 => adc_chan := "00110"; when 7 => adc_chan := "00111"; when 8 => adc_chan := "01000"; when others => end case; --Adc1State <= ST_START_CONV; --без этой строчки компилируеися end if; Это как вообще? -

интересно а как без if (clk3 = '1') then? не работать по фронту? а как тогда? после многих экспериментов непосредственно прием-передачу я разбил на два процесса. работает чётко, без проблем. проблема возникала в синхронизации - DATA_OUT. мой изначальный вопрос - когда DATA_IN = 0x34 - buf_in = 0x1 0x4 - а должно быть 0x3 0x4 - это было именно из рассинхрона между модулями. почему то это оказалось непростой задачей несмотря на то что модуль передающий DATA_OUT сидит на тех же SPI_CS и SPI_CLK. процесс передающий DATA_OUT был записан так if (clk3 = '1') then clk2_count := clk2_count + 1; end if; case clk2_count is when 0 => data_1553_out <= DOUT(7 downto 0); when 1 => data_1553_out <= DOUT(7 downto 0); when 2 => data_1553_out <= DOUT(7 downto 0); when 3 => data_1553_out <= DOUT(15 downto 8); when 4 => data_1553_out <= DOUT(15 downto 8); State <= ST_READ_3; when others => end case; переписал так if (clk3 = '1') then clk2_count := clk2_count + 1; end if; if (clk2_count = 4) then State <= ST_READ_3; else if (clk2_count < 2) then data_1553_out <= DOUT(7 downto 0); else data_1553_out <= DOUT(15 downto 8); end if; и теперь работает нормально.

-

в смысле? у меня физически 4 линии.

-

LIBRARY ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.std_logic_unsigned.all; видел эти варианты. в первом input logic MOSI_0, input logic MOSI_1, input logic MOSI_2, input logic MOSI_3, output logic MISO_0, output logic MISO_1, output logic MISO_2, output logic MISO_3 у меня нет отдельных линий. у меня SPI_DATA : inout std_logic_vector(3 downto 0); второй вариант похож на вуду маджик.

-

Алокация строк

jenya7 ответил jenya7 тема в ARM, 32bit

Всё. Когда мат иссяк пошёл посмотрел старые проекты - он там всё переделал. В новом проекте он уже забыл об этом. Извиняюсь за это насилие над коллективным разумом. -

Алокация строк

jenya7 ответил jenya7 тема в ARM, 32bit

тут нужно объясниться. в нормальном мире такое не может произойти. но у нас один кадр написал парсер на сотни строк в таком виде if(strcmp(ToLower(args[1]), ToLower("WRITE")) == 0) ему видите ли так удобно. я не уследил и это художество гуляет уже в нескольких проектах. но работает. а в новом камне с внешней флеш памятью вылезла проблема. -

Алокация строк

jenya7 ответил jenya7 тема в ARM, 32bit

не знаю. у нас все проекты прожигаются во флеш, по крайней мере наш код. в RAM алоцируются только системные функции. -

Алокация строк

jenya7 ответил jenya7 тема в ARM, 32bit

это не указатель на константу? компилятор выделит переменную в RAM? почему нет? во всех кортексах работает. и не только. -

Алокация строк

jenya7 опубликовал тема в ARM, 32bit

есть такая ф-ция char *ToLower(char *str) { int i; for(i = 0; i < strlen(str); i++) { if(str[i]>='A' && str[i]<='Z') str[i]=str[i]+32; } return str; } когда передаю переменную в качестве аргумента во всех контролерах работает без проблем. ToLower(some_string); когда передаю константную строку в качестве аргумента ToLower("WRITE"); в контролерах с внутренней флеш памятью работает без проблем. а в контролерах с внешней флеш памятью (по крайней мере в NXP) компайлер помещает строку во флеш и я соответсвенно получаю void MemManage_Handler(void) { while(1) {} } можно как то какой нибудь прагмой объяснить компайлеру чтоб помещал строку в RAM? -

упс. мой фак. исправил но не помогло. ЮАРТ и у меня работает чики пуки. с ним нет проблем.

-

изначально я работал по системному клоку process(CLK) variable clk_count : integer range 0 to 2 := 0; begin if (SPI_CS = '0') then if (s_ready_read = '1') then if (rising_edge(CLK)) then if (clk3 = '1') then case clk_count is when 0 => buf_in <= DATA_IN(7 downto 4); clk_count := 1; when 1 => buf_in <= DATA_IN(3 downto 0); clk_count := 0; when others => end case; end if; end if; end if; else buf_in <= DATA_IN(7 downto 4); clk_count := 0; end if; end process; та же херня.

-

есть процесс в другом модуле process(CLK) begin if (rising_edge(CLK)) then clk1 <= SPI_CLK; clk2 <= clk1; end if; end process; clk3 <= not clk2 and clk1; SPI_TX_DATA <= sspi_data_out when s_out_select = '0' else data_1553_out; ------------ IN PROCESS ------- when ST_READ_1 => s_out_select <= '1' Bustate <= ST_READ_2; when ST_READ_2 => debug <= X"12"; if (clk3 = '1') then clk2_count := clk2_count + 1; end if; case clk2_count is when 0 => data_1553_out <= DOUT(7 downto 0); when 1 => data_1553_out <= DOUT(7 downto 0); when 2 => data_1553_out <= DOUT(7 downto 0); when 3 => data_1553_out <= DOUT(15 downto 8); when 4 => data_1553_out <= DOUT(15 downto 8); clk2_count := 0; Bustate <= ST_READ_3; when others => end case; а SPI_TX_DATA соединен с DATA_IN честно говоря взыл бы готовый QUAD SPI и не парился ни минуты. забавно что нигде не нашел готовый модуль.

-

top entity получает с PLL 120 мега. но в данном процессе я сижу на SPI Clock.

-

у меня во всех проектах множество локальных variable в процесах. всегда четко работало. DATA_IN : in std_logic_vector(7 downto 0); - сигнал в top entity. он уже выставлен (как видно из сигнал тап). он соединен с сигналом из другого модуля. port map DATA_IN => s_spi_tx_data, а что не так с кодом?

-

Неправильная передача сигнала

jenya7 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

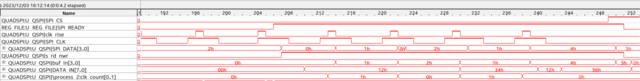

Есть такой процесс SPI_DATA <= buf_in when s_rd_nwr = '1' else "ZZZZ"; process(SPI_CLK) variable clk_count : integer range 0 to 2 := 0; begin if (SPI_CS = '0') then if (s_ready_read = '1') then if (rising_edge(SPI_CLK)) then case clk_count is when 0 => buf_in <= DATA_IN(7 downto 4); clk_count := 1; when 1 => buf_in <= DATA_IN(3 downto 0); clk_count := 0; when others => end case; end if; end if; else buf_in <= DATA_IN(7 downto 4); clk_count := 0; end if; end process; смотрим сигналы когда DATA_IN = 0x12 - buf_in = 0x1 0x2 всё правильно но когда DATA_IN = 0x34 - buf_in = 0x1 0x4 - а должно быть 0x3 0x4 Что не так? -

Вопрос о выборе FPGA

jenya7 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Мне нужен Cyclone 5 5CEFA9F27I7N. Его демо плата довольно дорогая. В то же время демо плата с 5CSEMA4U23C6N или 5CSEBA6U23I7 стоят в три раза меньше. Существенное отличие между последними двумя и тем который мне нужен это SOC on board. Вопрос насколько это важно, нужно ли его активировать или можно работать как с любым другим FPGA? Для апробации я бы взял любой, главное чтоб был дешевле. -

SPI_CS должен работать как асинхронный сброс в ST_IDLE состояние. иначе я останусь в каком нибудь состоянии ожидая следующего клока SPI_CLK. У меня бывали случаи когда моделсим показывал всё хорошо а в реальности не работало и именно сигналтапом я находил проблемы.

-

и поэтому возможен переход 3 -> 22 ? я не описал все состояния но есть и дефолт и рисет.

-

нет ну это дичь какя то when ST_IDLE => debug <= X"F7"; case INSTR is when COM_WRITE => debug <= X"03"; State <= ST_WRITE_1; when others => State <= ST_IDLE; end case; when ST_WRITE_1 => debug <= X"21"; State <= ST_WRITE_2; when ST_WRITE_2 => debug <= X"22"; State <= ST_IDLE; смотрю СигналТап ну как это ? а где 21?

-

у меня уже total memory bits 64% занято. мне вобще то нужно было оставить 50% свободных.

-

спасибо. FIFO пожалуй неплохое решение.

-

Универсальная посылка по UART.

jenya7 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Сегодня я просто посылаю определённое количество байт из одного модуля. UART_TX: process(CLK) variable tx_idx : integer range 0 to 255 := 0; variable del : integer range 0 to 255 := 0; begin if (rising_edge(CLK)) then case UartTxState is when ST_IDLE => tx_idx := 0; del := 0; if (TX_GO = '1') then tx_count <= tx_count + '1'; rx_count_ret <= rx_count; UartTxState <= ST_TX_DATA; end if; when ST_TX_DATA => del := 0; if (TX_RDY = '1') then case tx_idx is when 0 => tx_data_buf <= X"AA"; when 1 => tx_data_buf <= X"77"; when 2 => tx_data_buf <= tx_count(7 downto 0); when 3 => tx_data_buf <= tx_count(15 downto 8); --------------------------------------------- when 223 => tx_data_buf <= tx_chksum(7 downto 0); when 224 => tx_data_buf <= tx_chksum(15 downto 8); when others => UartTxState <= ST_IDLE; end case; UartTxState <= ST_TX_TRIG; when ST_TX_TRIG => if (TX_RDY = '1') then TX_TRIG <= '1'; UartTxState <= ST_NEXT_1; end if; when ST_NEXT_1 => if (TX_RDY = '0') then UartTxState <= ST_NEXT_2; end if; when ST_NEXT_2 => TX_TRIG <= '0'; tx_idx := tx_idx + 1; if (tx_idx > 224) then UartTxState <= ST_IDLE; else UartTxState <= ST_TX_DATA; end if; when others => UartTxState <= ST_IDLE; end case; end if; end process UART_TX; А как сделать универсальную посылку? Чтоб можно было посылать из любого модуля любое количество байт. -

странная проблема оказалась. иногда застревал в этом состоянии when ST_READ_2 => debug <= X"04"; if (clk3 = '1') then clk_count := clk_count + 1; if (clk_count = 2) then State <= ST_READ_3; end if; end if; if (SPI_CS = '1') then State <= ST_IDLE; end if; пришлось переписать when ST_READ_2 => debug <= X"04"; if (SPI_CS = '1') then State <= ST_IDLE; else if (clk3 = '1') then clk_count := clk_count + 1; if (clk_count = 2) then State <= ST_READ_3; end if; end if; end if; хотя не такая уж странная. явный косяк. и всё таки даже сейчас раз в 4000 - 80000 обращений одно ломается. правда последующие отрабатываются нормально до следующей поломки.