BSACPLD

Свой-

Постов

863 -

Зарегистрирован

-

Посещение

-

Победитель дней

3

Весь контент BSACPLD

-

Коллеги, мне тут отладка от Alinx наконец приехала. Начал изучать. Поставил PDS, запустил, и не обнаружил IP для PCIe. Только элементарные IP блоки типа BRAM, PLL, и т.д. Подскажите, пожалуйста, как правильно добавлять PCIe в проект. Или может быть где-то можно посмотреть готовый пример под PCIe?

-

Тут смотря что Вам нужно. Решить локальную задачу - готовый вполне подходит. Задел на будущее возможной с миграцией с одного производителя на другого - однозначно все свое либо в исходниках. У меня проект по ходу введения санкций прошел путь Intel/Lattice->Xilinx-Fudan. Сейчас смотрю в сторону PangoMicro - уж больно цена у них привлекательная.

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

Strap пины это лишь часть конфигурации. Доступ по MDIO всё равно нужен. Кстати, почему не готовый модуль MAC/MDIO? Я в своё время писал и MAC и MDIO контроллер (до сих пор ставлю их в свои проекты), но пока я оттестировал и закончил сбор и исправление всех багов, прошло явно больше года.

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

CAST JPEG-E

BSACPLD ответил BSACPLD тема в Работаем с ПЛИС, области применения, выбор

Удалось заставить работать 🙂 Взял JPEG заголовок от цветного JPEG для RTP MJPEG и выпилил из него DQT и две DHT таблицы относящиеся к CbCr составляющим, поправил маркеры с цветовыми компонентами и все заработало 🙂 В итоге получился вот такой заголовок: FF D8 FF E0 00 10 4A 46 49 46 00 01 01 00 00 01 00 01 00 00 FF DB 00 43 00 02 01 01 02 01 01 02 02 02 02 02 02 02 02 03 05 03 03 03 03 03 06 04 04 03 05 07 06 07 07 07 06 07 07 08 09 0B 09 08 08 0A 08 07 07 0A 0D 0A 0A 0B 0C 0C 0C 0C 07 09 0E 0F 0D 0C 0E 0B 0C 0C 0C FF C0 00 0B 08 02 58 03 20 01 01 11 00 FF C4 00 1F 00 00 01 05 01 01 01 01 01 01 00 00 00 00 00 00 00 00 01 02 03 04 05 06 07 08 09 0A 0B FF C4 00 B5 10 00 02 01 03 03 02 04 03 05 05 04 04 00 00 01 7D 01 02 03 00 04 11 05 12 21 31 41 06 13 51 61 07 22 71 14 32 81 91 A1 08 23 42 B1 C1 15 52 D1 F0 24 33 62 72 82 09 0A 16 17 18 19 1A 25 26 27 28 29 2A 34 35 36 37 38 39 3A 43 44 45 46 47 48 49 4A 53 54 55 56 57 58 59 5A 63 64 65 66 67 68 69 6A 73 74 75 76 77 78 79 7A 83 84 85 86 87 88 89 8A 92 93 94 95 96 97 98 99 9A A2 A3 A4 A5 A6 A7 A8 A9 AA B2 B3 B4 B5 B6 B7 B8 B9 BA C2 C3 C4 C5 C6 C7 C8 C9 CA D2 D3 D4 D5 D6 D7 D8 D9 DA E1 E2 E3 E4 E5 E6 E7 E8 E9 EA F1 F2 F3 F4 F5 F6 F7 F8 F9 FA FF DA 00 08 01 01 00 00 3F 00 FF D9 Правда пришлось ещё немного подправить RTP MJPEG под Grayscale, но эта небольшая несовместимость со стандартом на моём кастомном плеере позволила поднять FPS до 50 при разрешении 2К (было 30 FPS) 🙂 -

CAST JPEG-E

BSACPLD ответил BSACPLD тема в Работаем с ПЛИС, области применения, выбор

Заголовок вот такой: FF D8 FF E0 00 10 4A 46 49 46 00 01 01 02 00 1C 00 1C 00 00 FF DB 00 43 00 03 02 02 02 02 02 03 02 02 02 03 03 03 03 04 06 04 04 04 04 04 08 06 06 05 06 09 08 0A 0A 09 08 09 09 0A 0C 0F 0C 0A 0B 0E 0B 09 09 0D 11 0D 0E 0F 10 10 11 10 0A 0C 12 13 12 10 13 0F 10 10 10 FF C0 00 0B 08 02 58 03 20 01 01 11 00 FF C4 00 1C 00 00 02 03 01 01 01 01 00 00 00 00 00 00 00 00 00 03 04 02 05 06 00 01 07 08 FF C4 00 51 10 00 01 03 02 03 05 06 02 06 08 04 04 04 05 02 07 02 03 04 12 00 01 05 13 22 11 21 31 32 42 06 14 23 41 52 62 51 72 24 33 61 71 81 82 07 15 43 91 92 A2 B2 C2 A1 B1 C1 D2 16 34 53 D1 63 73 E2 F0 08 25 E1 F1 F2 17 44 54 64 35 83 45 74 A3 FF DA 00 08 01 01 00 00 3F 00 FF D9 Это то, что я записываю в кодек в качестве конфига. -

CAST JPEG-E

BSACPLD ответил BSACPLD тема в Работаем с ПЛИС, области применения, выбор

И вот спустя столько лет я вновь вернулся к этому кодеку... Для экономии ресурсов решил перевести его в монохромный режим - сенсор все равно монохромный. До этого был YCbCr и все прекрасно работает уже много лет. Сконвертировал цветной BMP файл в монохромный JPEG с помощью утилиты convert в Linux. Открыл файл hex редактором и извлёк из него заголовок. Записываю данный заголовок как и раньше для YCbCr варианта, подаю сырые данные. И... Кодек зависает на определенном участке картинки - на вход данные поступают, на выходе тишина. Пробовал с разными тестовыми паттернами на входе - в зависимости от диапазона чисел на входе либо отрабатывает картинку полностью, либо зависает. Что данные корректно приходят на вход кодека я проверил - количество пикселей строго равно Height*Width. Что я делаю не так? -

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

А вот это большая ошибка. Дефолтные конфиги у 88E1111 мягко говоря кривые. Его обязательно нужно правильно сконфигурировать по MDIO чтобы он корректно работал.

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

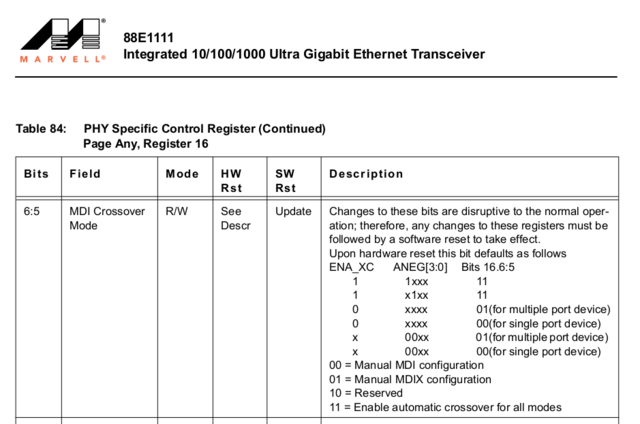

Не вводите людей в заблуждение. 88E1111 прекрасно работает как с прямым, так и с кросс кабелем. Вот пример правильной инициализации 88E1111 для RGMII: case PHY_ID_88E1111: { MDIO_PHY_ADDR = PHY_ADDR_88E1111 ; uint16_t data ; data = rd_mdio (0) ; data |= ((1<<12) | (1<<8)) ; data &= ~((1<<14) | (1<<11) | (1<<10)) ; wr_mdio (0, data) ; data = rd_mdio (4) ; data |= ((1<<8) | (1<<6)) ; data &= ~((1<<10) | (1<<7) | (1<<5)) ; wr_mdio (4, data) ; data = rd_mdio (9) ; data |= ((1<<9)) ; data &= ~((1<<15) | (1<<14) | (1<<13) | (1<<8)) ; wr_mdio (9, data) ; data = rd_mdio (16) ; data |= ((1<<15) | (1<<14) | (1<<13) | (1<<12) | (1<<6) | (1<<5)) ; data &= ~((1<<4)) ; wr_mdio (16, data) ; data = rd_mdio (27) ; data &= ~((1<<3) | (1<<2) | (1<<1) | (1<<0)) ; data |= ((1<<3) | (0<<2) | (1<<1) | (1<<0)) ; wr_mdio (27, data) ; data = rd_mdio (20) ; data &= ~((1<<7) | (1<<1)) ; data |= ((1<<7) | (1<<1)) ; wr_mdio (20, data) ; data = rd_mdio (29) ; data &= ~0x001F ; data |= 16 ; wr_mdio (29, data) ; data = rd_mdio (30) ; data |= ((1<<0)) ; wr_mdio (30, data) ; data = rd_mdio (0) ; data |= ((1<<15)) ; wr_mdio (0, data) ; __delay_cycles (const20ms) ; poll_speed = false ; mac_config = (LINK_AUTO<<ETH1000_SPEEDSEL0) | (0<<ETH1000_MACFLTDISABLE) | (1<<ETH1000_TXGENERATEIPV4) | (1<<ETH1000_RXCHECKIPV4) | (1<<ETH1000_RXUFENABLE) | (0<<ETH1000_RXMFENABLE) | (1<<ETH1000_RXBFENABLE) ; break ; }

- 10 ответов

-

- ethernet

- fpga kintex-7

-

(и ещё 3 )

C тегом:

-

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Коллеги, платы отгружены в Эпсилон в количестве 10 шт. По вопросам приобретения/аренды - прошу обращаться напрямую в Эпсилон. Технические вопросы можете задавать мне здесь напрямую или в личку. -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

В последней версии Procise появилось что-то вроде AXI Memory Mapped To PCI Express? Или как и раньше голый PCIe? Я Vivado использовал как раз из-за необходимости этого IP + поддержка SV. -

UPD. Если перенастроить на OPP0/OPN0, то все работает... Походу какой-то баг в самом чипе...

- 1 ответ

-

- 1

-

-

Коллеги, использовал ли кто-нибудь встроенный OPA в CH32V003? Я попробовал включить его по схеме неинвертирующего усилителя. Настроил следующим образом: void OPA_INIT (void) { GPIO_InitTypeDef GPIO_InitStructure = {0} ; OPA_InitTypeDef OPA_InitStructure = {0} ; RCC_APB2PeriphClockCmd (RCC_APB2Periph_GPIOD, ENABLE) ; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING ; GPIO_Init (GPIOD, &GPIO_InitStructure) ; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING ; GPIO_Init (GPIOD, &GPIO_InitStructure) ; GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4 ; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AIN ; GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz ; GPIO_Init (GPIOD, &GPIO_InitStructure) ; OPA_InitStructure.PSEL = CHP1 ; OPA_InitStructure.NSEL = CHN1 ; OPA_Init (&OPA_InitStructure) ; OPA_Cmd (ENABLE) ; } ОС 10к/43к, КУ = 5.3. Для входного напряжения 0.5В на выходе должно быть 2.65В, а по факту там 0 или VCC в зависимости от входного напряжения. Как будто это не усилитель, а компаратор... Хотя в datasheet написано именно OPA.

-

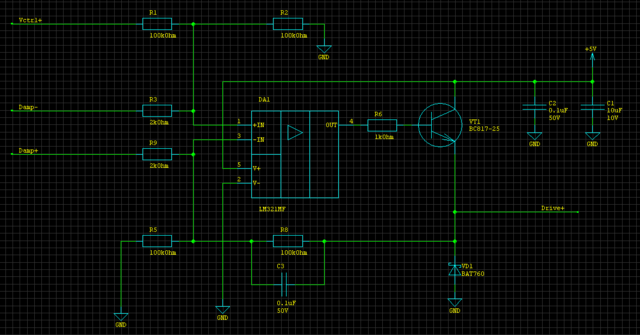

Коллеги, я сейчас тоже пытаюсь сделать схему управления DC IRIS. Сделал схему на ОУ с обратной связью от Damp. При начале увеличения напряжения диафрагма не двигается. После определённого уровня напряжения диафрагма начинает плавно открываться и уходит в полностью открытое положение. Чтобы закрыть приходится снижать напряжение значительно ниже чем нужно для открытия. Иными словами у меня получилось плавное открытие/закрытие с некоторым гистерезисом вместо плавного регулирования. Если оторвать обратную связь по Damp, то диафрагма открывается/закрывается намного быстрее, т.е. обратная связь все же как-то работает, но неправильно. Можете подсказать, где у меня в схеме ошибка? Или может быть у кого-нибудь есть рабочая схема?

-

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Тьфу-тьфу, на Fudan ничего подобного не замечал... Хотя Pango уж очень привлекательны с точки зрения цены по сравнению с Fudan. В 4 раза дешевле аналогичной ёмкости... -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

А какие именно подводные камни? -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Их просто нельзя использовать чисто из Vivado. Требуется связка с Procise по очень кривому маршруту. Все потому, что Fudan сделали клон Artix-7 приделав к нему трансиверы от Kintex-7. Vivado про это естественно не знает. -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Платы в количестве 10 шт. готовы. Сейчас готовим упаковку, после 13 октября планируем отгрузить в Эпсилон. -

Альтернатива Резониту

BSACPLD ответил BSACPLD тема в Пайка и монтаж

Спасибо за развернутый ответ 🙂 -

Альтернатива Резониту

BSACPLD ответил BSACPLD тема в Пайка и монтаж

Запас есть. 10-15% на пассив, 1-3 шт. на микросхемы, дорогие микросхемы (ПЛИС, матрицы) без запаса. VIA под QFN делать залитыми или без разницы? -

Альтернатива Резониту

BSACPLD ответил BSACPLD тема в Пайка и монтаж

Требуют комплектацию только в виде целых катушек. У нас часть комплектации это обрезки. Иногда большие, иногда всего 5 см 😞 -

Альтернатива Резониту

BSACPLD опубликовал тема в Пайка и монтаж

Добрый день, коллеги. Резонит сейчас отписался, что приостановил приём заказов на монтаж печатных плат в связи с переездом на новую производственную площадку. В связи с этим возникла необходимость в поиске альтернативных вариантов по монтажу печатных плат. Какие компании можете посоветовать? Платы у нас средней сложности: 1-2 BGA и обвязка 0402/0603. Комплектация давальческая с запасом 10-15%. -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

VPN + фейковый аккаунт на студента M.I.T. решает проблему 🙂 Почта с 10 minute mail прокатывает. -

FMQL45T900 это клон Zynq?

-

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Забыл ещё написать. Если будут вопросы по работе с Fudan на данной отладочной плате, можно обращаться за помощью ко мне напрямую.