Bear_ku

Свой-

Постов

189 -

Зарегистрирован

-

Посещение

Весь контент Bear_ku

-

Может ничего и не случится, только зачем вам понадобился такой финт ушами? Стандартные средства чем не угодили?

-

У меня такое было при черном цвете Drill Holes. Заменил на серый, проблема ушла.

-

Не в курсе как это сделать стандартными средствами, но можно использовать дополнительные надстройки, в частности Assign Net to Via.

-

Придерживаюсь направления: один компонент, одно посадочное место. Правда при этом появляется один неприятный момент: в BOM идет одна позиция с названием устанавливаемого модуля и приходится уже вручную добавлять нужные элементы. Модуль .mdd можно вручную подгружать при разводке, без каких-либо дополнительных манипуляций на схеме.

-

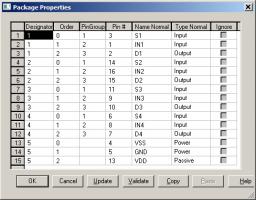

Добрый день. Для элемента содержащего несколько однотипных вентилей, хочу пользоваться функцией swap pin / function или чем-то подобным. Т.е. при замене одной ножки вентиля на другой в PCB Editor, надо чтобы соответственно заменялись и все остальные ножки. Что имеется на данный момент: создал элемент, ADG511 - heterogeneous. 4 части это ключи и пятая питание. На картинках показаны установленные свойства + добавлен параметр SWAP_INFO = (S1, S2, S3, S4) В итоге замена однотипных ножек возможна, но по отдельности. Что-то можно сделать что-бы получить желаемый результат?

-

Drawing Editot

Bear_ku ответил nxn тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Не в курсе какие функции от Autocad вам надо, но можете попробовать его бесплатный аналог nanoCAD. Монстром он точно не является ) -

Как разводить на плате BGA 1 мм

Bear_ku ответил 24mi тема в Работаем с трассировкой

Меня мало волнует какие герберы они используют, главное что проблем с конечным продуктом нет. -

Как разводить на плате BGA 1 мм

Bear_ku ответил 24mi тема в Работаем с трассировкой

Например, в моем случае, никого этот слой не волнует, трафарет делается под конкретную машину по тем же герберам, что отдаются на производство ПП. -

Можно сделать вариантные исполнения, в каждом из которых присутствуют только нужные элементы. При этом на формирование нужного сборочного чертежа уйдут секунды.

-

У меня тоже есть пара вопросов, на эту (похожую) тему: можно как-то сделать проверку трассировки с учетом слоя Ncroute_Path? или нарисовав сложную фигуру в этом слое линиями, все равно надо отдельно прорисовывать слои запрета установки элементов и разводки? На данный момент вообще не пользуюсь генерацией файла фрезеровки, на производство отсылаю гербер слоя Board с нужными контурами вырезов. Они сами решают какой фрезой добиться требуемых размеров (делаем все в КЭБ). Такой подход подойдет для других предприятий или вы сталкивались с тем, что требуют именно файл фрезеровки?

-

Трассировка (нужна консультация)

Bear_ku ответил uzzzer тема в P-CAD 200x howto

Можно поставить резисторы в соединение с землей http://www.atis-wdu.ru/docs/RS-485_2.pdf. -

Трассировка (нужна консультация)

Bear_ku ответил uzzzer тема в P-CAD 200x howto

Отсутствие соединения земли может привести к выходу микросхемы из строя. Видел подобное. Т.к. при этом может быть превышено максимально допустимое напряжение на A и B (-8V to +12.5V). Еще, как вариант, может быть проблема в работе самого интерфейса, т.е. в один прекрасный момент оба устройства переходят в режим передачи и побеждает МОХА ) И не стоит, конечно, экономить на защите: http://www.bourns.com/data/global/pdfs/Bou...485_AppNote.pdf . И у меня тоже вопрос возник, может не много не по теме: а как себя чувствует терминатор 110 Ом 0603, на сколько я понимаю допустимая мощность на нем может быть легко превышена? -

Сам не пользовался, но в PCB Editor есть функция File->Export->Fabmaster out. У меня OrCAD 16.6 SP29 лицензия Allegro PCB Designer (was Perfomance L). Если у вас нет этой функции можете выложить свой проект или отправить на почту. И можете еще попробовать в консоли PCB Editor написать команду "fabmaster out".

-

Сам создаю в pcb editor только нестандартные корпуса, все остальное делаю в сторонних программах (LP Wizard, Library Expert). Быстро и удобно. За отображение номеров выводов отвечает слой "Package Geometry -> Pin_Number".

-

Полно схем на специализированных микросхемах без ОС, без встроенной защиты от КЗ и т.п. Чем же МК хуже?

-

Эм-м-м, может я ошибаюсь, но скорее всего вы знаете о МК только по наслышке. О каком времени выполнения команды в МК вы говорите? даже при тактовой 16Мгц одна команда выполняется примерно за 60нс, вы считаете что это много? ШИМ на современных контроллерах вообще не требует участия процессора. Время реации на прерывание тоже сотни нс - ерунда. И почему коэффициент заполнения не связан с КПД, если от него зависят потери в реактивных/полупроводниковых элементах?

-

Еще раз спасибо. Такой вариант в голову не приходил.

-

Благодарю. Этот способ удобнее ) На сколько я знаю, в полигонах задается minimum gap, т.е. минимальный зазор между краями. А что означает maximum gap в данном случае? Ставил от 0.1мм до 10мм, никакой разницы не заметил.

-

Столкнулся со следующей проблемой при использовании Z-copy: периодически не получается создать полигон, по заранее нарисованному контуру т.к. он (контур) не является замкнутым. На данный момент просто удаляю часть линий и рисую их заново, при этом приходится использовать "snap pick to -> segment vertex". Можно ли как-то по другому объединить две и более линий в одну?

-

Ну у меня в win7 перестал работать PSpice.

-

The operators new and delete are not implemented, attempting to use them will cause the linker to complain about undefined external references. - это для GCC, а точнее winavr-20100110. Смотрите описание на используемый вами компилятор. И если не ошибаюсь, операторов new и delete нет в Си, это С++. Используйте malloc(), realloc(), calloc(), free().

-

На счет вырезов. Заданы ограничения: расстояние между любыми элементами двух цепей не менее 2.5мм. В месте где этот зазор выдержать не получается, сделан 1мм паз, которого вполне достаточно. Но при этом полигоны подчиняясь заданному правилу заливаться не хотят. Вопрос в том, как правильнее в данной области отойти от заданного ограничения? На счет шелкографии. Пазы на плате выполнены под элементами, при этом на них попадают части шелкографии. При формировании слоя автошелкографии, а в дальнейшем герберов линии будут проходить через паз. На сколько я понимаю, это не есть правильно. Или это уже проблемы производства?

-

На плате необходимо сделать вырезы. Как при этом объяснить PCB Editor-у что в этих местах можно не соблюдать заданные для цепи ограничения? делать регионы? И как учесть их при автоматическом формировании слоев шелкографии? На данный момент прорисовываю контуры пазов в слое Board Geometry \ Ncroute_Path.