-

Постов

3 014 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные EvilWrecker

-

-

6 minutes ago, dmitry-tomsk said:

Разреженная(?) матрица, начало планирования, никакой разводки не видно, как и невероятного планинга- что же конкретно показывает эта картинка?

-

1 minute ago, peshkoff said:

сразу видно человек этого не делал ни разу

+1

-

-

15 minutes ago, vitus_strom said:

FPGA от Xilinx или Intel справились бы

Это само собой разумеющийся факт, но нужно напрямую- одно в другое.

-

Здравствуйте,

Есть бакплейн разработанный сторонними лицами в котором:

- много 10GBASE-KR/KX4

- нужно несколько таких каналов вывести во внешний мир

Хотелось бы оптикой, но на худой конец рассмотрю медь: интересуют свежие(не старее 15-16 года выпуска) PHY как минимум на один канал, сугубо уровня Broadcom/Marvell/Intel и пр. Знает ли кто-либо такие? -

On 9/24/2019 at 12:41 PM, Volkov said:

Есть еще отдельный документ для memory down с ECC. И в нем те же картинки, и те же рекомендации. Так что я не думаю что они ошиблись, и теперь плодят ошибку в разных документах.

Не могу с этим согласиться

Повторяющиеся ошибки(в том числе противоречащие "сути гайда") я сам несколько раз находил и с ними же обсуждал, но что касается именно картинки/соединения из документа то:

Повторяющиеся ошибки(в том числе противоречащие "сути гайда") я сам несколько раз находил и с ними же обсуждал, но что касается именно картинки/соединения из документа то:

- более менее значимое влияние на сигнал(если все остальное сделано правильно) видел только для memory down dual-rank.По роду деятельности в основном занимаюсь именно memory down дизайнами(от двух ранков), соответственно не видел руинящего влияния длины трассы до терминатора

- в то же самое время мне совершенно непонятна топология с картинки, как это выглядит на плате

- на приведенных скриншотах с гиперлинкса в первом случае можно сказать что влияния и нет, а в случае второго "проблемы"(не самая лучшая форма сигнала, хотя по compliance kit пройдет видимо) в другом месте

С отпуска вернусь, попробую найти этот документ на стороне авторов

-

6 minutes ago, SergeySoG said:

Эти косяки я исправил

И самую правую часть с группой виа?

-

24 minutes ago, SergeySoG said:

Можно поподробнее из-за чего надо всё переделывать заново?

По порядку:

24 minutes ago, SergeySoG said:У меня трассы 0,1, зазор в паре 0,12, расстояние до референса 63мкм. Зазор между парами 0,25. Все пары выравнены на одном слое. Даже еслди в расстояниях от референса считать то зазор большой.

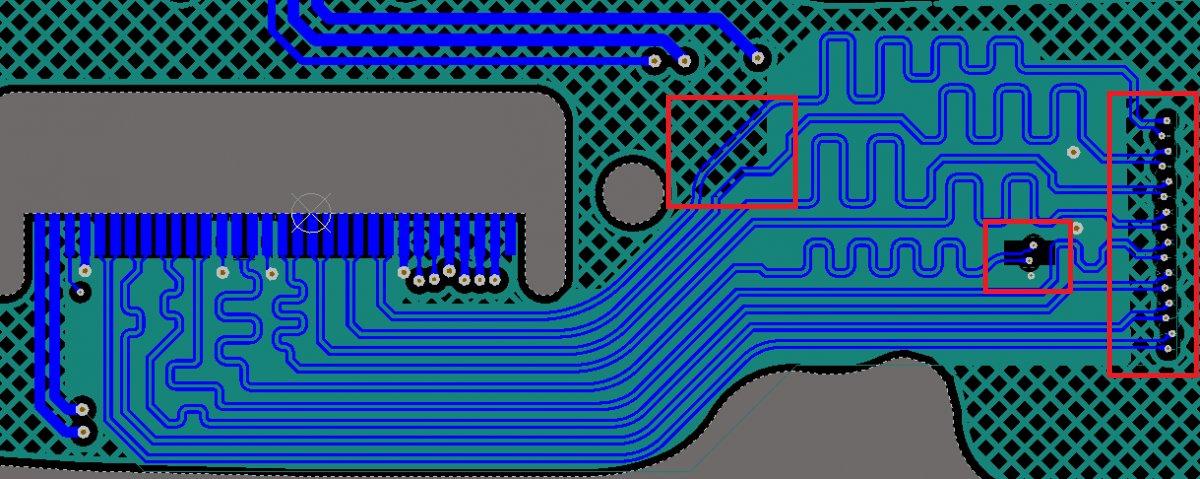

Здесь картинка многое проясняет- сомнительные участки обведены(см.вложение) но в остальном что цитируется я беру свои слова назд- неправильно интерпретировал изображение в ряде мест. С указанными числами зазор между парами вполне ок.

24 minutes ago, SergeySoG said:Полигон сеткой потому что плата гибкая из полиимида, под дифпарами залита сплошная земля, сетка только в остальной области где нет хайспидов, переходные в дифпарах microvia прямо на площадки коннекторов,под коннекторами и via антипады сделаны.

Вы тогда сразу говорите что у вас high-speed over flex+HDI

, это сразу бы многое прояснило.

24 minutes ago, SergeySoG said:

, это сразу бы многое прояснило.

24 minutes ago, SergeySoG said:То есть получается что спейсинги везде нормальные, параметры пары посчитаны, антипады есть, земдя нигде не рвётся - что не так то?

Ну и я бы это дело от краев полигона чуть дальше задвинул внутрь, особенно в нижней части картинки -

7 minutes ago, SergeySoG said:

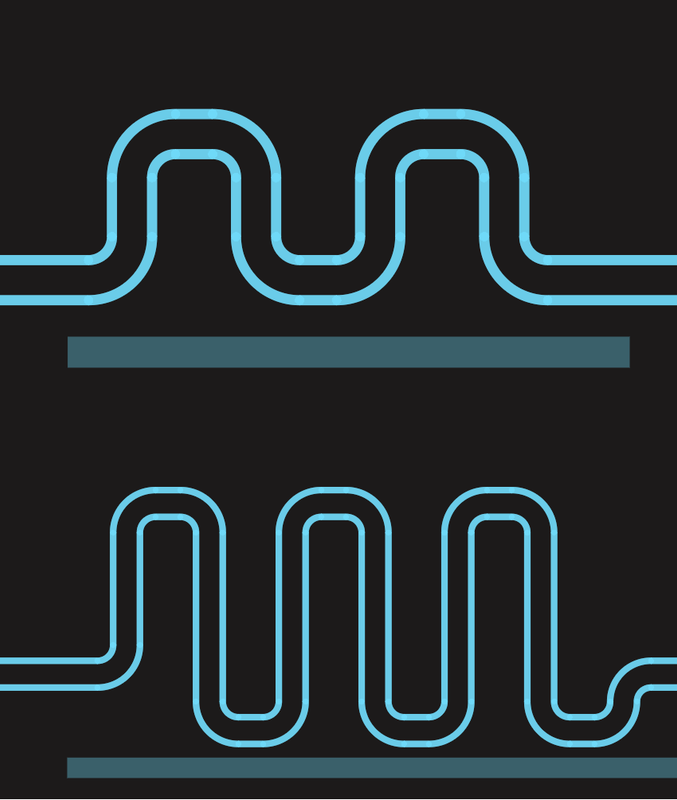

Только если места не очень много между проводниками надо правильно начальные параметры меандра подбирать, а то совсем отказывается меандр размещать

Сугубо опытным путем исходя из реалий дизайна, +возможно отключив на время clip to traget length, а так метод прост- таргет определили, дальше поджимаете проводник вплотную(с нормальным зазоров естественно) к таргету, чтобы он его огибал без свободных островов, после чего размазываете выравнивание по этому проводнику равномерно(либо максимально заполняете выравниванием пустой остров при наличии такового). После повторяете для оставшихся трасс в том же порядке- получится компактная структура

-

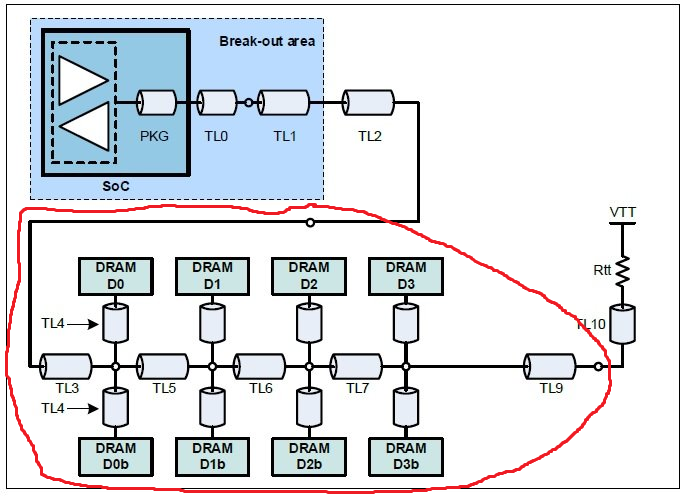

Значит это судя по всему разводка "планка на топе, сразу под ней планка на боттоме", без зеркалирования но с подводом типа такого

И смотря на то как подписаны TL на картинке есть стойкое ощущение чтоQuoteIntel strongly recommends routing DRAM loaded sections — TL5, TL6, TL7, TL9 and TL10 — the same length between command signals and their corresponding clock signals. Все Loaded секции.У JEDEC есть только требования к минимальной длине TL9 , TL10.

проблемам именно в ней, т.е. подписаны не те сегменты, т.е. должно быть что-то такое(с пропуском TL9,TL10)

иначе как тогда следуя этому же гайду возможны такие цифры?22 minutes ago, Volkov said:TL5 - TL7 - виа ту виа сегмнет между чипами памяти, минимум 450 мил макс. 750 мил. TL9 - макс 500 мил TL10 - макс 100 мил.

-

57 minutes ago, peshkoff said:

Оч интересно. да, действительною, сейчас так и есть.

видимо я новые версии на предмет выравнивания дифф пар не штудировал ввиду нереальных тормозов операции.

Оно и в старых так работает на самом деле- что касается тормозов, понятно о чем речь, там может помочь уже тромбом сделанный рисованием

38 minutes ago, SergeySoG said:

38 minutes ago, SergeySoG said:И тогда уж по теме ещё спрошу что бы удостовериться, вот рекомендации от TI для трассировки Display Port. Интересен пункт 3, гнуть под 45 градусов потому что так меньше изменяется ширина проводника.

Это все полная туфта потому что любые траски в кадах это траектория описанная окружностью, там нет никаких прямых углов которые бы давали прирост толщины(т.к. скругление на повороте). Другое дело как часто и в какой последовательности повторяются повороты- чтобы голову над этим не ломать можно местами применить rules of thumb. Далее:

- "отступ в хайпсидах" надо считать не в ширинах трассы, а по расстоянию от референса

- никакие полигоны сеткой тут не нужны

- земляные трассы тем более

- нужны возвратные виа с переходом на слой и антипад нормальный

- нужны нормальные спейсинги между парами и другими проводниками

Текущую разводку можете смело переделывать с нуля

-

-

10 minutes ago, dee2mon said:

Не могу не похвастаться небольшой методичкой, посвященной особенностями ВЧ-разводки в Altium, написанной для наших студентов. Она написана для AD17, сейчас потихоньку переводится на AD19.Работа с ВЧ-объектами_v2.pdf

Хорошая методичка, правильно написана- удивлен прямо(без сарказма). В плане именно псб дизайна конечно есть вопросы(стартуя с темы термалов в вч, и тем более используемых в примере), плюс не раскрыты возможности магии привязок и рисования на механике- а так все на хорошем уровне.

-

21 minutes ago, Volkov said:

TL3 - это neck-down. Документ под НДА, да и там особо нет ничего такого интересного.

Насколько можно понять это 100% не DIMM а memory down, поскольку такое не может быть для планки

Есть ли скриншот топологии реальной, не из секретного документа? Если TL3 это neck, то что тогда TL4 и далее? TL4 везде одинакова для вех ветвей, верно? Это мультиранковая система или нет(не понимаю нейминги сигналов)? -

4 minutes ago, peshkoff said:

для диф пары не поможет

верней не так. оно поможет, но только для размещения змейки с одной стороны.

Так именно это же и просят- выравнивание с одной стороны для диффпары, не?

5 minutes ago, peshkoff said:Для сингла можно поставить препятствие и змейку можно получить несимметричную.

Не понял о чем речь, можно поподробнее?

-

3 hours ago, SergeySoG said:

Может ли альтиум ровнять пары так что бы сегменты змейки были только на одну сторону пары, то есть вот так как в Allegro.

Там в 17.1 нет галки типа centered и пока еще нет рамки именно для диффпары- говоря про сноровку о которой уже упомянули, попробуйте поставить искусственное препятствие(медное) с другой стороны, 100% поможет

-

2 minutes ago, peshkoff said:

Скорее всего получите контур меди, то нужно выделить замкнутый контур, tools-Convert-region. и ему присваиваете цепь

Да, нужен обязательно замкнутый контур+ удаление мусорных трасс("точки" в соединениях треков) если такое генерируется в процессе.

2 minutes ago, Aner said:DXF обеспечит только геометрию топологии, он не привязан к схематике.

Верно.

2 minutes ago, Aner said:Ппривязать к цепям в Альтии не просто, компонент делать в либе нужно.

Либа тоже не всегда поможет если есть участки аля "кз между сигналом и землей", как это видится системой

-

Если арок много то скорее всего на этом и погорел имопрт- по поводу DXF, экпортируйте контур из ансиса, далее импортируйте на плату в альтиуме, после заливайте регионами(если версия от 18), либо полигонами с конвертацией в регионы(если до 18, соответственно нужно настроить аппроксимацию арок сначала). Если повторяющиеся блоки и/или предполагается реюз можно проект ансиса разбить на функциональные блоки и оформить как отдельные футпринты, а потом уже склеивать на плате

-

20 minutes ago, Александр Мылов said:

Пробовал через гербер, последовательность ясна, но не работает.

Нужен совет кто реально получал результат

У меня пока не клеится

Из какого софта пытаетесь воткнуть блок и в каком виде? Наиболее простой и 100% путь это DXF. Касаемо герберов, при наличии в топологии арок можно пролететь с качеством в некоторых ситуациях т.к. может произойти зверское разбиение на сегменты.

-

2 hours ago, Uree said:

Загадочное что-то... почему TL2/TL3 и TL9/TL10 отдельные линии и что означают точки между ними? К чему конкретно относится эта топология(несколько чипов по разным сторонам платы, планка памяти в разъеме с внешней терминацией?!, что-то еще)? Интересно было бы услышать хоть какой-то намек на обоснование этой рекомендации.

Присоединяюсь к вопросу- на дуалранк не тянет(один терминатор), на кламшелл тоже, плюс вроде как показаны биты(???)- что за документ? Есть полная ссылка или один из NDA-protected?

-

6 minutes ago, AndreyTrundov said:

Вот вы и выдали заказчика :) Отлично, Василий! Спасибо, Василий! (Без сарказма).

@Vasily_полагаю речь о вас идет- как вам "заказ"?

Сколько трилиардов мне заплатили за посты?

8 minutes ago, AndreyTrundov said:

Сколько трилиардов мне заплатили за посты?

8 minutes ago, AndreyTrundov said:А Василий, если я был не прав, запросто мог бы закрыть мой "суперспамный аккаунт" без возможности восстановления.

И ждать моего ухода не пришлось бы.

Ну в поспамьте еще, может модераторы и сподобятся- по правде говоря здесь не банили до последнего таких, до которых далеко даже вам

9 minutes ago, AndreyTrundov said:

9 minutes ago, AndreyTrundov said:А спамите Вы, мой друг.

Вовсе нет- перечитайте еще раз предыдущий пост. И еще раз, я вам не друг, к нашему обоюдному счастью

11 minutes ago, AndreyTrundov said:

11 minutes ago, AndreyTrundov said:За день столько писем не получал от одного персонажа ). Да еще и с каринками.

Дык радуйтесь, сейчас еще будут

12 minutes ago, AndreyTrundov said:попросили его, видите ли, разобраться, оценить )))

Именно так, плюс персональное желание прокомментировать ваши сказки- и поверьте, смешно не только вам

-

1 minute ago, AndreyTrundov said:

Я не ругал чьи то книги, и свои вовсе не нахваливаю, что вы :)

Насчет ругательств ничего не могу возразить(пока или уже), а что насчет нахваливания- конкретно на этом форуме вы их спамите, уверяя что "поможет/полегчает"

QuoteСпасибо модератору Василию за то, что выгнал меня с форума за рекламу моих книг, в которых я очень подробно и доступно попытался поделиться знаниями и практическими наработками в этой области. Повторю, читайте книги, в том числе мои.

Модератору Василию респекты(без сарказма), но вы не торопитесь уходить

5 minutes ago, AndreyTrundov said:Раньше меня удивляло такое отношение Гуру, Своих и прочих "компетентных" в верстке специалистов, и то, что ни слова по теме. Сейчас уже не удивляет.

Если у вас нету внятных контраргументов для предыдущего поста, то возможно они найдутся на следующие

Как я и говорил, прокомментированы будут как минимум все картинки из отзыва с финалом в виде слезно-драматичного усб.

Как я и говорил, прокомментированы будут как минимум все картинки из отзыва с финалом в виде слезно-драматичного усб.

-

4 minutes ago, Flood said:

А так получается - все вокруг дураки, я д'Артаньян, а почему так вышло - не мое дело.

Не могу согласиться с вами

Смотрите:

Смотрите:

- нигде на форуме я не предлагаю свои услуги и ничего не продаю

- нигде никому не тыкаю в лицо "дипломами-регалиями", а даже наоборот, прямо пишу что

Quote...являюсь самым обычным псб-крестьянином

- нигде не продвигаю свои дизайны, наработки и пр. в том же духе.

Соответственно никакого дартаньянства нет и в помине. Что касается:7 minutes ago, Flood said:На мой взгляд, главный минус ваших разоблачений - отсутствие положительных контр-примеров, как сияющего дзена собственной трассировки, так и ссылок на хорошие источники.

Тут также не могу согласиться- ссылки на хорошие источники как раз и приводятся, а информация которая там содержится на мой взгляд исчерпывающая в заданном контексте обсуждений. Что касается дзена личных разработок, у меня нет ни желания ни мотивации продвигать свои дизайны за счет критики других

-

2 minutes ago, Flood said:

не то просто растровые с низким разрешением формулы и битые символы в описаниях к ним. Возможно, это артефакт html-предпросмотра, но разбираться где смысл, где опечатка, а где побилось из-за преобразования - как-то не хочется. Лучше уж никакого предпросмотра, чем такой. Не знаю, как там дела в pdf, но вряд-ли намного лучше.

В пдф дела еще хуже

Altium vs Mentor

в Разрабатываем ПП в САПР - PCB development

Опубликовано · Пожаловаться

Я такой ерунды как у вас не держу - но правильно ли я понимаю, этим переводом стрелок и переходом на "ты" вы не можете вывезти свои же слова?

- но правильно ли я понимаю, этим переводом стрелок и переходом на "ты" вы не можете вывезти свои же слова?