Pridnya

-

Постов

208 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Pridnya

-

-

2 hours ago, x893 said:

Генерируете сертификат.

Приватным ключом подписываете свой bin и прячете ключ в сейф.

Публичный ключ сохраняете в программе и при обновлении прошивке проверяете подпись (и нужные поля если нужно).

Диагностическое приложение для ПК генерирует сертификат X509v3 для пользователя c Login Password (кто запустил на ПК диагностическое приложение) - получили файл сертификата.

Как закрытым ключом подписать свой файл bin? И где взять этот закрытый ключ? Предполагается, что открытый ключ известен всем экземплярам (приложениям для ПК).

PS: Открытый и закрытый ключ используется в алгоритмах асимметричного шифрования, а в моем случае прошивка шифруется алгоритмом симметричного шифрования - один ключ, закрытый.

-

Всем привет!

Есть прошивка для микроконтроллера - файл *.bin полученный из *.hex, она встраивается в проект диагностического приложение для ПК - как файл ресурса, проект собирается с последней версией прошивки и после запуска диагностического приложения на ПК можно обновить прошивку в девайсе через интерфейс USB. Появилось требование "файл прошивки должен быть подписан сертификатом x509v3". Как это сделать?

-

1 hour ago, x893 said:

А уточнить можете? В данный момент прием пакетов более 64-х байт выполняю склейкой пакетов по 64 байта. 64+64=128, 64+32=96. Каждый раз при вызове функции копирую фрагмент данных в другой массив.

#define APP_RX_DATA_SIZE 64 #define APP_TX_DATA_SIZE 128 uint8_t UserRxBufferFS[APP_RX_DATA_SIZE]; uint8_t UserTxBufferFS[APP_TX_DATA_SIZE]; uint8_t UserRxBuffer[256]; uint8_t UserTxBuffer[256]; uint16_t UsbRxCtr = 0; uint16_t UsbLenCtr = 0; static int8_t CDC_Receive_FS(uint8_t* Buf, uint32_t *Len) { /* USER CODE BEGIN 6 */ USBD_CDC_SetRxBuffer(&hUsbDeviceFS, &UserRxBufferFS[0]); USBD_CDC_ReceivePacket(&hUsbDeviceFS); memcpy(UserRxBuffer + (64*UsbRxCtr), UserRxBufferFS, *Len); UsbRxCtr++; UsbLenCtr += (*Len); return (USBD_OK); /* USER CODE END 6 */ }

-

Здравствуйте, уважаемые разработчики!

Функция принимающая данные вызывается каждый раз при приеме 64-х байт. Если принимается пакет из 128 байт, то она вызывается дважды, при этом при второй пакет из 64-х байт записывается с начала буфера UserRxBufferFS.

Я предполагал, что APP_RX_DATA_SIZE 128 позволит принимать пакеты до 128 байт.

#define APP_RX_DATA_SIZE 128 #define APP_TX_DATA_SIZE 128 uint8_t UserRxBufferFS[APP_RX_DATA_SIZE]; uint8_t UserTxBufferFS[APP_TX_DATA_SIZE]; static int8_t CDC_Receive_FS(uint8_t* Buf, uint32_t *Len) { /* USER CODE BEGIN 6 */ USBD_CDC_SetRxBuffer(&hUsbDeviceFS, &UserRxBufferFS[0]); USBD_CDC_ReceivePacket(&hUsbDeviceFS); return (USBD_OK); /* USER CODE END 6 */ }

Функция передачи корректно передает 128 байт:

memcpy(UserTxBufferFS, "01234567ABCDEFGH01234567ABCDEFGH01234567ABCDEFGH01234567ABCDEFGH01234567ABCDEFGH01234567ABCDEFGH01234567ABCDEFGH01234567ABCDEFGH", 128); Stat = CDC_Transmit_FS((uint8_t*)UserTxBufferFS, 128);

Вопрос к функции приёма. Где я косячу?

-

10 hours ago, Darth Vader said:

Надо найти исходник - файл SVD, отредактировать его, скомпилировать, и получить на выходе новый исправленный SFR. Структура SVD файла и работа с ним хорошо описана тут. Читайте, пробуйте. Там внутри ничего сложного, обычный xml.

Спасибо! :)

-

Здравствуйте!

Можно ли как-то отредактировать файл STM32***.SFR, чтобы в нем появились недостающие регистры (нет регистров ADC, RCC, FDCAN)?

-

4 hours ago, mov said:

Отладчики бывают разных версий (по времени выхода в свет), т.е. реализаций в железе да плюс ещё учесть разные версии софтверных драйверов . М23 относительно новое ядро. Старые дебаггеры могут не определить это ядро.

Вот поэтому я и прошу совета, т.к. в описании на ULINK-и разных версий написано "поддержка Cortex M", "настраиваемые пользователем алгоритмы программирования FLASH...", но это относится к M0,M3,M4, а меня интересует M23. Может, на форуме есть разработчики, использующие ULINK для какого-нибудь Cortex-M23 (а желательно для Renesas RA2L1).

-

Здравствуйте, уважаемые разработчики!

Интересует вопрос, Keil ULINK поддерживает отладку и программирование микроконтроллеров из серии RA2L1 (Cortex M23)? Renesas E2 Lite поддерживает, но его нет в списке отладчиков, в Keil. На данный момент остается только Segger JLink (версия 7.23). Кто что посоветует?

-

Здравствуйте, уважаемые разработчики!

Интересует вопрос, Keil ULINK поддерживает отладку и программирование микроконтроллеров из серии RA2L1? Renesas E2 Lite поддерживает, но его нет в списке отладчиков, в Keil. На данный момент остается только Segger JLink (версия 7.23). Кто что посоветует?

-

1 hour ago, Allregia said:

Да не за что. Но внешний клок для STA - оверкилл.

Помоим подсчетам модуль I2S STM32F407 не может выдать частоту MainClock 49.152 MHz из-за ограничений на значения делителя и верхнего значения частоты I2SCLOCK <= 192 MHz. Минимальный делитель равен 4, а верхнее значение частоты I2SCLOCK <= 192 MHz. Или я не прав? Наверное, поэтому нужно использовать внешний генератор MainClock 49.152 MHz.

QuoteSPI_I2S prescaler register (SPI_I2SPR)

Bits 7:0 I2SDIV: I2S Linear prescaler

I2SDIV [7:0] = 0 or I2SDIV [7:0] = 1 are forbidden values.Bit 8 ODD: Odd factor for the prescaler

0: real divider value is = I2SDIV *2

1: real divider value is = (I2SDIV * 2)+1 -

3 minutes ago, Allregia said:

Внешний мастерклок подается на CK_IN (РС9).

Спасибо!

-

11 minutes ago, Allregia said:

Это если работать с pll и использовать выход mclk.

Я обычнно работаю с внешним mclk, 512 или 1024Fs

А с STA333 навскидку действительно не понятно.

От внешнего кварцевого генератора подаете сигнал на вход mclk I2S Slave?

-

19 minutes ago, Allregia said:Quote

Вопрос не в комбинации а в джиттере. Но для STA плл-я более чем.

49.152 = это 1024фс,, одна из стандарных аудио частот для клоков.

Я с STA особо не разбирался, но вроде внутри там все на 96/24 происходит.

Частота битклока напрямую зависи от разрядности данных, как правило она 64фс, но в древних устройствах бывает и 32фс.

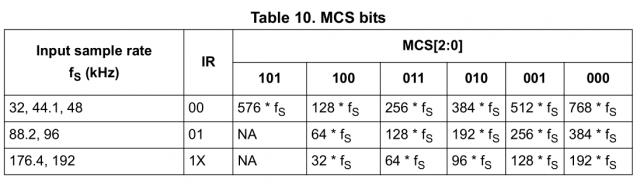

Про XTI там четко пишут что должна быьт кратна Fs:

The external clock frequency provided to the XTI pin must be a multiple of the input

sampling frequency (fS).

The relationship between the input clock and the input sampling rate is determined by both

the MCSx and the IR (input rate) register bits. The MCSx bits determine the PLL factor

generating the internal clock and the IR bit determines the oversampling ratio used

internally.Еще там дальше про оверсемплинг пишут.

49.152 MHz = 1024 * Fs, где Fs=48kHz, но судя по описанию на STA333W, режим 1024*Fs не поддерживается микросхемой (я приводил таблицу в начале топика), поддерживаются режимы 32-768, поэтому не понятно, какая частота должна подаваться на вход ХTI.

Сейчас частота XTI кратна Fs: XTI=256*Fs=12.288 MHz, где Fs=48kHz, но работают два канала из четырех, левый 200 Гц, правый 100 Гц.

STM32F407 I2S умеет выдавать Fs*256.

А в этом описании есть два термина external clock и internal clock (49.152 MHz for Fs 48 kHz) и еще к чему-то PLL упоминается, что предполагает кратность частот (подаем одну - получаем другую).

-

3 hours ago, Allregia said:Quote

А откуда они в исходном буфере берутся? Если тоже с I2S, то они там уже с чередованием.

Я обычно эти буфера в структуру заворачиваю.

Вообще, в чем именно состоит проблема - не понял.

QuoteНет, данные берутся не с I2S, а с другого источника, просто есть два буфера, один для левого и один для правого канала.

QuoteНу еще там есть некторые заморочки с частотами тактированя. Я правда, практически никогда не использовал его от внутреннго PLL, т.к. требования как правило были гораздо выше, чем он может обеспечить. Но для STA333 это конечно оверкилл, там и внутреннего выше крыши.

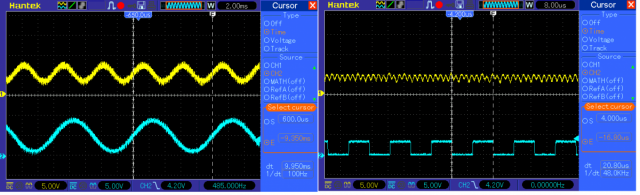

Внутреннего I2S PLL вполне хватает для некторых комбинаций частот. Не очень понятно, какую частоту нужно подавать на вход XTI STA333W. Работает (два канала из четырех) только от XTI=12.288 MHz = Fs*256, где Fs=48kHz, 16 бит на канал. Т.е. частоты на входах получаются такие:

XTI = 12.288 MHz = Fs * 256.

BCKI = 1.536 MHz = Fs * 32, где 32 бита на два канала.

LRCKI = Fs = 48 kHz.

Fpwm = 384kHz = Fs *8.

А в документации на STA333W написано, что для Fs = 48 kHz нужна частота 49,152 MHz. Вот здесь совсем не понятно, почему 49.152 MHz и вообще не описаны поддержиаемые частоты XTI, BCLKI.

2 hours ago, jcxz said:Видимо как всегда - для обработки предполагается использование некоей готовой чужой "либы", которая так не умеет.

Quote

QuoteНикакие чужие либы не используются. Для STA333W либ нет. На все семейство описание скудное. Есть несколько примеров, но в готовом оборудовании (LCD TV). В русскоязычном сегменте одни чинщики аппаратуры про них спрашивали, разработчики не упоминали. У ST на комьюнити тоже тишина.

2 hours ago, Allregia said:QuoteЗависит от того, как обработка сделана. В общем случая-же никто не мешает делать обработку семплов, не лежащих непрерывно в памяти.

Все равно ведь, для какой-то серьезной обработки STM32F4 мало пригоден, тут H7 или G4, да и то...

А в случае соединения с STA333 вобще непонятно зачем обработка в STM32 - она же внутри STA какая-никакая уже есть.

Никто не мешает обрабатывать сэмплы через один, достаточно написать свои обработчики. Если данные приходят не от I2S, то нужно собирать их в буфер.

-

23 minutes ago, uriy said:

Мне кажется вас смущает то что в буфере перемешаны дынные правого и левого каналов. Увы кажется STM не умеет раскидывать по каналам. Если вам беэ этого не жить то берите DSP процессор. Blackfin так умеет и другие наверняка тоже.

Да, это одна из особенностей реализации I2S в STM32F407. Получается что два буфера данных нужно слить в один с чередованием данных и затем отправить в I2S через DMA. А иначе как разработчики микроконтроллера предполагали использовать режим I2S DMA? Пока только так и работает. Вот в STM32F427 обнаружил SAI (Serial audio interface), нужно его посмотреть.

-

9 hours ago, aaarrr said:

Нормальная.

Вообще, не очень понятно, о чем вопрос: кем, например, предполагалось? Буфер с чередующимися данными каналов - вполне нормальное явление, и уж точно не стоит привлекать DMA для перестановки.

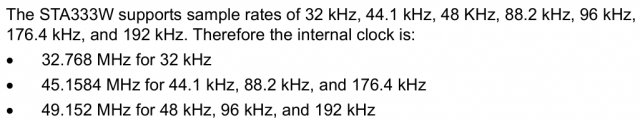

В STM32F4 есть интерфейсы для передачи аудио: STM32F407 I2S, в STM32F427 I2S и SAI (Serial audio interface). Вообще интерфейс I2S в STM32F4 поддерживает режим MainClock = 256 × Fs; (Fs is the audio sampling frequency), но фирма STMicroelectronics производит микросхемы Digital Terminal Audio (таблица из документации), у которых эти множители разные, от 32*Fs до 768*Fs. И у STM32F407 есть ограничения на настройку I2S PLL, например, для поддержки некоторых частот придется использовать кварц 6.144 МГц, 12.288 МГц и другие, т.к. у самих микросхем Digital Terminal Audio есть еще дополнительные требования к тактовой частоте MainClock. Т.е. при использовании кварца на 8 МГц не удается настроить I2S PLL на частоту 49.152 МГц.

-

Здравствуйте!

Master соединен со Slave, по интерфейсу передаются данные двух каналов (левого и правого) с использованием DMA, но для этого создается новый буфер двойного размера в котором данные каналов чередуются. Правильная ли это реализация I2S + DMA или есть способ проще? Вообще, не очень понятно, как предполагалось создавать двойной буфер чередующихся данных. Может быть с использование DMA memory-tomemory с инкрементом адреса на два? Или как?

-

Здравствуйте, уважаемые специалисты!

По типовой схеме собран аудиоусилитель, микросхема STA333W. Микросхема имеет два интерфейса I2C и I2S, по первому интерфейсу все регистры микросхемы пишутся и читаются, а по интерфейсу I2S микросхема получает аудиопоток (48 кГц, 2 канала по 16 бит). Удалось частично запустить микросхему - работают два канала из четырех, 1A и 2A, каналы 1B и 2B выдают минимальный ШИМ (т.е. работает половина левого канала и половина правого). При этом тактовые частоты на линиях интерфейса I2S следующие:

XTI = 12.228 MHz; (Fs*256)

BCLKI = 1.53 MHz;

LRCLKI = Fs = 48 kHz;А в техописании на микросхему написано:

The STA333W supports sample rates of 32 kHz, 44.1 kHz, 48 KHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz. Therefore the internal clock is:

32.768 MHz for 32 kHz

45.1584 MHz for 44.1 kHz, 88.2 kHz, and 176.4 kHz

49.152 MHz for 48 kHz, 96 kHz, and 192 kHz

The external clock frequency provided to the XTI pin must be a multiple of the input sample frequency (f S ).Вроде как есть два термина external clock и internal clock, получается что микросхема из внешнего тактового сигнала XTI=12.228 MHz формирует внутренний сигнал PLL=12.22*4=49.152 MHz? Или на вход XTI нужно подавать 49.152 MHz? Если подать на вход XTI частоту 49.152 МГц, то на выходе микросхемы вообще отсутствуют импульсы.

-

Здравствуйте!

Подскажите пожалуйста, совместима ли топлогия Full Bridge Phase-Shifted с режимом Peak Current Control? Оба режима реализованы в микроконтроллере STM32F3. По отдельности работают, для Full Bridge Phase-Shifted фазовый сдвиг меняю в прерывании от таймера TIM1, т.е. программно, а Peak Current Control работает в случае однофазного или двухфазного повышающего преобразователя (для ограничения тока используется компаратор COMP2). Интересует вопрос совместимости.

-

4 hours ago, Stepanov said:

Для этой задачи лучше перейти на TMS320F28027, с ним это решается гарантированно на отлично...

Спасибо за участие! С TMS не работал, ознакомлюсь.

-

Здравствуйте!

Peak Current Control реализовал на однофазном и двухфазном повышающем конвертере.

Full Bridge Phase Shifted реализовал без Peak Current Control, в преывании от таймера TIM1 меняю фазовый сдвиг между сигналами.

Подскажите, пожалуйста, совместимы ли Full Bridge Phase Shifted и Peak Current Control с использованием этого микроконтроллера?

Никак не получается совместить.

-

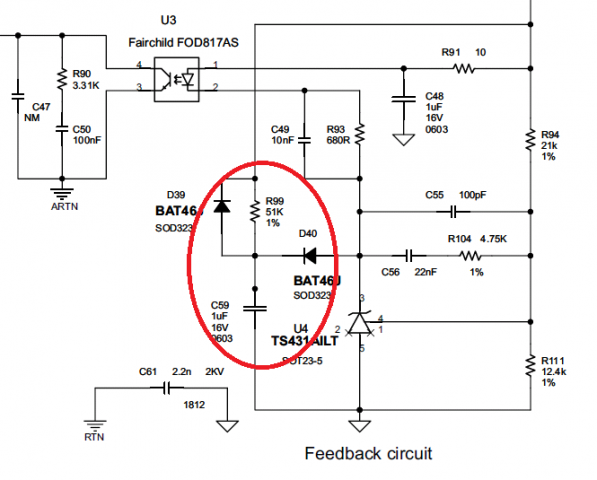

3 minutes ago, Plain said:

Ясно же видно, что цепь в начале работы увеличивает сигнал ОС до предела, что означает уменьшение до предела же мощности БП, т.е. типовой мягкий старт. В конце работы цепь требуется быстро возвратить в исходное состояние, для чего конденсатор разряжается через второй диод, питая нагрузку БП.

А я туплю, почему она есть только в некоторых схемах, которые я раньше не встречал. И номиналы у RC у разных производителей разные. Вообще в микросхеме есть soft-start и в типовом варианте включения такой цепочки нет, поэтому я и не сообразил. Оказывается для реализации soft-start (удлинения что ли ? ) нужно еще и эту цепь добавлять. Поэкспериментирую. Спасибо!

-

Здравствуйте!

Подскажите пожалуйста назначение RCD цепи возле TL431. Уже у нескольких производителей видел такую цепочку, в Application Note, но назначение понять не могу,

добавил к своей схеме (прямоходовый импульсный преобразователь) - разницы не увидел. Когда эта цепочка работает, может, я не создаю такой режим?

-

3 minutes ago, _pv said:

например чтобы подключить что-нибудь вроде KSZ8895

Спасибо! Теперь понятно.

Файл прошивки подписан сертификатом x509v3

в STM

Опубликовано · Пожаловаться

Нужно "Прошивка должна быть подписана цифровой подписью в соответствии с X509v3. Другие сертификаты не допускаются". И трафик при обновлении прошивки должен шифроваться.

Получается, что прошивка должна иметь цифровую подпись, наверное, для проверки подлинности. Обмен между приложением и девайсом должен быть зашифрован.

Похоже, что девайс принимает прошивку, расшифровывает её, проверяет подпись (подлинность прошивки) и обновляется.