Dmitry_B

-

Постов

245 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные Dmitry_B

-

-

Опубликовано · Изменено пользователем Dmitry_B · Пожаловаться

Just now, iosifk said:И Вы что, тысячи триггеров вручную готовы "просмотреть" даже при том, что компилятор "пообещал" Вам, что все цепи развел правильно?

И откуда вот это утверждение: "Задержка распространения clock'а от выхода буферного усилителя до входов многочисленных триггеров проекта велика"?? Насколько велика и насколько отличается?

И кстати, какова тактовая частота проекта?

Вы обсуждаете мои мотивы? Извольте: мне это интересно.

Утверждение из отчета Timing analiser. Задержка около 3 нс от входного контакта. Отличие - десятки пикосекунд. Частота для пробы 250 МГц.

-

Встроенный симулятор Vivado легко позволяет вывести в окно моделирования сигналы из HDL - описания post-imlementation проекта.

Но вот проблема: сигнал clock можно отобразить как выход внутреннего усилителя и как сигнал входного pin'а.

Задержка распространения clock'а от выхода буферного усилителя до входов многочисленных триггеров проекта велика и несколько отличается для разных триггеров.

Можно ли вывести на временную диаграмму сигналы тактовой частоты на входах самих триггеров?

-

4 hours ago, FatRobot said:

забейте в гугле

synopsys tcoug

Большое спасибо.

-

Дайте пожалуйста ссылку на полное описание языка создания constraints Synopsys.

-

Опубликовано · Изменено пользователем Dmitry_B

Ошибка в тексте · ПожаловатьсяПробовали ли использовать симулятор Modelsim из Vivado HLS?

Если у кого получилось, сообщите пожалуйста какие версии Vivado и Modelsim.

-

22 hours ago, Flood said:

Спасибо за помощь.

Неопределенность хуже всего.

-

Еще один вопросик появился: где взять IBIS - модель JESD204B выходов АЦП? В предоставленой ADI модели эти выводы описаны крайне странно: ни вольтамперной характеристики, ни Ramp.

-

Интересует имя IBIS - модели входа GTX интерфейса. У Xilinx-7 много моделей, какую выбрать? Может, где-то есть описание/рекомендации?

-

Кто-то разбирался?

Интересуют номера контактов, на которые выведено управление номером активного FTW (частоты настройки управляемого генератора).

В микросхеме хранится 16 значений, в datasheet (раздел NCO) нарисовано 4 контакта для их выбора, но на изображении корпуса в наличии только 2, со странными названиями A0, B0.

В описании программно-доступных регистров можно найти упоминание еще двух: А1 и В1, но ни в таблице описания контактов, ни на изображении корпуса их уже нет.

Допустим, как-то удастся обнаружить, на какие контакты выведены А1, В1; все равно останется неясным, что надо подавать на A0,A1,B0,B1 чтобы выбрать FTW3, например. Какой из них младший-старший?

-

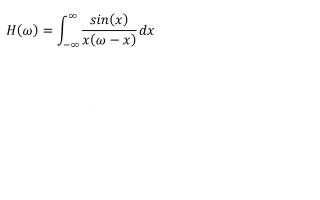

да нет никаких обоснований. я же дилетант и делаю все в лоб и неправильно через неопределенные интегралы

INT(sin(x)/(x*(w-x)), dx)=

INT( sin(x)/(w*x) + sin(x)/(w*(w-x)) , dx)

С первой частью все понятно, откладываем до взятия пределов.

Далее

INT( sin(x)/(w-x) , dx): замена u=w-x (пределы все равно останутся плюсминус бесконечность; чи не контур и не вектор, направления нет)

INT( sin(w-u)/u , du)= sin(w)*INT(cos(u)/u, du)-cos(w)*INT(sin(u)/u,du)

Опять, SI(±∞) и CO(±∞), значения приведены ранее. Т.е. интегральный косинус можно отбросить сразу с его множителем. Останется косинус параметра при интегральном синусе, и удвоенный инт. синус в добавке. Все это поделено на параметр в общем знаменателе.

Может грубо и неверно, но результат должен получиться ранее указанный.

Браво!

Красивый и простой вывод!

-

Опубликовано · Изменено пользователем Дмитрий_Б · Пожаловаться

В итоге получается так:UPD: Исправил ошибки.. :biggrin:

То есть, искомый интеграл равен:

I(ω) = pi*[1- cos(ω)]/ω.

Спасибо за помощь.

Тоже нашел ответ в справочнике 1974г.

К стати, я правильно понял, что интеграл по полуокружности на самом деле брать не надо, он в 2 раза меньше, чем интеграл по окружности, и его можно через вычет получить?

-

ЕМНИП, через вычеты.

У функции два полюса на вещественной оси и две особенности на бесконечности. Нужно сместить контур интегрирования и воспользоваться теоремой Коши.

Метод такой:

Рисуете на комплексной плоскости прямоугольник охватывающий оба полюса подынтегральной функции: x = 0 и x = ω.

По теореме Коши интеграл по этому прямоугольнику равен сумме вычетов подынтегральной функции.

Вычет в точке x = 0 равен нулю.

Вычет в точке x = ω равен sin(ω)/ω.

Теперь смещаете левую и правую стороны к прямоугольника к -∞ и +∞, соответственно.

Поскольку при x -> -∞ и x -> +∞ подынтегральная функция стремится к нулю как: 1/x2, оба интеграла вдоль левой и правой стороны прямоугольника стремятся к нулю.

Теперь смещаете верхнюю и нижнюю стороны к прямоугольника к +i0 и -i0 соответственно.

Теперь в интеграле вдоль отрезка (+∞,+i0)..(-∞,+i0) меняете направление интегрирования и замечаете, что сумма обоих получившихся интегралов равна удвоенному интегралу, который вы хотите вычислить.

В итоге получаете:

ʃ{sin(x)/[x(ω-x)]dx = (1/2)*sin(ω)/ω.

Если ничего не напутал.. :biggrin:

Идея понятна.

Есть тут неприятность: теорема о вычетах требует, чтобы на контуре интегрирования не было полюсов - а они как раз на действительной оси.

Нас интересует интеграл вдоль действительной оси - это должно быть нижней стороной контура при обычном обходе против часовой стрелки.

Другие стороны (будь то прямоугольник или пол-окружности) должны быть бесконечно удалены от 0. Метод работает, если подинтегральная функция комплексного аргумента стремится по модулю к 0 при стремлении к бесконечности модуля комплексного аргумента.

И здесь вторая трудность: |sin()| комплексного аргумента неограниченно растет при увеличении мнимой части - превращаясь в sh(). Хорошее предположение об ограниченности подинтегральной функции нарушается.

И еще одно. Получилось, что преобразование Гильберта от sinc() есть та же самая sinc(). Тогда комплексная огибающая sinc() - тоже sinc()? Не очень похоже на правду.

-

Если я не ошибаюсь, то интеграл sin x/x^2, не должен сходиться в окрестности 0. Соответственно H(0) неопределено.

Похоже. Ну, положим, там дельта - функция. А на остальной оси?

Да. Но как его брать?

-

-

Существует ли какое-либо правило назначения контактам разъема HPC стандарта VITA 57.4 FMC сигналов интерфейса JESD204B?

Ясно, что данные и тактовая частота в разъеме стандартного мезонинного разъема присутствуют, а вот как с оставшейся парой сигналов интерфейса JESD204B?

-

Кому все еще интересно, из источников, которым я вынужден доверять:

время предустановки данных относительно окончания импульса nRd вычисляется:

Tsu= (период клока ядра + 66 нс)*1,2.

Множитель 1,2 - рекомендуемый запас 20%.

При максимальной частоте ядра 144 МГц - примерно 90 нс.

Вот теперь можно определить допустимую длительность nRd как сумму задержки переключения периферийного устройства из третьего состояния в активное + Tsu.

-

Ваш первначальный вопрос вроде-как касался именно времени tdh?

Нет.

Перевод: tsu - set up time - время предустановки;

th - hold time - время удержания.

Схемотехнику достаточно знать, что чтение данных с шины осуществляется в момент времени после 1/2 tcycle но до фронта окончания nRD.А что заставляет Вас думать, что установления данных в момент 1/2 цикла достаточно? На рисунке они явно устанавливаются раньше (но насколько раньше - непонятно).

Пофантазируем еще.

Момент "полцикла" на рисунке примерно совпадает с фронтом CLKO при СPOL=0.

А возможно, всего лишь надо установить данные до переднего фронта CLKO при СPOL=0 (последнего, при активном nRD)? Тогда - за какое время до фронта CLKO?

С другой стороны, похоже, "фиксация данных" происходит по спаду CLKO при СPOL=0.

Тогда возможно, данные достаточно установить на шине чуть раньше, чем закончится последний импульс CLKO при активном nRD? Тогда - за какое время до спада CLKO?

Но при этих предположениях нам надо знать взаимное положение CLKO и nRD, а также, строго говоря, и моментов переключения адреса. Чего разработчики МК (видимо беспокоясь о нашем душевном равновесии) не предоставили.

Возможно, вероятно, похоже...... Так аппаратуру не разрабатывают. О том и речь.

-

ТСКЯ.431296.008CП стр.134 Рисунок 29. Диаграмма чтения. Документ более старый и диаграмма чтения показана подробнее, чем в последней версии.

Спасибо. Но в части цикла чтения ничего дополнительно нет. Любезно обозначили время удержания th = 0, а вот tsu - нет. Вместо этого бесполезная жирная стрелка "фиксация данных". Как этот "момент фиксации" расположен относительно nRD, либо чего бы то ни было другого осмысленного - предлагается пофантазировать самостоятельно... Уж не говорю о том, сколько читаемый код с шины данных должен постоять на шине до наступления сего счастливого момента.

Уважаемый AVR!

Разумеется, у Миландра проблем тем меньше, чем меньше контролируемых параметров при сдаче микросхемы по ТУ. Да и выход годных может оказаться меньше.

Но при этом игнорируются интересы разработчика аппаратуры - и это проблема (естественно, не главного конструктора МК).

Формат форума не позволяет всерьез обсуждать методику разработки цифровой аппаратуры, для которой и требуется параметр tsu.

Я, правда, думал, что это всем разработчикам известно, ибо классика.

-

Ну, такие вопросы может техподдержка и не знать, может эта часть - лицензированная часть ядра. По телефону такой вопрос можно сходу и не ответить. Попробуйте форум.

Не сходу, а после консультации с главным конструктором. Какой смысл скрывать информацию, без которой, строго говоря, нельзя подключать к шине какие - либо устройства?

Но что значит импульс чтения, у меня нет ТУ, есть лишь их документация в PDF. Может речь про фронт/спад чтения?ТУ в этой части дословно повторяет общедоступную спецификацию в PDF.

Речь о сигнале nRD (рис.29 спецификации). Картинку не могу загрузить, файл docx - тоже (мне "запрещено загружать файлы такого типа"!!!).

-

Опубликовано · Изменено пользователем Дмитрий_Б · Пожаловаться

Прошу прощения, следует уточнить, молчит где? Форум, почта, телефон, в документации не написали?По телефону техподдержка. Впрочем, не молчит, но говорит на отвлеченные темы, вместо ответа на вполне конкретный вопрос. Похоже, неохота им возиться.

В документации ничего - это само собой.

-

Кто работал, известно ли время предустановки данных на внешней системной шине относительно окончания импульса чтения nRD (рис.29 ТУ)?

То есть, какое время следует подержать данные на шине до того, когда импульс чтения закончится?

Миландр таинственно молчит... (Впрочем, можно проще сказать: послал...)

-

Помогите пожалуйста еще разок: как в проекте Quartus для нескольких конечных автоматов назначить разные способы синтеза? Например, один-one-hot,а другой- minimum bit?

-

В случае, если при синтезе ваша FSM была определена синтезатором как one-hot, то всё правильно, 16 триггеров - это ожидаемо.

Объясните, почему вы считаете, что очевидно достаточно 4-х?

Потому что 4 двоичных разряда описывают 16 различных состояний. А что такое one-hot?

-

У меня получилось, что конечный автомат с 16-ю состояниями реализован на 16 триггерах. Очевидно, на самом деле достаточно 4-х. При создании автомата использовал штатный редактор конечных автоматов Quartus с последующей генерацией VHDL- описания.

Поделитесь, кто делал: у вас то же самое?

Вывод на временную диаграмму сигнала, отсутствующего в HDL - описании проекта Vivado

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

Данные с частотой 250 МГц на вход не подаются. Это всего лишь упражнение на освоение Vivado и Xilinx.

Вот и я на это надеялся. Но в текстовом описании на Verilog'е, при выделении имени нужного триггера (примитив FDCE) и нажатии правой кнопки мыши, меню "добавить в wave" неактивно. Мне удается добавлять только имена входных сигналов триггера. Имя входного сигнала на входе С - выходной сигнал буфера clock, и это не слишком интересно.