kas

Свой-

Постов

76 -

Зарегистрирован

-

Посещение

-

Есть мнение, что эта утилита (перенумерации элементов сверху вниз и слева направо) ненужна. Перенумеровывать можно средствами Expedition PCB, и это будет по ГОСТ. Пункт 3.19 ГОСТ 2.702-75 гласит: Порядковые номера должны быть присвоены в соответствии с последовательностью расположения элементов или устройств на схеме сверху вниз в направлении слева направо. При необходимости допускается изменять последовательность присвоения порядковых номеров в зависимости от размещения элементов в изделии, направления прохождения сигналов или функциональной последовательности процесса. При внесении изменений в схему последовательность присвоения порядковых номеров может быть нарушена. Пункт 5.3.10 ГОСТ 2.702-2011 также содержит подобные строки: 5.3.10 Порядковые номера следует присваивать в соответствии с последовательностью расположения элементов или устройств на схеме сверху вниз в направлении слева направо. При необходимости допускается изменять последовательность присвоения порядковых номеров в зависимости от размещения элементов в изделии, направления прохождения сигналов или функциональной последовательности процесса. При внесении изменений в схему последовательность присвоения порядковых номеров может быть изменена. ИМХО, надо воевать с нормоконтролем, учить их читать ГОСТ.

-

Подтяжка входов

kas ответил studert тема в Языки проектирования на ПЛИС (FPGA)

Вы где слабую единицу планируете применить? В синтезируемом модуле или в модуле тестового воздействия? -

На время изучения HDL, ИМХО, надо бы подзабыть про языки программирования, да вспомнить цифровую схемотехнику. Изучать VHDL я начинал с Бибило Основы языка VHDL.

-

Спасибо большое! Все получилось. Моя ошибка была в том, что я пытался сразу всю систему синтезировать.

-

Можно поподробнее про барабан? Как затягивать исходники в Synplify?

-

Altium для новых начинающих

kas ответил Uladzimir тема в Altium Designer, DXP, Protel

Тоже не понятно почему так. Есть JumperID, который показывает группу соединенных выводов внутри микросхемы. Так зачем мне кроме JumperID еще и десигнаторы одинаковыми делать? Идея про JumperID хорошая, но, ИМХО, немного не доработанная. -

Altium для новых начинающих

kas ответил Uladzimir тема в Altium Designer, DXP, Protel

Пожалуйста, вот весь тестовый проект. Я понимаю что этот механизм говорит о замыкании выводов внутри компонента, но не могу понять почему альтиум зная о замыканиях внутри компонента не может определить замыкания между разными цепями через компонент. Похоже программисты альтиума тут немного не дороаботали :). tst_kz.rar -

Altium для новых начинающих

kas ответил Uladzimir тема в Altium Designer, DXP, Protel

Вопрос про JumperID. Есть некоторый компонент, у которого сигналы "АА" и "ББ" выведены на несколько выводов. Я, при создании посадочного места для выводов сигнала "АА" указал параметр JumperID=1, а для выводов сигнала "ББ" JumperID=2. Получилось примерно следующее: имя designator jumperID "АА" A1 1 "АА" A2 1 "АА" A3 1 "АА" A4 1 "ББ" Б1 2 "ББ" Б2 2 "ББ" Б3 2 Считаю, что этими действиями я указал соединения выводов внутри кристалла. Делаю следующий шаг - соединяю у компонента в схеме выводы А1 и Б1 цепью "НетАБ", выводы А2...А4 подключаю к цепи "НетАА", а выводы Б2, Б3 подключаю к цепи "НетББ". Создаю печатную плату, на плате вижу все цепи, в том числе и соединение между А1 и Б1, развожу все цепи, делаю DRC и не получаю ошибки, при этом правило запрещающее соединять цепи с разными именами включено и работает. Получается либо я не так понимаю механизм работы JumperID, либо я что-то не настроил как надо, либо это программисты в альтиуме что-то не дописали. Помогите, пожалуйста, разобраться. -

TCL script

kas ответил Iouri тема в Среды разработки - обсуждаем САПРы

смсла может и нет, но другого пути вставить номер и дату сборки в проект автоматически я не нашел :05: . Если кто подсажет как это сделать без tcl-скриптов - буду безмерно благодарен. -

TCL script

kas ответил Iouri тема в Среды разработки - обсуждаем САПРы

В ISE можно запустить tcl скрипт до синтеза? Например в ISE нажимаю я "синтезировать", а уменя перед синтезом мой скрипт раз, и выполнился. Проверил там чего-нибудь, или даже подредактировал. -

как написать на vhdl память

kas ответил _ANDREW тема в Языки проектирования на ПЛИС (FPGA)

entity ramNxM is generic( AddrWidht : integer := 4; DataWidht : integer := 2); port ( clk : in std_logic; we : in std_logic; AddrA : in std_logic_vector(AddrWidht-1 downto 0); DataIn : in std_logic_vector(DataWidht-1 downto 0); AddrB : in std_logic_vector(AddrWidht-1 downto 0); DataOutA : out std_logic_vector(DataWidht-1 downto 0); DataOutB : out std_logic_vector(DataWidht-1 downto 0) ); end ramNxM; architecture Behavioral of ramNxM is type ram_type is array ((2**AddrWidht - 1) downto 0) of std_logic_vector (DataWidht-1 downto 0); signal RAM : ram_type; begin process (clk) begin if rising_edge(Clk) then if we = '1' then RAM(conv_integer(AddrA)) <= DataIn; end if; end if; end process; DataOutA <= RAM(conv_integer(AddrA)); DataOutB <= RAM(conv_integer(AddrB)); end Behavioral; У меня такой код синтезируется в ISE'е. Память правда распределенная, но мне такую и надо. -

Реализация БПФ на ПЛИС

kas ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

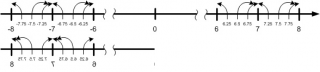

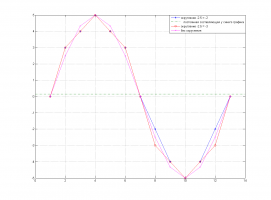

? :rolleyes: Например как на этой картинке И уже совсем по детски конечно, но Matlab -7.5 округляет до -8 Вот я и пытаюсь разобраться. :) -

Реализация БПФ на ПЛИС

kas ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

А разве числовая ось не должна быть зеркальной относительно нуля? Если мы будем отрицательные числа с дробной частью равной 0.5 округлять до большего по абсолютной величине, то мы получем смещение. -

Реализация БПФ на ПЛИС

kas ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

я не совсем удачно пример выбрал и, в попыхах, посчитал неправильно :unsure: вот, набросал небольшую програмку, и получил вот такой результат: a = -31 (11100001b) a+2 = -29 (11100011b) (a+2)>>2 11111000 = -8; a/4= -7.75 - правильно a = -30 (11100010b) a+2 = -28 (11100100b) (a+2)>>2 11111001 = -7; a/4= -7.50 - неправильно? a = -29 (11100011b) a+2 = -27 (11100101b) (a+2)>>2 11111001 = -7; a/4= -7.25 - правильно a = -28 (11100100b) a+2 = -26 (11100110b) (a+2)>>2 11111001 = -7; a/4= -7.00 - правильно a = -27 (11100101b) a+2 = -25 (11100111b) (a+2)>>2 11111001 = -7; a/4= -6.75 - правильно a = -26 (11100110b) a+2 = -24 (11101000b) (a+2)>>2 11111010 = -6; a/4= -6.50 - неправильно? a = -25 (11100111b) a+2 = -23 (11101001b) (a+2)>>2 11111010 = -6; a/4 = -6.25 - правильно a = -24 (11101000b) a+2 = -22 (11101010b) (a+2)>>2 11111010 = -6; a/4 = -6.00 - правильно ... a = 24 (00011000b) a+2 = 26 (00011010b) (a+2)>>2 00000110 = 6; a/4 = 6.00 - правильно a = 25 (00011001b) a+2 = 27 (00011011b) (a+2)>>2 00000110 = 6; a/4 = 6.25 - правильно a = 26 (00011010b) a+2 = 28 (00011100b) (a+2)>>2 00000111 = 7; a/4 = 6.50 - правильно a = 27 (00011011b) a+2 = 29 (00011101b) (a+2)>>2 00000111 = 7; a/4 = 6.75 - правильно a = 28 (00011100b) a+2 = 30 (00011110b) (a+2)>>2 00000111 = 7; a/4 = 7.00 - правильно a = 29 (00011101b) a+2 = 31 (00011111b) (a+2)>>2 00000111 = 7; a/4 = 7.25 - правильно a = 30 (00011110b) a+2 = 32 (00100000b) (a+2)>>2 00001000 = 8; a/4 = 7.50 - правильно a = 31 (00011111b) a+2 = 33 (00100001b) (a+2)>>2 00001000 = 8; a/4 = 7.75 - правильно Получается ошибки при округлении отрицательных чисел все-таки будут? -

Реализация БПФ на ПЛИС

kas ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

(-32 + 2)/4 = -7.5, отбрасываем младшие разряды получаем -7, а должны получить -8. При сумме больше нуля прибавление двойки перед делением на 4 дает нужный результат, а вот когда сумма меньше нуля, то появляется ошибка. Я что-то упустил?