-

Постов

243 -

Зарегистрирован

-

Посещение

Весь контент Я.К.

-

Два клока - как сделать на C2?

Я.К. опубликовал тема в Работаем с ПЛИС, области применения, выбор

Проблема такова: у меня есть Nios для отладки и есть мой модуль, которое подключается к нему через PIO-порты. К ниосу подходит 50 МГц и как-то там PLLится внутри ниос-системы. А к моему модулю подходит 100 МГц через отдельную PLLку, а затем - через ALTCLKCTRL. Когда я пытался всё это дело скомпилировать, то компилировалось всё, кроме этих клоков. Говорит: Error: Can't fit fan-out of node DoublePLL:comb_3|altpll:altpll_component|_clk0 into a single clock region Когда я пытался запитать Nios и мой модуль через два разных выхода одной PLLКи, то выдавало то же самое. Как сделать правильно? -

Понадобилась двунаправленная шина, что-то никак не разберусь, как её сделать. Решил сначала сделать тестовый модуль, чтобы понять, что к чему. Вроде всё по науке, однако он, зараза, всё равно не работает. По идее, по OE он должен что-то выдавать на bidirPort'у, а по !OE - просто читать с bidirPort'а и передавать на outPort. ModelSim компилирует, но смоделировать не может. Как исправить положение? Модуль: `timescale 1 ns/100 ps; module BidirModule ( input wire oe, inout[7:0] bidirPort, output[7:0] outPort ); assign bidirPort = oe ? 8'hFF : 8'bZZZZZZZZ; assign outPort = !oe ? 8'hZZ : bidirPort; endmodule Тестбенч: `timescale 1 ns/100 ps; module BidirModuleTB; wire[7:0] testOut; BidirModule underTest ( .oe(1'b0), .bidirPort(8'hFF), .outPort(testOut) ); endmodule

-

Собственно проблема такая: у меня на этой машине раньше стоял Eclipse, который я использовал для Python-разработки. Когда я начал работу с Nios'ом, поставив NII EDS (в отдельный от прежнего Eclipse каталог), то на Nios II EDS слетела перспектива Nios. В списке доступных перспектив её также нет. Простая переустановка Nios II EDS тоже не помогает. Что делать, как быть - положительно непонятно. P.S. Самый цимес в том, что Legacy Nios IDE ещё работает, а новое - нет.

-

Нет ли каких туториалов для написания компонентов под Nios? Вроде "этот шнур подключается сюда"?

-

SDXC - у кого есть спецификация?

Я.К. опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Собственно, сабж. Карточки в продаже есть, у кого есть спеки по ним? -

Вот он, тот злополучный тестовый проект. top.v там верхний уровень, если что. Посмотрите, может, хоть вы чего поймёте... NuclearDesign.zip

-

Приду домой - выложу. А то я уже всю мышку себе отмахал с этим Альдеком. ^__^

-

C Рутрекера. Там есть.

-

Собственно, сабж. Имею ещё вопрос: можно ли его как-то более или менее прилично использовать, не имея NIOSа?

-

Делал-делал. Даже модуль top появлялся. Я назначал его модулем верхнего уровня, он назначался. Однако симулировался строго тогда, когда я заказывал Functional Simulation в Design Flow. Дальше - больше, когда я решил попробовать засимулировать таким макаром самую простенькую память то у меня она собралась, однако не нашлась нижележащая LPM-ка altsyncram, хотя соответствующая либа и была прилинкована. Когда я заказал функциональную симуляцию в маршруте проектирования, то и тут всё внезапно заработало. Где справедливость?..

-

ActiveHDL 8.3 - cтранные глюки с симуляцией

Я.К. опубликовал тема в Среды разработки - обсуждаем САПРы

Как всегда, прошу квалифицированной помощи. Я собирался попробовать засимулировать одну корку в ActiveHDL, однако потерпел странное фиаско. Не симулируется вообще ничего, даже простой повторитель, который легко синтезируется и симулируется в Quartus'е. Я компилирую top.v с текстом `timescale 1 ns/100 ps module top(input inPort, output outPort); assign outPort = inPort; endmodule Делаю его "Set as top level", создаю awf'ку (симулятор вейвформ простой, не ускоренный даже) top.awf, перетаскиваю туда модуль top из Structure, жму "Initialize simulation". Выдаёт варнинги: # Selected Top-Level: top (top) # KERNEL: Warning: Cannot trace SLP signal `inPort' in standard Waveform module. Please use Accelerated Waveform Viewer instead. # Signal inPort not found in design # KERNEL: Warning: Cannot trace SLP signal `outPort' in standard Waveform module. Please use Accelerated Waveform Viewer instead. # Signal outPort not found in design Вешаю на inPort клоковый стимулятор, а мне и говорят: # KERNEL: Error: inPort does not have write access. Use switch +access +w_nets for this region. # Error: Cannot force signal inPort with formula 0 0 fs, 1 5000000 fs -r 10000000 fs. Жму "продолжить" на 100 нс, естественно, ничего хорошего не происходит. Выдаёт "Симуляция завершена" и выдаёт на все порты пустое значение. Все сигналы выводит как пустое значение. Не Z, не U, а именно пустое. Как это исправить? Странное дело: когда я запускаю аналогичную симуляцию через Design Flow, всё работает хоть как-то. Раньше работало и так, можно было не махать мышкой... -

Посоветуйте АЦП

Я.К. опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Кто что-нибудь знает, чтобы не делать вокруг обычного АЦП обвязки для согласования диапазонов? -

Отладочная плата SP605

Я.К. опубликовал тема в Работаем с ПЛИС, области применения, выбор

Доброго вечера. Пользовался ли кто-нибудь из нас сабжем и где его лучше покупать в Москве? -

Запись на Compact Flash

Я.К. опубликовал тема в Работаем с ПЛИС, области применения, выбор

Собственно, сабж. Проблема, к сожалению, снова встала перед нами. Кому приходилось такое делать? Кто чем пользовался? -

Моделирование антенны

Я.К. опубликовал тема в RF & Microwave Design

Доброго дня. Посоветейте мне что-нибудь почитать на следующую тему: у меня есть несколько антенн, разнесённых на несколько метров, которые принимают некий шумовой сигнал (диапазон 1400-1420 МГц), который затем нужно когерентно просуммировать. Я знаю распределение поля в любой точке пространства, мне нужна более точная модель зависимости сигнала на выходе антенны от поля на её входе, чем простая амплитудная диаграмма направланности. Что можно покопать из литературы? -

Контроллер флешки-CFки

Я.К. опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Доброго дня, товарищи. Кто-нибудь из нас знает хорошее, годное ядро для работы с Compact Flash на её полной скорости? Необходимо как воздух. Что у нас есть в загашнике? P.S. Язык использую VHDL, но и Verilog тоже сгодится. -

Микросхема DDR2

Я.К. опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Нет ли где указаний, как запитывать MT47H16M16? -

Altium для новых начинающих

Я.К. ответил Uladzimir тема в Altium Designer, DXP, Protel

Спасибо! -

Altium для новых начинающих

Я.К. ответил Uladzimir тема в Altium Designer, DXP, Protel

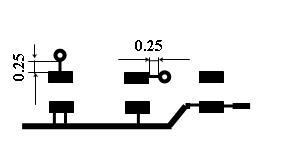

Кто знает, как выставить в Design Rules минимальное расстояние от контактной площадки до переходного отверстия этого же узла цепи? Я вот об этом: -

Не его же подать, конечно. Высокий уровень, поделённый вдвое, да.

-

Кстати, можно не думать долго, а сделать у FPGA LVDS-выходы и таки поставить конвертер с LVDS на TTL, выдав в качестве земли -2.5В. Кто знает хороший транслятор на 4 канала? Или даже так: использовать транслятор с LVDS на TTL, однако просто подать с FPGA на прямые входы неинвертированный сигнал, а на инвертированный - его же, только поделенный вдвое.

-

Чем преобразовать LVTTL от моей FPGA к +-2.5V?

Я.К. опубликовал тема в Форумы по интерфейсам

Есть FPGA с периферией 3.3V, и есть чип с логической единицей 2.5 и логическим нулём -2.5. Нужно передавать сигнал от FPGA к чипу, от чипа к FPGA - не нужно. Как такое сделать? Раньше у меня была пятивольтовая FPGA, там я пользовлся AM26C32, но теперь нужно что-то новое. Желательно - с 3.3V-питанием. Кто-нибудь что-нибудь знает? -

Посоветуйте компаратор

Я.К. ответил Я.К. тема в Цифровые схемы, высокоскоростные ЦС

Да, ещё один горький аспект: деньги. В моей схеме будет 2048 каналов, каждый из которых должен проходить через канал компаратора. Может ли кто показать кого-нибудь, походящего на LT1715 (в смысле, с раздельным питанием входа и выхода), может быть, с несколько худшими таймингами, только подешевле? И, может быть, в 4-канальных корпусах? -

Посоветуйте компаратор

Я.К. ответил Я.К. тема в Цифровые схемы, высокоскоростные ЦС

Я, наверное, всё-таки LT1715 возьму. Он вроде больше подходит. -

Посоветуйте компаратор

Я.К. ответил Я.К. тема в Цифровые схемы, высокоскоростные ЦС

Дело в том, что на моей плате маловато места. Нет ли чего-нибудь типа "Всё-в-одном"? Засада, полная засада...