-

Постов

9 579 -

Зарегистрирован

-

Победитель дней

4

Весь контент des00

-

Анализ исходников на С

des00 ответил RobFPGA тема в Управление проектами

пользовал Understand c/c++ мне понравилось(смотрел только эту прогу, так что аргументов нет), но если ковыряться в динамике то лучше скормить слику %) -

код в студию, телепаты в отпуске так работает или не работает ? ИМХО это не поможет, тут нужно править либо руки, либо голову и руки. :))

-

я вас правильно понял, интерполировать по двум информационным отсчетам промежуточный отчет и пропустить отчет этого "лишнего такта" и следующий за ним информационный через эквалайзер и детектор гарднера за один такт символьной частоты? Или этот отчет можно вытащить из интерполятора взяв его в середине между информационными отчетами ?

-

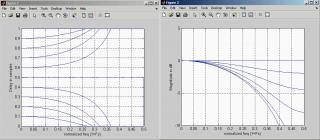

вот это мне тоже не понятно. В атаче АЧХ и ФЧХ фарроу первого порядка и простая модель с фарроу первого и второго порядка при mu = 0.5 при 2-х отчетах на символ. Если смотреть на ЧХ то видно что по идее, при 2-х отчетах на символ, будет полный ужас, но в модельке с первым порядком ошибка ~4.5 градусов, а с третим порядком ~1 градуса. Результат странный, но факт остается фактом. %( про эквалайзер понятно, надо уходить на 4 отсчета на символ. А как поступают в ситуации когда АЦП может дать только 2 отсчета на символ ? повышают частоту дискретизации интерполяцией в 2 раза и берут сигнал с интерполятора ? Спасибо. OSFx2.zip

-

хмм, я может быть что то не понимаю, но вот моделька для 2-х отчетов на символ. В модели использован самый простой линейный интерполятор. В данной модели есть расстройка частоты передатчика на 1кгц, если ее убрать (поставить в Signal Source -> Random Integer Generator -> Sample Time == 1/Fs) то видно что ошибка для QPSK составит 4.5 градуса. Если в этой модели использовать кубический интерполятор то ошибка составит ~1 градуса. Для моей системы эти ошибки допустимы, т.к. потом планируется поставить деджитер с аналоговым ГУНом. Расшифруйте пожалуйста что вы понимаете под словами ну очень плохо. Если судить по созвездию, то не все так плохо. Если посмотреть модель, то там вычисления идут последовательно и при расстройке частот да видны ухудшения (точки "булькают"), но при этом вроде как все работает. ----------------- Кажеться доходит вы имеете в виду что в этом случае дробный эквалайзер будет не успевать проводить последовательные вычисления со скоростью 2 отчета на символ, т.к. будет разрыв когда NCO возьмет отчеты каждый такт? если рассмотреть 2 генератора в приемнике и передатчике на одну частоту ~30МГц со стабильностью 100ppm, если я правильно понял ваш критерий то dF*1/2 << 1 будет выполняться и для непрерывных модемов. Или я ошибаюсь ? Есть ли среди ваших запасников статьи о feedback синхронизации по 2-м отсчетам ? :) Спасибо. timing_recovery_loop_2sps_first_order_R14.zip

-

Спасибо за ответ и отдельное спасибо MKS за модель. Я смотрел на интерполятор не с той стороны и рассматривал его как устройство у которого на входе 2 отсчета и на выходе 2 отсчета. А надо было смотреть как на входе 2 отсчета, а на выходе один. Тогда возник еще вопрос, в такой системе где должен стоять дробный эквалайзер работающей с двумя отсчетами на символ? До или после интерполятора? Спасибо. PS. глупый вопрос, почти уверен что до %)

-

http://ru.wikipedia.org/wiki/%D0%9C%D0%B5%...0%BE%D0%B2#HDB3 один из видов кодирования данных, обладающих свойством самосинхронизации, но за счет расширения полосы сигнала + есть еще пара вкусностей. кодирование 4/5, 8/10 и т.д. несет цель увеличить количество переходов в сигнале, для облегчения работы системы синхронизации. но имеет недостаток в виде расширения полосы(для передачи того же объема информации нужна тактовая выше). если расширение полосы не возможно то как вариант обработать данные аддитивным скремблером в приемнике и передатчике. http://en.wikipedia.org/wiki/Scrambler но в случае возникновения битовой ошибки у вас будет размножение ошибок. Надо закодировать сигнал на передающей стороне!!! кодирование на приемной смысла не имеет. Почему я вас и спрашивал : есть ли у вас доступ к передатчику или нет, если доступа нет, то все вышеизложенное не имеет смысла.

-

если есть доступ к источнику и хороший кабель то самое простое перевести все HDB3 и резать на тактовой в 4-8 раз выше. пройтись скремблером 7 кой самосинхронным, нарезать на тактовой в 4-8 раз выше и собрать сигнал(в доках у хилых такое есть) %).

-

восстановление тактовой частоты при двух отчетах на символ

des00 опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день! На данном форуме в темах про интерполяторы для восстановления тактовой/символьной частоты несколько раз встречал упоминание, что если ошибки вызванные влиянием интерполятора устраивают, то можно восстановить тактовую частоту всего при двух отчетах на символ. Собрал модель с кубическим интерполятором, действительно приемник цепляется и хорошо держится за фазу частоты передатчика (изменение фазы моделирую интерполятором). Но меня интересует вот какой вопрос. Промоделированная система это система в которой частоты передатчика и приемника равны, отличаются только их фазы. Будет ли работать такая система если частоты разные? Да частоты будут отличаются не сильно, но тем не менее они разные? Если частота передатчика ниже частоты приемника, то система будет работать, ошибка будет копиться и рано или поздно будет взят 1 отчет за 2 такта. Но что будет если частота передатчика будет выше частоты приемника? Ведь NCO в такой системе упирается в верхнюю границу по генерируемой частоте и он не сможет сделать так что бы взять 2 отчета за 1 такт. Или я не правильно понимаю принцип работы петли по тактовой для системы с интерполятором ? ЗЫ. Как я понимаю подобная ситуация не возникнет если в системе с интерполятором больше чем 2 отсчета на символ или в системе с ГУНом, который сможет дотянуть частоту. Спасибо! -

Вопрос по интерполятору Farrow

des00 ответил _sda тема в Алгоритмы ЦОС (DSP)

Господа гуру просвятите по этой статье. на странице 19 рассмотрена модифицированная структура фарроу, модификация заключается в удалении целой части задержки и использовании только дробной части. (подозреваю что у кубического интерполятора Nazami на стр.203, который используется в моделях petrov проведена как раз такая модификация). Для этого вводиться матрица трансформации, которая определяется формулой 3.109. Дальше рассмотрен пример для квадратного интерполятора. Собственно вопрос как в примере, при расчете по формуле 3.109 T(n,m) = round(N/2)^(n-m) for n >= m, для N = 2, n = 2, m = 1 получено T(2,1) = 2 ? Спасибо. -

хмм, ну какой то протокол у вас должен же быть. Как-то же вы должны были синхронизовать потоки. есть много вариантов. асинхронный UART самый простой, за счет расширения полосы вы получаете возможность привязки данных по фазе по старт-стоп битам. Есть варианты с канальным кодированием, есть с цифровой петлей ФАПЧ и т.д. Выбор конкретного варианта зависит от требований к реализации.

-

это просто был пример что при конвейеризации важно не только ставить регистры но и понимать куда их ставить. Тормоза вашего варианта заключались как раз в условиях над 20 ти битными векторами (regN < cTAB_CODE[indexN] и т.д.) их то я и разрулил. Комбинационная логика над 5 ти битными индексами меньше + завязана на константы, потому и быстрее, поэтому так в данном случае так можно сделать. Вот если вам потребуется 450 МГц, тогда нужно будет и индексы конвейеризировать %)

-

дык это же систем верилог, о чем квартус вам и говорит %) приатачил оба модуля странная аппроксимация, лог моделирования в атаче. если я правильно понял то по этому коду log(8,2) = 3.(128/256) = 3.5 не сильно ли большая ошибка. mlogtabdiv2.v mlogtabdiv2_inv.v

-

вот оно последствие VHDL :))) взял ваш алгоритм, делал на стратиксе 3, спидгрейт 4. ваш показал 190 МГЦ, чуть подправил module mlogtabdiv2 (input rst, clk, input [19:0] in, output logic [5:0] out); localparam int unsigned cTAB_CODE [0 : 63] = '{ 1, 1,2,2,3,3,4,5,6, 8,10,13,16,20,25,32,40, 50,63,79,100,126,158,200,251, 316,398,501,631,794,1000,1259,1585, 1995,2512,3162,3981,5012,6310,7943,10000, 12589,15849,19953,25119,31623,39811,50119,63096, 79433,100000,125893,158489,199526,251189,316228,398107, 501187,630957,794328,1000000,1000000,1000000,1000000 }; logic [5 : 0] index1; logic [5 : 0] index2; logic [5 : 0] index3; logic [5 : 0] index4; logic [5 : 0] index5; logic [19 : 0] reg1; logic [19 : 0] reg2; logic [19 : 0] reg3; logic [19 : 0] reg4; always_ff @(posedge clk or posedge rst) begin if (rst) begin index1 <= 32; index2 <= 32; index3 <= 32; index4 <= 32; index5 <= 32; reg1 <= '0; reg2 <= '0; reg3 <= '0; reg4 <= '0; out <= '0; end else begin reg1 <= in; if (in == cTAB_CODE[32]) index1 <= 32; else if (in < cTAB_CODE[32]) index1 <= 16; else index1 <= 48; // reg2 <= reg1; if (reg1 == cTAB_CODE[index1]) index2 <= index1; else if (reg1 < cTAB_CODE[index1]) index2 <= index1 - 8; else index2 <= index1 + 8; // reg3 <= reg2; if (reg2 == cTAB_CODE[index2]) index3 <= index2; else if (reg2 < cTAB_CODE[index2]) index3 <= index2 - 4; else index3 <= index2 + 4; // reg4 <= reg3; if (reg3 == cTAB_CODE[index3]) index4 <= index3; else if (reg3 < cTAB_CODE[index3]) index4 <= index3 - 2; else index4 <= index3 + 2; // if (reg4 == cTAB_CODE[index4]) index5 <= index4; else if (reg4 < cTAB_CODE[index4]) index5 <= index4 - 1'b1; else index5 <= index4 + 1'b1; // out <= index5 - 1'b1; end end endmodule получил 208 МГц подправил чуть больше assign index1 = in_eq ? 32 : (in_less_eq ? 16 : 48 ); assign index2 = reg1_eq ? index1_reg : (reg1_less_eq ? index1_reg - 8 : index1_reg + 8 ); assign index3 = reg2_eq ? index2_reg : (reg2_less_eq ? index2_reg - 4 : index2_reg + 4 ); assign index4 = reg3_eq ? index3_reg : (reg3_less_eq ? index3_reg - 2 : index3_reg + 2 ); assign index5 = reg4_eq ? index4_reg - 1 : (reg4_less_eq ? index4_reg - 2 : index4_reg + 0 ); always_ff @(posedge clk or posedge rst) begin if (rst) begin in_eq <= 1'b0; in_less_eq <= 1'b0; reg1_eq <= 1'b0; reg1_less_eq <= 1'b0; reg2_eq <= 1'b0; reg2_less_eq <= 1'b0; reg3_eq <= 1'b0; reg3_less_eq <= 1'b0; reg4_eq <= 1'b0; reg4_less_eq <= 1'b0; index1_reg <= 32; index2_reg <= 32; index3_reg <= 32; index4_reg <= 32; reg1 <= '0; reg2 <= '0; reg3 <= '0; reg4 <= '0; out <= '0; end else begin reg1 <= in; in_eq <= (in == cTAB_CODE[32]); in_less_eq <= (in < cTAB_CODE[32]); // reg2 <= reg1; reg1_eq <= (reg1 == cTAB_CODE[index1]); reg1_less_eq <= (reg1 < cTAB_CODE[index1]); index1_reg <= index1; // reg3 <= reg2; reg2_eq <= (reg2 == cTAB_CODE[index2]); reg2_less_eq <= (reg2 < cTAB_CODE[index2]); index2_reg <= index2; // reg4 <= reg3; reg3_eq <= (reg3 == cTAB_CODE[index3]); reg3_less_eq <= (reg3 < cTAB_CODE[index3]); index3_reg <= index3; // reg4_eq <= (reg4 == cTAB_CODE[index4]); reg4_less_eq <= (reg4 < cTAB_CODE[index4]); index4_reg <= index4; // out <= index5; end end получил 248 МГц. все это не меняя алгоритм.

-

Во первых причем здесь ария жиикс ? разговор идет про сыклон 2. повторяю еще раз для тех кто в танке, в сыклоне 2 подать сигнал на PLL можно ТОЛЬКО со входных ног. О чем в даташите черным по белому нарисовано и написано. если вы ЭТО сделаете сообщите об этом в первую очередь фирме альтера, что нашли недокументированную фичу сыклона 2 %))

-

Read The Fucking Manual тем более если про каскадирование ни слова, то это уже намек что его делать нельзя :) а вот тут указано точно, что можно подать на вход плл сыклона 2 Cyclone II Device Handbook, Volume 1 -> Chapter 7. PLLs in Cyclone II Devices -> Cyclone II PLL Hardware Overview -> Figure 7–2. Cyclone II PLL Block Diagram

-

RTFM!!!! там написано что каскадировать PLL в этом семействе нельзя.

-

Добрый день! У меня как раз вопрос по этой модели и детектору годдарда. если в модели оставить только годдарда и убрать искажения в канале, то видно что созвездие нормально не восстанавливается. Значит ли это что использовать в эквалайзере только критерий годдарда не рекомендуется ? В той же статье, годдард рекомендует что как только раскроется глазок, переходить на адаптацию эквалайзера по решению. Спасибо. ЗЫ. Под "нормально" я понимаю сравнение созвездия с модемом в котором используется критерий настройки по решениям.

-

Редакторы HDL

des00 ответил zorromen тема в Среды разработки - обсуждаем САПРы

посмотрел новый слик, блин все равно с косяками разбирает файл, причем если систем верилоговский разбирает еще более менее, то с верилоговским такая засада %( но вообще существенный прогресс налицо %) -

как уже писал квартус тупо не видит импортированый глобально пакет, даже если все описано в одном файле, насчет количества файлов это уже мои умозаключения, основанные на использовании квартуса и поиска объяснений его действий в стандарте %)

-

VHDL: IEEE1076-2008

des00 ответил cms тема в Языки проектирования на ПЛИС (FPGA)

Понимаю что оффтопик, но все же скажу, и да простят меня модераторы. если я правильно помню AHDL, то использование интерфейсов в данном случае не корректно, в объявленном интерфейсе можно получить иерархический доступ до любого сигнала объявленного в нем. Что в случае использования модуля противоречит инкапсуляции в объектном подходе в хдл. подключение портов "где попало" реализовать в SV можно легко, будет крайне удобная, но местами опасная фича (уже писал почему), но вот сделать подобный сумматор это врядли, т.к. это уж сильно выбивается из концепции языка %) -

нет недостаточно, нужно задать set_input_delay -max/min, смотрите по этому поводу an433 :: Constraining and Analyzing Source-Synchronous Interfaces удачи !!!

-

я столкнулся с этим именно при синтезе когда ква не увидел глобально импортированных пакетов, затем стал ковырять далее, результаты я привел. использовать макросы для импорта пакетов можно, но ИМХО это не серьезно последнее время у меня квеста валиться только когда ее заваливаю в ручную, констрейны хитрые или с классами экспериментирую %)

-

столкнулся с этим при синтезе проекта, искал ответ в стандарте, но четкого ответа не нашел. после ковыряния данной проблемы я сделал следующий вывод. Импорт пакета вне членов иерархии (т.е. в глобальный unit) не корректен, в частности с точки зрения синтеза, все файлы рассматриваются как один compilation unit и возникает ошибка переопределения констант, параметров и прочего. В этом неудобство в отличие от вхдлного use pkg.all, который действует в пределах только одного файла. решения проблемы я нашел два : 1. использовать scope resolution operator при использовании содержимого пакета в портах - метод рабочий, но корявый. писанины много 2. использовать старый стиль - описание портов размещать после описания интерфейса и импортировать пакет до описания портов - мне такой метод удобен, т.к. такую "красоту" за меня делают скрипты (хотел выложить этот скрипт для всех, но как я понял это не актуально :) ). ЗЫ. Ответ на данную проблему пробегал в логах обсуждений комитета по SV, по ссылке которую вы давали. Там я просматривал обсуждение возможности импорта пакета в секции интерфейсов, ссылку уже не помню.

-

вообще задачка занятная, проковырялся пару дней, расковырял проект до чип едитора, вытащил все задержки из кристалла, но так и не понял как TimeQuest считает Data Required Time для пути fr[1]/fr[2] для quest. Еще интересно почему он не учитывает длину пути между пинами fr[1].regout -> quest.clk и их соотношение к клоку. Господа гуру просветите что не так в этом примере ? ЗЫ. Как вариант напишите в саппорт альтеры, пусть прояснят ситуацию.