-

Постов

629 -

Зарегистрирован

-

Посещение

-

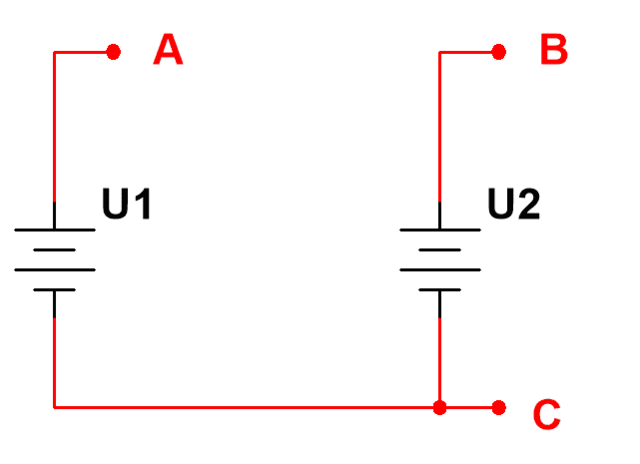

Тут на работе с другом получилась дискуссия за метрологию. Грубо: Есть будка, собака, миска (находятся на одной прямой) и линейка с известной погрешностью. Мы измерили расстояние от будки до собаки и расстояние от будки до миски. Расстояние от собаки до миски вычислили как разность измеренных расстояний. С какой погрешностью получен результат? Условие задачи: У нас есть вольтметр постоянного напряжения, который имеет абсолютную погрешность измерений ±0.01*Ux ± 0.001В, где Ux – измеряемая величина напряжения. Индикация измеренных значений на табло вольтметра производится шестью цифрами. Линейность этого вольтметра столь высока, что будем считать его абсолютно линейным. Вольтметр имеет нулевой температурный и временной дрейф. Т.е. мультипликативная погрешность ±1%, аддитивная ±1мВ. Есть два источника постоянного напряжения U1 и U2, о которых мы знаем, что они имеют нулевой температурный и временной дрейф, т.е. будем считать их идеальными. Электрическая схема (см. приложение) Для упрощения задачи будем считать, что источники напряжения и соединительные провода имеют нулевое выходное сопротивление, а вольтметр имеет бесконечно большое входное сопротивление. Мы подключаем вольтметр к источнику U1 (измерения производятся между точками A и C), на индикаторе прибора имеем показания Uac = 1.01000 В. Значение на индикаторе стабильно (младшие разряды не болтаются). Мы подключаем вольтметр к источнику U2 (измерения производятся между точками B и C), на индикаторе прибора имеем показания Ubc = 1.00000 В. . Значение на индикаторе стабильно (младшие разряды не болтаются). По каким-то неведомым причинам я не могу провести прямые измерения напряжения между точками A и В, поэтому я решаю вычислить его: Uab = Uac – Ubc. Получаю результат вычислений Uab = 0.01000 В Теперь вопросы: 1. С какой погрешностью я получил результат Uab ? 2. Как называется метод (или вид) измерений, который я применил для получения значения Uab ? Мои варианты ответа (поправьте, где я ошибаюсь): Ответ на вопрос 1: Оба измерения (Uac, Ubc) производятся одним и тем же вольтметром, по условиям задачи прибор абсолютно линейный и не имеет дрейфов. Поэтому справедлива такая математика: Uac = M * U1 + A ± 1/2ЕМР; Ubc = M * U2 + A ± 1/2ЕМР; Где: Uac, Ubc – значения считанные с индикатора вольтметра, U1 и U2 – истинные напряжения источников, M – коэффициент, учитывающий мультиплекативный компонент погрешности прибора (находится в диапазонах значений от 0.99 до 1.01, т.к. по условиям задачи мультипликативная погрешность = 1%) A – аддитивная погрешность измерений, находящая в диапазоне значений от -0.001 до +0.001 В. ±1/2ЕМР – половина единицы младшего разряда индикации При вычислении Uab получаем: Uab = Uac – Ubc Uab = ( M * U1 + A ± 1/2ЕМР) – (M * U2 + A ± 1/2ЕМР) = M * (U1 – U2) + 0 ± ЕМР. Таким образом (с учетом единицы младшего разряда) значение Uab получено в данном эксперименте с абсолютной погрешностью ±0.01 * Uab ± 0.00001 В. Данный метод применим только при измерениях обоих напряжений Uac и Ubc одним и тем же прибором в одном и том же измерительном диапазоне, что позволяем исключить аддитивную погрешность как систематическую. Ответ на вопрос 2: Данный метод относится к косвенным измерениям.

-

Открываете государственную поверочную схему для средств измерений силы переменного электрического тока и прикидываете, возможно у Вас появился шанс изобрести новый государственный первичный эталон.

-

Мы в описании типа честно указали абсолютные погрешности измерений с мультипликативной и аддитивной компонентой. Это для умных людей. Мы честно указали разрядность АЦП и ЦАП. Это для людей, принимающих решения. Вот Вам ещё пример: мой любимый лабораторный мультиметр 6 1/2 знака Keysight 34465A в частотном диапазоне от 10Гц до 20кГц при измерении переменного напряжения имеет "годовую" погрешность 0.05%*Uизм+0.02%*Uдиап. Т.е. при измерении 9.99В скз получаем абсолютную погрешность = 0.0005*9.99+0.0002*10 = 0.007В. log(10/0.007) = 3.16 < 3 1/2. Обманули дурака на четыре кулака на три знака.

-

Я с АКИП-ом не работал за него не скажу, но парочка Keysight 34465A подключенных по USB у нас на фирме ведут себя прекрасно.

-

Мне кажется, что Вы сами себе усложняете задачу. Насчет "тормозной" я бы поспорил. Современные "бюджетные" мультиметры (Keysight 3446xA) дают сотни-тысячи измерений в секунду в режиме постоянного напряжения. Подключаетесь к нему по USB и вперёд по кочкам. Предполагаю что у АКИП тоже есть такая возможность. См. секцию 5.1. https://www.analog.com/media/en/training-seminars/design-handbooks/Data-Conversion-Handbook/Chapter5.pdf

-

Могу, конечно, ошибаться, но "некоторые более правильные изготовители измериловки" - это компания, продающая приборы под торговой маркой INWAVE, а прибор - что-то из серии MWR (https://inwave.ru/upload/iblock/e55/5vzlsf34k0oqzsq0v8ql264srw4u3lp4/MWR_series_datasheet.pdf). Пришел к такому выводу из-за дословного совпадения формулировок на Вашей картинке и в технических параметрах. К сожалению, этих приборов в Государственном реестре средств измерений я не нашел (но не факт, что они не входят в закрытый спец.раздел). Соответственно, с какими параметрами они внесены в гос. реестр я не знаю. Зато нашел INWAVE MWT. По заявлениям производителя: Спектральная чистота • Ультранизкий фазовый шум (-140 дБн/Гц тип. при отстройке 10 кГц от несущей 1 ГГц) • Ультранизкие негармонические искажения <-81 дБн • Низкий уровень гармоник (-53 дБн тип.) По описанию типа (приложение к свидетельству 69067😞 Спектральная плотность мощности фазовых шумов на частоте 1ГГц при отстройке от несущей 20кГц при уровне выходного сигнала 20 дБм : -128 дБн/Гц Уровень негармонических спектральных составляющих при уровне выходного сигнала -10 дБм : -65 дБн Уровень гармонических спектральных составляющих (в ОТ много цифр), но : от -28 до -47 дБн Я полагаю, что "некоторые более правильные изготовители измериловки" также столкнулись с проблемой подтверждения параметров на том оборудовании что есть в ЦСМ-ах, поэтому и занизили цифры в ОТ.

-

Температурному дрейфу подвержены все компоненты схемы, не только ИОН. Так что при выборе оборудования следует опираться на параметры подтверждаемые (ну или хотя бы заявляемые) производителем, а не надеяться, что накрыв ИОН спичечным коробком получите цифры в 10 раз лучше. Вообще какая погрешность измерений Вам нужна по постоянному и переменному напряжению и в каком температурном диапазоне должно работать оборудование?

-

Для нашего оборудования с частотным диапазоном 0.1Гц - 106кГц попадаем на поверку на оборудовании класса APX5xx (Audio Precision) R&S UPx (Rohde & Schwarz) DS360 (Stanford Research) и в метрологических лабораториях это оборудование должно быть эталонным. Если какие-то параметры отсутствуют в описании типа, то это ещё не значит что прибор плохой, а производитель жулик. Даже глыбы вроде National Instruments для измерительных модулей аналогичного назначения (PXI/PXIe 4461) не вносят в описание типа сложные для подтверждения параметры. https://www.ni.com/docs/en-US/bundle/ni-4461-4462-specs/resource/373770k.pdf https://fgis.gost.ru/fundmetrology/registry/4/items/1229091 https://fgis.gost.ru/fundmetrology/registry/4/items/354350 Вот методика от конкурирующей компании по определению динамического диапазона регулирования: https://vibrationresearch.com/wp-content/uploads/2018/07/ExaminingDynamicRange-VR9500.pdf Наиболее сложный тест это "Random Loop-Back Test" по китайскому стандарту JJG 529-88. Из практики наших поставок: большинство виброиспытаний проводятся в диапазоне частот от 3Гц до 2500Гц, реже от 0.1Гц до 5000Гц, единичные случаи до 20кГц. Без термостата.

-

Ну да. Разрабатываем, производим и продаём. Это системы управления вибрационными испытаниями, но в режиме сбора данных они тоже работать умеют.

-

Обвязка АЦП не сильно отличается от рекомендаций AN-1384. Конкретную модель ИОН не буду писать, но это малошумящий с низким температурным дрейфом дешевле 10$. Измерительные каналы при наладке прибора калибруются. Проводили испытания прибора в термокамере от 0 до 50 градусов, метрология в пределах параметров из описания типа с большим запасом.

-

Чем больше параметров указано в описании типа и чем они "круче" тем больше времени занимает поверка и тем более "крутое" оборудование должно быть у поверительной лаборатории. Соответственно дороже поверка и далеко не каждый ЦСМ берётся за поверку. Часть измерений в нашем оборудовании производится после пропускания сигнала через узкополосные цифровые фильтры, соответственно подобрать внешнее оборудование (которое должно являться эталонным средством измерений) для подтверждения параметра проблематично. По ВС-407М динамические диапазоны из описания типа убраны сознательно, они подтверждаются ОТК. В ВС-407(без буквы М) этот параметр в ОТ присутствует и подтверждается в методике поверки (см. https://fgis.gost.ru/fundmetrology/registry/4/items/381165). Приборы производятся нами чтобы их продавать. Продавать приборы хотим не только мы. Соответственно метрологические параметры должны устраивать заказчика а дополнительные цифры и фичи в описаниях типа, руководствах пользователя и т.п. должны проходить по условиям тендера. А как это подтверждать? Я Вам открою страшную тайну: современные сигма-дельта АЦП имеют разрядность от 1 до 6 бит, остальные биты генерируются математически и они "нечестные". Для лучшего понимания различий 16 и 24 битных АЦП советую прочитать раздел "noise performance and resolution" в даташитах AD7761 (стр.28-29) и AD7768 (стр. 43-44), обратите внимание на шумы АЦП на низких частотах "дискретизации" (8 ksps). Для обоих моделей АЦП они одинаковые. Только вот у 16 битной модели этот шум составляет 1/64 единицы младшего разряда. Точно такая же ситуация возникает при полосовой фильтрации в алгоритмах обработки, для малых сигналов 16 бит данных недостаточно.

-

Случайно не генератор на мосту Вина изобретаете? Если да, то Вам сюда: http://www.janascard.cz/aj_Vyrobky.html http://www.janascard.cz/PDF/An ultra low distortion oscillator with THD below -140 dB.pdf

-

Техническая сторона вопроса: Не надо путать вольтметр (чем меньше погрешность тем лучше) и виброанализатор (чем шире динамический диапазон тем лучше). Динамический диапазон и отношение сигнал-шум. Мы используем AD7768 (24 бита, SNR = 108дБ), у этой АЦПшки есть 16-битный близнец AD7761 (у меня есть подозрение, что кристалл у них одинаковый). У 24-битной модели эти параметры на 10 дБ превосходят 16 битную модель (см. даташиты). Если взять хрестоматийную формулу SNR = 6.02N + 1.76dB, то из 16 бит больше 98 дБ не выжать. Значения погрешности измерений и неравномерности АЧХ вносились в описание типа исходя из того, чтобы быть не хуже конкурентов и чтобы для первичной и периодической поверки можно было бы обойтись оборудованием имеющимся в региональных ЦСМ. Реально для задач виброметрии погрешность менее 1% не нужна, нужен большой динамический диапазон. Показометрическая сторона вопроса: 1. А почему бы и не поставить 24битную сигма-дельту вместо 16 битной ? Цена вопроса не столь велика. 2. Конкуренты (из недружественных и дружественных стран) используют 24/32битные аудио АЦП и ЦАПы, не стесняясь писать об этом в описаниях типа и рекламных материалах, умалчивая про "аудио". 3. Разрядность АЦП попадает в технические требования при тендерных закупках, когда написано "Разрядность АЦП: не менее 24", меня с 16-битами отсеют ещё на этапе подачи заявок. 4. Решение о покупке той или иной системы зачастую принимает человек вообще не понимающий смысл терминов "погрешность" и "динамический диапазон", главное чтобы цифры были круче.

-

Всё в гос.реестре средств измерений. Могут работать в режиме сбора данных. 24 бита, дискретизация до 265тыс. семплов на канал, честная, без мултиплексирования. +/-10В, +/-1В. https://visom.ru/catalog/ https://fgis.gost.ru/fundmetrology/registry/4/items/1401101 Отечественная разработка и производство.

-

Питание ПЛИС

sysel ответил Styv тема в Работаем с ПЛИС, области применения, выбор

Китайские многоканальные понижающие конвертеры уже кто-нибудь применял?