faa

Свой-

Постов

786 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент faa

-

This FTP-server is not working.

-

Перевод GUI

faa ответил faa тема в Бесплатные САПР: KiCAD, EasyEDA, EAGLE и др.

Спасибо за проделанную работу. Постараюсь попереводить при возможности, вернее, уже начал. Но со свободным временем тоже не густо. -

И я бы ядро еще обновил. Мы на своих цинках (10, 20, 45) как минимум 4.9 крутим. Да и при начале проекта, ЕМНИП, на 3.18 тоже проблем не было. #dmesg|grep PS e0000000.serial: ttyPS0 at MMIO 0xe0000000 (irq = 26, base_baud = 6249999) is a xuartps console [ttyPS0] enabled e0001000.serial: ttyPS1 at MMIO 0xe0001000 (irq = 27, base_baud = 6249999) is a xuartps Не перекручены уарты. Jury093 правильно намекает ;)

-

Ну тогда начнем от печки. Что за плата? С железом все в порядке?

-

Вывод dmesg будет? Или все заработало?

-

В dts оба UART присутствуют. console на ttyPS0, выводу не мешает. Может скорость и режим на приемной стороне ttyPS1 не те установлены? Для диагностики нужен вывод команд dmesg stty -F /dev/ttyPS0 -a stty -F /dev/ttyPS1 -a

-

А console куда пристегнута? Покажите эту часть dts.

-

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Основное чуть не забыл, мы четыре потока под 5ГБ каждый в одну машину толкать пытаемся ;) 2 в одну ноду, 2 в другую. Если интел - в разные камни. Если EPYC - делим на 4 ноды. С gigabyte все неплохо. Работает, биос полный - есть доступ ко всем параметрам, техподдержка отзывчивая и толковая. Супермикро: Работает плохо. Жлобы, за каждый чих хотят денег. Биос обрезан - параметры далеко не все, подкрутить ничего нельзя. ТП - динамисты и футболисты. Это если коротко. ЗЫ: Всех с наступающим 2022 НГ! -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Kintex 7 даже через кабель - вопросов не было, gen2 же. Kintex US через кабель - проблемы были. Поддержка xilinx спросила "хоть где-то работает?". На ответ "да" послали к вендорам хостов ;) Virtex 7 не использовали. -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

А ПЛИС какие? Платы в слот вставлялись или через кабель 2м и свитч/ретаймер? -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

А никто и не требовал постоянной пиковой. Нужна была постоянная скорость в ~0.6 от пиковой (с учетом оверхеда и размеров TLP) для Ген3х8. Буфера были. Многоуровневые. Перед коркой PCIe фифо толстое, перед фифо буфер в ddr. Не считая буферов в конвейере. Про архитектуру современных ЦПУ немного в курсе. Но, ИМХО, EPYC поправильнее сделан по сравнению с интел. Скоро еще aarch64 попробуем. Вот тогда и посмотрим "чьи лыжи не едут" ;) -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Замирания при записи в системную память по dma. При этом биос был настроен с учетом всех рекомендаций mellanox и прочих HTS/HPC. Операционка тоже настраивалась: изоляция ЦПУ, выключение irq-balance и т.п. Проблема была именно в замирании транзакций по PCIe. На форуме интел я нашел, что народ жаловался на такие же замирания. Какой-то инженегр (по нику не поймешь кто) из интела отписал, что "да, жалуются, поправить можно, какие-то биты в msr, уточню-отпишусь". И затих. Замирания на интеле были на десятки миллисекунд. С чем связано - хз, возможно с архитектурой. На ксеонах до скалябельных было очень плохо, на больших постоянных потоках не работают. В пике неплохие цифры показывают, но недолго :) Скалябельные первые и вторые чуть лучше, но тоже замирания были. Измеряли по длительности сигналов full в буферных фифо. Можно поискать результаты, но уже почти 4 года прошло. Проще заново промерять. ;) Если время будет. У интела еще явная проблема - приоритет доступа к контроллеру памяти со стороны dma pcie один из самих низких. Может это как-то настраивается, но либо это тайна, либо никто не знал, да еще и забыл. Про EPYC надо писать отдельно - там много. Замирания может и не пропали, но заработало устойчиво вот на таком железе: MZ31-AR0-00, биос version: R06. В конторе есть еще несколько железок под EPYC, по ним тоже есть статистика. Местами не очень хорошая ;) Особенно по супермикро :( -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Почти тот же. А в чем противоречие? ;) Что на Интеле были замирания? Заменили хосты на EPYC 7002 и все стало хор и ок. Замираний нет, рестартов нет, потерь нет. Аптаймы - пока не выключишь. Тут еще AMD дает утилитку интересную. Ну и тюнинг сервера нужен, у AMD есть рекомендации. -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

-

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Под линуксом мы и пишем прямо в gpu. Только gpu д.б. quadro/tesla/ampere и т.п., где разлочена прямая запись. -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Нет. Это ж Церн ;) Наши драйвер виндовый сами писали. Там все довольно просто. Но под виндой 96МБ dma буфер только был. Больше 7-ка не дает сделать. А под линуксом на х86_64 до 1ГБ на дескриптор через hugepage-1GB. И scatter-gather не нужен. Родной драйвер cmem тоже работает, но с hugepage программистам проще показалось. Нужно только конвертировать адреса из virt в phys через ioctl. И да, cmem на больших размерах буфера очень долго их может выделять (пока он непрерывного пространства страничками по 4К наберет). -

PCIe and FPGA

faa ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

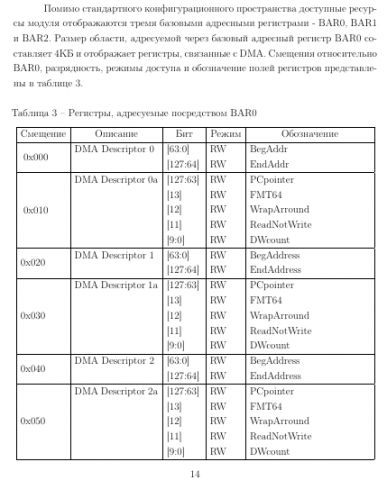

Есть проект wupper на opencores. Работает. Под 6 ГБ/сек на Gen3 x8 по DMA выдает. Больше нам не надо было. Драйвера и софт в комплекте. В драйвере надо надо включить pci bus master - там этого нет :) У нас работает на xilinx Kintex 7 (XC7Z045) и US (XCKU085). Правда, под 45 Zynq пришлось переписывать довольно много. Но там есть фича - каждую TLP пытается писать по следующему свободному дескриптору. Но это довольно просто лечится. -

Реализация извлечения корня

faa ответил _sda тема в Языки проектирования на ПЛИС (FPGA)

Помнится, пришлось применить метод Понселе Посмотрите, может точности хватит. -

Версия какая? Был не так давно баг, что не попадала в расчет длины при тюнинге часть проводника, которая оказалась в паде. В 5.99 было много косячков в тюнинге. Что-то из них поправлено, но еще могли остаться.

-

KICAD::допиливание

faa ответил _Pasha тема в Бесплатные САПР: KiCAD, EasyEDA, EAGLE и др.

Опять всплыли миллиметровые сетки в схематике. Уже столько воздуха насотрясали по этому вопросу... ГОСТ 2.701-2008 п.5.4.2 (Выделено мной). И нигде не сказано, что этот шаг д.б. строго кратен миллиметру. В п.5.3.4 указаны минимальные расстояния между элементами. Даже дюймовая сетка позволяет их выдерживать. Нормоконтроль (наш) уже успокоился. А тут все бурления какие-то :( -

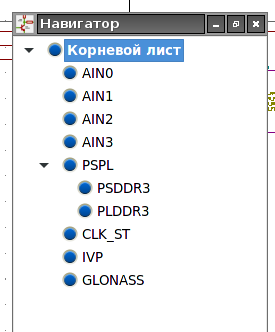

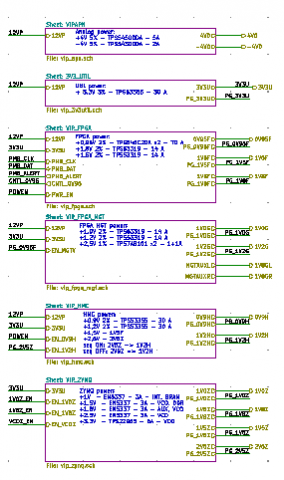

Постоянно делаем многолистовые схемы. Есть схемы с повторением листов, т.е с повторением частей схемы. На верхнем уровне эти листы подключаем к разным цепям, нетлист формируется правильно, КЗ и пересечений не замечено. По нумерации листов: ЕМНИП, нумерация листов идет по внутренней последовательности, которая определяется таймштампом листа (т.е. временем создания). Причем, номера листа присваивается сразу при создании листа. Может сейчас в ветке master это перепилили - там в программерах появилось много новых лиц и еще больше идей ;) Я сижу на ветке 5.1 - там, КМК, поведение при нумерации листов не изменилось. Т.о. разбивку схемы по листам приходится продумывать до начала рисования. Я обычно на корень кидаю листы в нужной мне последовательности. Если уровней больше двух, то сначала шагаю внутри листа по иерархии. Госту не совсем соответствует (там надо по листу сверху-вниз, слева-направо), но при печати и для понимания схемы, ИМХО, правильнее получается. Т.е. на корне номера листов с пропусками, если на некоторых листах уровней больше одного. Далее заполняю листы, а потом уже соединяю их по иерархии и на корневом. Пример с использованием одного файла схемы для 4 разных листов прикрепил. Пример иерархии листов прикрепил, номера листов сверху вниз. ГОСТ допускает иерархические метки, только сами метки в кикаде не соответствуют ГОСТу. По ГОСТу надо стрелочки, но там есть послабления при машинном черчении. Нормоконтроль не сильно бухтит. Вписать на _окончательной_ схеме номера листов в прямоугольники листов можно текстом. Я там еще пишу текстовку, интересную мне. Пример прикрепил. Не замечал изменение нумерации листов при перетаскивании прямоугольников листов.

-

И где это написано? ЗЫ: мы их очень давно используем и не знаем об этом ;)

-

NB6L11 можно, если jitter и skew устроит. По входу может LVPECL, LVDS, CMOS. Если swing нужен больше (пр длинном кабеле или больших потерях в нем), то 10EP89 - у нее до 800мВ, но с джиттером похуже. На приеме балун нужен на трансформаторе типа TC1-1-13 и та же NB6L11. Стыковка LVPECL с LVDS есть в апнотах от OnSemi.

-

back drill - гуглится сразу. Отвечаю по порядку: Головой разработчиков и глазами. А при выпуске герберов есть соответствующие галочки, если вдруг они (разработчики) пропустили. Вывод в какой файл? pdf нужен? Меню Файл - Печать. Все в цвете и алфавитном порядке имен слоев, слой на страницу. Нет. Для одинаковых каналов схема одна, вернее файл схемы. Листов столько, сколько каналов. Все эти листы с каналами ссылаются на один файл. Можно иерархически. ЗЫ: Есть вполне приличная документация. Стоит прочитать, для начала можно по диагонали. Роликов на youtube полно, некоторые полезно посмотреть.

-

А по джиттеру, разбегу-повторяемости какие требования?