Dec_NN

Свой-

Постов

92 -

Зарегистрирован

-

Посещение

Весь контент Dec_NN

-

Квартус сам размещает исключительно на логических ячейках. По поводу мегафункции Shift Register (RAM-based). Да я ее видел, собствено она и навела на мысль реализовать регистры на блоках памяти, но я понимаю использование ее только в схемном редакторе, как использовать сгенеренный VHDL файл в составе своего кода не знаю.

-

Использование памяти M4К под регистры

Dec_NN опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! FPGA - Cyclone II. Пишется проект на VHDL. Необходимо создать 4 сдвиговых регистра по 1024 бита каждый. Можно ли каким то образом указать, чтобы компилятор создал их не на основе логических элементов а на основе памяти M4K, чтобы не транжирить емкость кристала? -

Так ведь можно руками указать размещение кусков кода в памяти и при сборке они не наложаться друг на друга. А вообще надо посмотреть чего там в листинге по адресу 0059H находиться.

-

Описать все в одном процессе.

-

Может так: В режиме редактирования vwf файла: Edit --> Insert --> Insert Node or Bus --> кнопка Node Finder --> в фильтре выбрать нужную строчку и нажать лист.

-

А почему бы не сделать переменную cnt типа Std_Logic_Vector ?

-

Большое спасибо!

-

PFD в PLL

Dec_NN ответил SM тема в Работаем с ПЛИС, области применения, выбор

Меня тоже интересует вопрос возможности использования FPGAшной PLL в плане clock and data recovery. В настоящее время реализую выделение тактовой из сигнала на сдвиговых регистрах с помощью "увосьмеренной" частоты, там PLL тоже используется, но только лишь для умножения опорного клока на 8 :) -

Добрый день. Попрошу у имеющих доступ к opencores вот эти 2 проекта : http://www.opencores.org/projects.cgi/web/e1framer/overview http://www.opencores.org/projects.cgi/web/...esizer/overview

-

Монитор COM-порта под Windows

Dec_NN ответил altlogic тема в Интерфейсы

А какие требования необходимы? Если просто ansi терминал, то TeraTerm неплохая программка. Если нужно мониторить RTS, CTS и т.д. то из Freeware можно воспользоваться Comtest. Еще есть программка ZelaxTest. Мальнькая и удобная. -

Может все проще. RS-232 имеет топологию точка-точка (point-to-point) в принципе. Так что может быть упоминание P2P отражает ее (топологию подключения), а не какой то протокол. В даташите на ту железяку наверняка должны быть формат и описание выдаваемых данных.

-

Если нужно сделать в схемном редакторе, то можно поделить на 2, потом на 5. На 2 поделить например с помощью lpm_counter. Схема деления на 5 с 50% скважностью есть в приаттаченом файле. UnusualClockDividerspdf.pdf

-

Понятно. До этого я еще не добрался.

-

Извиняюсь за глупый вопрос :) А что это слово означает? Во многих топиках читаю, а понять не могу.

-

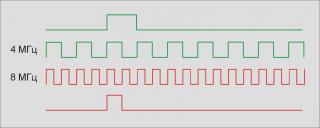

Спасибо. Думаю пока остановлюсь на варианте с 570 :), но может и еще чего придумаю. А вообще вот картинка. Зеленым то что мне приходит, красным то что надо сгенерить. Клок сделаю внешней штуковиной(ICS570), а фрейм уже в ПЛИС на D-триггере с установкой по зеленому фрейму и сбросом инвертированным зеленым клоком.

-

Там еще сигнал кадровой частоты присутствует привязанный к битовой частоте, поэтому необходимо фазирование. Можно конечно чего то наворотить-набуферить, но мне кажется синхронно работающая система будет прозрачней для отладки и надежней в работе. ICS570 как раз равняет фазы: входного, выходного и выходного/2 сигналов. Плюс к этому улучшенные параметры по джиттеру. Именно жесткая.

-

В даташите указано что она работает от 2 МГц, а вот насчет фаз это да, как сказано гуляют от включения к включению. Но нашел еще ICS570 - у нее фазы выровнены и работает так же от 2МГц (по крайней мере для моего случая). 4МГЦ - это битовая частота с которой определенный чип запихивает в ПЛИС последовательно данные (TDM шина). В ПЛИС необходимо их правильно разложить и выпулить с частотой уже 8МГц (в будущем 16МГц) в другую TDM шину. При этом всем чип выдающий 4МГц является мастером, т.е. от его частоты и приходится плясать. Тут и из альтеровской линейки можно найти, например stratix, но цена уже не на один порядок выше.

-

Так сделать нельзя. :rolleyes: Сигнал 4МГц выдается трансивером встраиваемого модуля и никуда от него не денешься.

-

Нет конечно, не только для этого. Там большой проект, причем половина уже сделана.

-

Я только начинаю работать с циклонами и тем более PLL поэтому видимо не все понимаю. У меня задача такая: есть внешние 4 МГц, чистый меандр со скважностью 50%. Нужно в ПЛИС получить из этой частоты другую, а именно 16 МГц , тоже меандр, тоже скважность 50%, совпадающую по фазе с исходной. У циклоновской PLL нашел 2 входа частот inclk0 и inclk1. Ни один из входов не работает при частоте ниже 10МГц. Вот и придется видимо получать эти 16 МГц снаружи ПЛИС.

-

Спасибо за развернутый ответ. Указанные вами синтезаторы с первого взгляда очень не плохие. Сейчас посмотрю подробней.

-

Ну что такое генератор я в курсе Не могу понять каким образом он мне поможет. Подскажите.

-

Вот, как раз вчера установил Q8.1 и обнаружил такую возможность . До этого тоже сидел на пятерке. Так что данный вопрос исчерпан. Всем спасибо

-

Вы имеете ввиду генератор управляемый напряжением, т.е. сделать свою PLL?

-

Вот как. У меня документ cyc2_cii51007.pdf. Там только раздел 7 - про PLL, без параметров. Грустно.