Politeh

Свой-

Постов

710 -

Зарегистрирован

-

Посещение

Весь контент Politeh

-

Добрый день! Есть интересная статья https://www.microsemi.com/document-portal/doc_view/133863-tn-201-ensuring-poe-surge-compliance, где разжевывают защиту PoE и что там происходит во время испытаний и т.д. Видимо одна из совсем немногих на просторах сети, где подробно объясняется. Но как всегда есть непонятные моменты. Вот, например, стр 8, последние 2 строчки: "We realize that reduction of Y-capacitance is one of the best ways for ensuring surge survivability, especially in AC-disconnect cases" - что тут подразумевается под "AC-disconnected cased"? Далее в статье это ещё встречается, и на схеме обозначено так же "DC disconnect". Т.е. что тут имеется в виду под этими режимами? Благодарю.

-

Спасибо, но там температурный диапазон от 0 до 70, а нужно минимум индустриальный. а для индустриального диапазона там цена очень высокая начинается, поэтому видимо на внешнем ЦАПе делать придется. Всем спасибо! Но видимо без внешних ЦАП никак, т.к. дороже выйдет для индустриального диапазона на УВХ и подобных.

-

Спасибо! Насчет ШИМа идея хорошая. Посмотрел - вроде достаточно точно можно работать с такой цепочкой.

-

Добрый день! Есть вопрос по поводу схемы увеличения кол-ва канало ЦАП из микроконтроллера. У микроконтроллера всего х1 ЦАП выход. А нужно х2. Есть два решения: 1. Повесить внешний х2 канальный на SPI 2. Использовать внутренний 12битный(точности с избытком достаточно для задачи) и сделать из него х2 канала с помощью внешних цепочек захвата с удержанием + мультиплексор. Выходной сигнал постоянный, т.е. тут какая-то полоса пропускания неважна. Подскажите пожалуйста, сталкивался ли кто-то с такой схемотехникой и какие подводные камни могут быть? Точность установки нужна около +\- 5мВ. Посмотрел цены на Sample/Track and Hold Amplifiers - оказывается недешевое решение если использовать готовую микросхему. Поэтому и рассматриваю вариант на рассыпухе, тем более, что тут неважна полоса сигнала. Скорость переключения между каналами должна быть <1мс. Благодарю.

-

Добрый день! Появились вопросы снова про подключение шасси к корпусам разъёмов. 1. Хорошо ли объединять корпуса разных разъёмов (RJ45 и USB) стоящих рядом c помощью полигона шасси на плате? Или лучше всё-таки подключать их раздельно к корпусу, чтобы контак был только через корпус, а не через медь на плате? 2. Почему в некоторых статьях рекомендуют ставить параллельную цепочку из резистора и конденсатора между минусом платы и шасси по обе стороны от разъёма RJ45, т.е.таких цепочки нужно 2? А если разъём RJ45 многопортовый, допустим 6 портов, то сколько таких цепей нужно? Благодарю.

-

" на 1/h21э меньше, т.е. порядка 99,5% от исходного" - да нет, смоделируйте и посмотрите. Там же получается верхний PN-переход у PNP транзистора - это диод на базу, вот туда и уходит прилично, если я не ошибаюсь. Я ставлю вход ОУ на измерительный резистор R11(через делитель) и он мне покажет падение на нём, с учетом того что 1.5мА делают падение больше 0.1В на 82Ом, даже с делителем этого достаточно, чтобы определить сколько там узлов. ОУ будет тотже что и сейчас на схеме, MCP6241, дешевый, а АЦП, что-то вроде ADC121S021CIMF. Ну и всё это изолированно должно быть. Поэтому ещё БП изолированный и цифровые изоляторы на цифровые сигналы.

-

ЦАП - это уже лишнее тут, мне так кажется. Размах передачи ведомых: 11-20мА примерно. А вот моделирование показывает, что как-то многовато уходит тока в базу при отсутствии там резистора на землю. Ну и при наличии резистора, при большом кол-ве ведомых - тоже достаточно много, что создает погрешность в подсчете кол-ва узлов.

-

Там ещё будет АЦП, который мерит постоянку и определяет кол-во слейвов. Погрешность из-за того, что часть тока уходит в базу транзистора T1 BC640. Я поэтому и поставил резистор R7, чтобы меньше туда уходило, но решил всё-таки мерить весь ток на верхнем плече, чтобы не зависеть от компонентов что ниже по схеме.

-

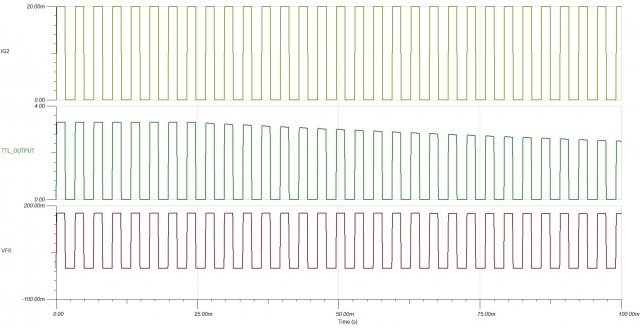

Убрал С1, всё стало нормально. Схему взял из справочника TI (Cookbook). Интересно почему так происходит? Этот кондер загибает сильнее характеристику на нижних частатах к нулю. В общем-то мне главное постоянку не пропускать, а реагировать только на переменку. Конечно всякий низкочастотный мусор в районе десятка Герц тоже было бы хорошо не пускать, но пока не знаю как это сделать на одном ОУ. Других схем пока не пробовал. Может что-то на Саллена-Кея лучше будет, но пока нет времени на оптимизацию решения. Нет, в вашем случае погрешность будет выше. при кол-ве слэйвов около 10шт, погрешность уже достигает около 1шт слейва.

-

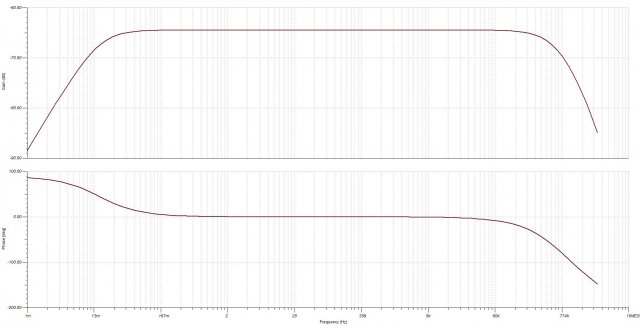

Падение амплитуды выходного миандра из ОУ.

Politeh опубликовал тема в Операционные усилители и АЦП

Добрый день! Кто может объяснить, почему амплитуда миандра падает со временем на выход ОУ? Пытаюсь доработать схему MBUS мастер трансивера, нужно приобразовать токовые импульсы в напряжение. Мне важна полоса 100Гц - 10кГц. Прилагаю: схему, АЧХ звена на ОУ, выходной сигнал во временной области. Спасибо. -

Варианты M-Bus

Politeh опубликовал тема в Форумы по интерфейсам

Добрый день! Может ли кто-нибудь в кратце сказать чем гостовский M-BUS отличается от оригинального стандарта? Хочу сделать схему вроде этой: https://github.com/rscada/libmbus/blob/master/hardware/MBus_USB.pdf, но изолированную и на число узлов около 10. Спасибо. -

Да, есть изолированный ИП на платке. Уже дошло, что от него нужно будет питать выход оптопары. Спасибо.

-

https://www.contec.com/support/basic-knowledge/daq-control/digital-io/#anc-06 Меня интересует схема "3-1-2. Photocoupler-isolated output (current source type and negative common type)". Как объяснить, почему биполярный транзистор будет находиться в открытом состоянии, когда падение на коллекто-эмиттер всего около 0.2В и меньше? Что тогда остается на базе? Как работает схема "3-1-1. Photocoupler-isolated open-collector output (current sink type)" - понятно. Спасибо.

-

Вопрос по поводу изолированных силовых выходов до 1А: в чем принципиальная разница между NPN и NMOS выходами? Почему-то в основном в схемах указывается именно NPN, его проще реализовать? Чем плоха приклепленная схема? Спасибо! Уже догадался - при открытом NMOS - падение напряжения будет на нагрузке и в итоге на затворе ничего не останется и транзистор закроется сразу. А для биполярного нужен ток базы и немного напряжения. Хотя на биполярном на коллектор-эмиттер тоже малое падение, но там эмиттер выхода оптопары цепляется на базу выходного биполярного и делителя не нужно, только ограничивающий R1.

-

Спасибо.

-

Библиотека для блок схем.

Politeh ответил Politeh тема в Altium Designer, DXP, Protel

Спасибо! Действительно классная вещь! -

Добрый день! Есть задача разработать универсальный модуль DI, DO, AI, AO для промышленного применения. Интерфейсы общения с хостом: SPI, UART, I2C. Модуль изолированный. Всего есть 5 пинов на клеммной колодке: один под минус, другие под сигналы. Модуль должен быть конфигурируемым, и могут быть следующие конфигурации: 1. х1..4 DI/DO, логический уровень 24В. DO - или открытый коллектор(300мА) или релейный. Т.е. любой вывод может быть как DI так и DO. 2. х2 АI, x2AO. AI: single ended, x12..16bit, 0..10В/4-20мА(configurable), AO: single ended, x12..16bit 0..10V, Также есть достаточное кол-во GPIO от хоста, чтобы попробовать сделать конфигурацию выводов полностью программную, если это возможно. Пока что вижу следующий вариант: цифровые изоляторы естественное на SPI, чипселектов есть 2-3, поэтому переключаемся между чипами ADC/DAC SPI. Аналоговые входы между 0..10V и 4-20мА конфигурируются включением точного резистора между AI и минусом, видимо мультиплексором или транзистором. Дискретные входы реализовать прямо на ADC через делитель с мощными резисторами, чтобы токи были мА 10 хотябы - для промышленности. Выходы дискретные напрямую к пинам клеммной колодки, т.к. они будут разомкнутыми при их неиспользовании. Если кто делал подобные конфигурируемые входы/выход - подскажите пожалуйста на что обратить внимание, какие подводные камни. Интересуют моменты также с программной конфигурацией, т.е. сколько примерно понадобится обязки(мультиплексоры/ключи), чтобы программно это делать, например тот же резистор токовый вкл/выкл. Спасибо!

-

Библиотека для блок схем.

Politeh ответил Politeh тема в Altium Designer, DXP, Protel

Спасибо! Действительно библиотеки неплохие, не знал что там такие библиотеки, а так пользовался иногда этим приложением, сейчас наверное на него перейду в основном. Спасибо! -

Библиотека для блок схем.

Politeh опубликовал тема в Altium Designer, DXP, Protel

Добрый день! Часто приходится делать блок-схемы устройств. Для удобства построения блок-схем удобно пользоваться символами которыми чаще пользуются в автоматике: т.е. сухой контакт реле, усилитель в виде треугольника, обозначение фильтра, примерно такие как в прикрепленном файле. Может кто находил такие библиотеки для Алтиума на просторах интернета, или готов поделиться? Благодарю. BN-DS-E2_02.pdf -

Profibus Master DP PCB модуль UART/SPI

Politeh опубликовал тема в Форумы по интерфейсам

Добрый день! Стоит задача добавить интерфейс Profibus DP master в промышленное устройство. Есть интерфейсы быстрые SPI/UART. Хост - достаточно шустрая SoC, т.е. SPI и UART тоже быстрые. Система работает на линуксе. Кто-нибудь находил подобные модули Profibus DP master на SPI/UART под линукс? Благодарю -

Нет, задача была перключать именно 5В. Встречные транзисторы не исключены. Хорошо, спасибо за совет! В будущем учтём!

-

Вы можете показать схемы изолированных выходов ваших ИП? Спасибо.

-

Я видимо вас не так понял. Т.е. вы напрямую соединяете их выходы? Интересный вариант.

-

Это если напряжение выше, чем 5В. Для 5В всё-таки с диодными вырпямителями не получится ни как

-

Спасибо большое за развернутый ответ! Сейчас нашли всё-таки интегрированное решение вроде https://www.ti.com/lit/ds/symlink/lm7310.pdf?ts=1630846581732&ref_url=https%3A%2F%2Fwww.ti.com%2Fproduct%2FLM7310 Там есть "настоящая" блокировка реверсного тока. Время срабатывания тоже вроде неплохое для 5В, но вроде в ваша схема шустрее работает. В любом случае решил в ближайшее время погрузиться в разобрать вашу схему более глубоко. А то каскодные схемы с универа не трогал руками, и тем более всякие компараторы на транзисторах, т.к. всё на ОУ делал. Всё чаще понимаю, что в индустриальных решениях очень помогают схемы на рассыпухе, особенно когда нужны универсальные конфигурируемые входы/выходы и т.д. Ещё раз спасибо!