Ed2000

Свой-

Постов

173 -

Зарегистрирован

-

Посещение

Весь контент Ed2000

-

Altium designer

Ed2000 ответил ГодзиллаРенессанса тема в Altium Designer, DXP, Protel

Хотел посмотреть видеоуроки Altium Designer --> папка /pub/Education_video/Altium designer - Видеоуроки не открывается 😂 -

Подскажите, а где можно ознакомиться с программой?

-

Посмотрите (ежегодные мероприятия): https://electronix.ru/forum/index.php?showt...hl=cad.mephi.ru В программе тренинги. Значит есть материал.

-

А что есть на русском по проектированию в Cadence интегральных схем? И есть ли вообще?

-

Смотря что делать и для каких целей.

-

Казалось бы вопрос актуальный, а тема остановилась в 2011 г. и похоже никто и нигде свои проекты больше не делает. Интересно а в каких передовых технологиях сейчас работают россияне?

-

см .ранее

-

RE to: Кто нам может помочь? Если вопрос актуален -- обратитесь на кафедру Электроники МИФИ см. asic.mephi.ru. Они этим (FPGA to ASIC) занимались.

-

Методы и средства моделирования и автоматизированного синтеза элементов аналого-цифровых интегральных микросхем: Сб. лабораторных работ / Э. В. Аткин, Ю. И. Бочаров, В. А. Бутузов, Ю.А.Волков, А.А. Куксов, Е.З. Маланкин, Д. Л. Осипов, А. Б. Симаков. – М.: НИЯУ МИФИ, 2012. 56 с. Сборник включает четыре работы, посвященные моделированию элементов аналоговых и аналого-цифровых интегральных микросхем, а также ознакомлению с методами синтеза цифровых микросхем с использованием средств автоматизированного проектирования компании Cadence и библиотек КМОП элементов с проектными нормами 45 нм. Сборник лабораторных работ предназначен для студентов, обучающихся по программам подготовки специалистов и магистров по направлению «Электроника и автоматика физических установок». см. Работа 4. Маршрут проектирования цифровых микросхем ..........38

-

А что-нибудь сдвинулось за прошедшие 2 года?

-

Для создания fabless-центра проектирования преимущественно аналоговых микросхем... подскажите пожалуйста минимально обязательный набор контрольно-измерительной техники, которой целесообразно оснастить такой центр. Бюджет для покупки -- 10-15 млн. руб. Спасибо за любую полезную информацию ...

-

Подскажите удалось ли разобраться, а то я тоже решил настроить DP? Может есть где концентрированный документик типа how to?

-

Если ваше предложение в силе дайте мне вход в sonsviri. Постараюсь быть активным юзером...

-

Планируется ли какое-либо следующее мероприятие?

-

Пробовали моделировать скажем простейшую RC-цепочку? Или результат не зависит от сложности схемы?

-

А есть ли организации из РФ, которые имеют официально киты на технологию лучше 40 нм? Не знаете ли что об этом?

-

Обновление экрана в IC615

Ed2000 опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

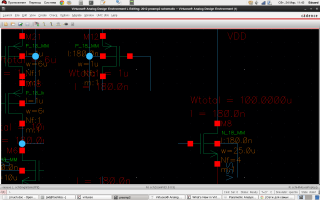

RHEL6+IC615+MMSIM При выделении любого элемента или группы онных в окне Schematics почему-то автоматически не обновляется экран. Каждый раз для прорисовки нужно нажимать "горячую" клавишу "F". Чем это вызвано и как с этим бороться? Кстати, хотел сделать screenshot (снимок экрана через меню Schematics - File- Export Image) и разместить его в теме, однако в результате в самом файле снимка все ОК (нет не прорисованных мест). Удалось сделать screenshot с помощью RHEL (стандартной Gnome-утилитой) -- см. прикрепленный рисунок В середине прямоугольная черная зона -- это то, что было выделено для редактирования. -

К сожалению с некоторой задержкой (фактически только сегодня) увидел эту тему... Внесу небольшую лепту (пару абзацев) в обсуждение на основе имеющегося опыта. Возможно кому-то будет полезно. Во-первых, лет пять назад пришлось решать задачу замены быстрого ПЛИСа от Xilinx (сделанного по КМОП 90нм) на заказной чип по КМОП технологии 0,35 мкм. Результаты исследований на конкретном цифровом проекте показали лучшие параметры заказного варианта. Так, по быстродействию выигрыш был примерно в 1,5 раза. (Следует конечно помнить, что результат будет сильно зависим от типа схемы.) Во-вторых, сегодня современные ПЛИСы могут работать с внешними тактовыми частотами 200-300 МГц (м.б. даже выше), в то время как заказные технологии (уровня 45-180 нм) с внутренней логикой, тактируемой в 1,0-1,5 ГГц (м.б. даже выше). Вместе с тем для последних важно решить вопросы создания (или использования стандартных IP) интерфейсов, которые в основном и будут определять быстродействие. С переходом на нанометровые технологии ограничивающим фактором становятся большие утечки, а для "старых" технологий (например 180-350 нм) потребляемая мощность. Экономика при мелкосерийном производстве (не путать с прототипированием!), как правило, на порядок оказывается лучше у заказных чипов, чем у ПЛИС. (Если конечно забыть, что есть шанс "запороть партию" заказных из-за ошибок при проектировании или процесса изготовления).

-

В любой центр проектирования, можно во внепроизводственный (от англ. fabless), у кого есть выход на соответствующую фабрику (скорее всего зарубежную). Перечень ДЦ можно найти в интернете...

-

Thanks for the reply. Firstly I do not have any problem with IC5141 at RHEL5. But that is not a case for the Neocell. Did you try to use Neocell in RHEL5?

-

В МИФИ нет кафедры с таким названием. См. http://www.mephi.ru/about/chairs/

-

Посмотрите http://www.ic-resources.com/

-

Для сравнения привожу цены Europractice по прототипированию маленьких и больших чипов соответственно: www.europractice-ic.com/docs/MPW2011-miniasic-v5.pdf www.europractice-ic.com/docs/MPW2011-general-v5.pdf

-

Я бы дополнил список по МИФИ кафедрой "Микроэлектроники", кафедрой "Электроники", Ускорительной лабораторией и Исследовательским реактором. А вообще испытаниями на радстойкость занимаются и в Дубне и в Протвино и пр.

-

Мне кажется упомянутые книжки слегка устарели...