-

Постов

2 052 -

Зарегистрирован

-

Посещение

Весь контент Krys

-

Ну об этом я уже хвастался тут Я не о том. А вот о чём. Если открыть доку на DSP48, то там будет параметр, задающий синхронный или асинхронный сброс в DSP48. Чисто теоретически, синтезатор имел возможность понять по Вашему коду, что этот параметр надо при синтезе выставить в асинхронный режим. Другое дело, что он этого асинхронного сброса почему-то не распознал... Это уже недостатки синтезатора. Возможность у него была.

-

там вроде был где-то параметр указания типа сброса: синхронный или нет. Хотя могу путать. Ну и конечно ничто не мешает всё равно на этом месте синтезатору спотыкаться. Просто не умеет корректно обрабатывать, возможно. Так что Вы может быть очень даже правы ))

-

Одной из причин может быть то, что подаваемая частота 50Гц не строго синхронна частоте выборок АЦП, поэтому возникает размытие спектра. Попробуйте тест вашего БПФ не на реальных данных с АЦП, а на заранее подготовленном в Matlab буфере данных, где частота сигнала строго синхронна получится. Можно даже в симуляторе прогнать наверное.

-

"Все точки над фиксированной.точкой"

Krys ответил Artunique тема в Алгоритмы ЦОС (DSP)

навскидку: положительное значение fractional bitwidth говорит о том, что десятичный разделитель (точка, отделяющая целую и дробную часть) находится левее на столько-то битов по сравнению с положением этой точки ровно после самого младшего бита разрядной сетки данной переменной. А отрицательное значение - соответственно, что десятичный разделитель находится правее. Это однозначно означает, что разрядная сетка вашей переменной содержит только целую часть, и то не всю, а начиная с какого-то разряда (указанного в отрицательном значении fractional). Вот пример: разряды вообще : 9 8 7 6 5 4 3 2 1 0.-1 -2 -3 разрядная сетка : 4 3 2 1 0 конкретной переменной В данном примере у конкретной переменной bitwidth = 5, а fractional bitwidth = -4. Это говорит о том, что нулевой разряд вашей переменной он на самом деле не нулевой, а 4. -

Выбор разрядности на выходе фильтров

Krys ответил Artunique тема в Алгоритмы ЦОС (DSP)

Выигрыш ещё и в том, что на последующих этапах децимации тактовая частота поступления отсчётов снижается, и фильтры могут работать в т.н. "полифазном" режиме, т.е. когда на одном и том же умножителе обсчитывается сразу несколько коэффициентов последовательно, а на умножитель подаётся повышенная тактовая частота. -

Короче завёл полностью тот же текст под функцию - проблема исчезла. Так что такой вот workarround этого бага. Если кому-то допустимо менять таск на функцию.

-

а, ну тогда в любом брандмауэре отрубить ему вообще под ноль доступ к инету. Или есть проги (для андроида это называется adaway), которые все рекламные адреса добавляют в файл hosts, после чего эти адреса не грузятся ))

-

А вообще в Вашей конструкции DSP48 хоть в каком-то виде вставляется, но без PREG? Или он вообще ни в каком виде не вставляется, а суммирование делается на рассыпухе? Возможно, его смущает "after td". А возможно, ena. Попробуйте для начала убрать оба. Возможно, тип сигнала data должен быть signed, а прибавляемая величина - ту же разрядность (т.е. надо единичку расширить), хотя последнее - вряд ли должно влиять.

-

Да, Вы говорите очень логично. Но как быть с этим: ?

-

Спасибо за версию. Насколько я понял, всё, что не указано в шапке task, не является подставляемыми параметрами и берётся из переменных, объявленных вне task (как глобальные). Таким образом, rst в таск заходить должен, как и куча других сигналов, которые я в шапке таска не объявил (куча других сигналов у меня используется в "боевой версии", а когда я сюда выкладывал пример - упростил его до предела, чтобы выявить суть). То, что rst заходит в таск, косвенно подтверждает и то, что всё работает, как надо, если поменять условие в нижней ветви на определённое, скажем, 1'b0. Использую pure verilog.

-

Своровать )

-

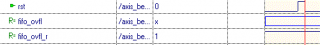

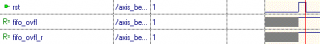

Здравствуйте. Хочу поделиться багой Aldec Active HDL: неверно симулирует условия с неопределёнными состояниями (x) в task. Ну или у меня лыжи не едут ))) Условия задачи: Код с таском: task ovfl_proc; output res; input inp; if(rst) begin res <= 1'b1; end else begin if(1'bx) begin res <= 1'b0; end else begin res <= inp; end end endtask always @(*) begin ovfl_proc(fifo_ovfl, fifo_ovfl_r); // output value, old value end и без таска: always @(*) begin if(rst) begin fifo_ovfl <= 1'b1; end else begin if(1'bx) begin fifo_ovfl <= 1'b0; end else begin fifo_ovfl <= fifo_ovfl_r; end end end В момент действия сигнала rst код с таском даёт неопределённое состояние: А код без таска даёт единицу, как и должно быть (или у меня лыжи не едут?). Как я понимаю, согласно коду, в момент действия rst работает верхняя ветвь условия, поэтому должно быть пофигу, какие условия (определённые или нет) находятся в нижней ветви. Если неопределённое состояние в условии заменить на любое определённое, то отрабатывает корректно в обоих случаях.

-

У меня была собственная корка, у неё был AXI-Lite интерфейс к процу. Среда SDK могла читать содержимое регистров по заданным мной адресам памяти, так что я наблюдал актуальное состояние регистров корки. Только помню, что вычитывалось не просто постоянно, а по какому-то событию, не помню по какому. Вот подзабыл уже. Толи при паузе программы, то ли при обновлении экрана... ))) Чипскоп частенько не любит одновременно работать во время отладки в SDK... Как лечится - не знаю, у нас коллеги на это ругаются, а у меня ни разу такого не вылазило.

-

А намного ли это быстрее, чем ручками с применением автоматизации блочного выделения в Notepad++? Пользуюсь последним, копировать цепи согласно указанным Вами проблемам вообще не напрягало...

-

Интересно, китайские V2 можно применять в нашей военной отрасли? Или только отечественные ПЛИС...

-

Вот именно! Xilinx позволяет подцеплять несколько ucf-файлов.

-

-

Не работает фильтр

Krys ответил Artunique тема в Языки проектирования на ПЛИС (FPGA)

А откуда же у Вас такое мнение, если у самого не получалось? У коллег получалось? -

И вообще, не на языке описания. А только макрокомпонентом. Подробности тут

-

Task Вы хотели сказать?

-

Как реализовать на Verilog'e

Krys ответил sidy тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте. Подскажите, пожалуйста: синтезатор Xilinx даёт ошибку: Функция такая: function clog2ge1; input x; clog2ge1 = ($clog2(x) < 1) ? 1 : $clog2(x); endfunction Какими рациональными причинами можно объяснить такое ограничение? И как его обойти? -

Aldec AtiveHDL

Krys ответил suprun тема в Среды разработки - обсуждаем САПРы

Поковырялся тут маленько. Похоже показывает состояние памяти на момент окончания симуляции (точнее симуляция на паузе). Исходный вопрос остаётся в силе: Как заставить показывать содержимое памяти в Memory View в определённый момент времени, определяемый положением курсора? (или надо как-то по-другому указывать момент времени показа содержимого для Memory View?) -

ну понятно, что оно везде "рекомендация", т.к. если я атрибутом попрошу разместить какой-то элемент там, где он размещён быть не может чисто физически (например опишу массив памяти под атрибутом USE_DSP48), то такая "рекомендация" будет проигнорирована. А в моём случае всё реально.

-

Aldec AtiveHDL

Krys ответил suprun тема в Среды разработки - обсуждаем САПРы

Сделаем из старой темы по типу "вопрос-ответ". Мой вопрос: вывел содержимое памяти на Memory View. Двигаю курсор по осциллограмме, где сигналы заполнения памяти.Ожидаю, что циферки содержимого в Memory View будут меняться (так работает по крайней мере Cadence). Но не меняются, хоть куда курсор в осциллограмме ставлю, хоть в самое начало (где содержимое 100% другое, не определено). ЧЯДНТ? )) Как заставить показывать содержимое памяти в Memory View в определённый момент времени, определяемый положением курсора? (или надо как-то по-другому указывать момент времени показа содержимого для Memory View?)