Varenik711

Участник-

Постов

17 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Varenik711

-

Звание

Участник

Посетители профиля

305 просмотров профиля

-

Запуск симуляции в Vivado через консоль

Varenik711 опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте! Подскажите пожалуйста, возможно ли реализовать запуск симуляции в Vivado ( не имеет значения версия) через консоль? Именно симуляции в интернете я нашел, что функция запуска симуляции через tcl launch_simulation. Собственно, можно ли реализовать запуск этой команды через cmd? Спасибо! -

Да!

-

Подскажите пожалуйста, корректно это как?

-

Altera USB-BLASTER

Varenik711 опубликовал тема в Работаем с ПЛИС, области применения, выбор

После каждой перезагрузки компьютер выводит : Чинится это перезагрузкой в расширенном режиме и выбором Disable Driver Signature enforcement . Но хотелось бы чтобы каждый раз когда включаешь USB Blaster не приходилось проделывать эту операцию. Знает кто-нибудь как это сделать? -

Vivado

Varenik711 опубликовал тема в Среды разработки - обсуждаем САПРы

Подскажите пожалуйста в чем разница между Vivado ML Standart и Vivado Lab Edition? Где они применяются? Заранее спасибо -

А можете пояснить про 0 width replication? Как я понимаю значение в этом случае обнуляется?

-

Здравствуйте, подскажите пожалуйста можно ли задать переменную при параметре parameter X =1; Как reg A = X'b1;

-

Verilog counter

Varenik711 ответил Varenik711 тема в Языки проектирования на ПЛИС (FPGA)

Да мне уже объяснили, спасибо! -

Verilog counter

Varenik711 ответил Varenik711 тема в Языки проектирования на ПЛИС (FPGA)

Как? -

:0 Звучит круто!

-

Verilog counter

Varenik711 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, помогите пожалуйста, столкнулся с такой проблемой в QuestaSim 2020.1 . Не работает счётчик (counter) . Можете подсказать почему так ? (Раньше он работал(вроде)) module LED_TB; reg clk40MHz ; wire LED ; LED LED_inst ( .clk40MHz ( clk40MHz ), .LED ( LED ) ); initial begin clk40MHz = 1'b0; forever #5 clk40MHz = ~clk40MHz; end endmodule module LED #( parameter MAX_COUNTER = 4, parameter LED_SHINE = 15) ( input clk40MHz, output LED ); reg [MAX_COUNTER-1:0] counter; assign LED = counter[MAX_COUNTER-1:0]; // Output LED signal counter[MAX_COUNTER-1] always @(posedge clk40MHz) begin counter <= counter + 1'b1; if (counter > LED_SHINE) begin // Period 15 seconds counter <= 4'b0; end end endmodule -

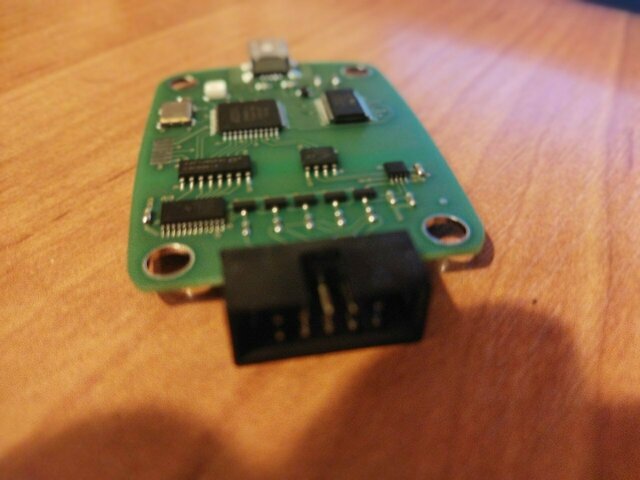

Мне для учебы :) Хотел поиграться с выводом на семисегментный индикатор и кнопочками. Конечно можно попробовать отпаять с него их, но не уверен что получится.

-

Xilinx XC4003E

Varenik711 опубликовал тема в Работаем с ПЛИС, области применения, выбор

-

Cпасибо большое!

.thumb.jpg.1a5818662dabf5e816c0ca09b60068f5.jpg)

.thumb.jpg.82004d0118b0f866f6eb9593d00b6538.jpg)