Zalman_

Участник-

Постов

51 -

Зарегистрирован

-

Посещение

Весь контент Zalman_

-

atan2 на Verilog

Zalman_ ответил Zalman_ тема в Языки проектирования на ПЛИС (FPGA)

Спасибо -

atan2 на Verilog

Zalman_ ответил Zalman_ тема в Языки проектирования на ПЛИС (FPGA)

Да, очень) -

atan2 на Verilog

Zalman_ ответил Zalman_ тема в Языки проектирования на ПЛИС (FPGA)

Видел эту статью Насколько понял из статьи она генерирует синус и косинус, то есть это классический CORDIC в качестве DDS синтезатора, а вот функцию atan2 не вычисляет -

atan2 на Verilog

Zalman_ ответил Zalman_ тема в Языки проектирования на ПЛИС (FPGA)

Спасибо за рекомендацию, попробую еще какие-нибудь варианты теста корки Сегодня весь день этим занимался Результат был следующим В тестбенче корки уже генерируются рандомные значения, что упрощает работу с ним и вот расскажу как это было Примем, что на вход подаются два значение x = 0.11, а у = -0.38, тогда atan2 = -1.29 (все в радианах) В случае Verilog и SystemVerilog есть функция $atan2, которая позволяет посчитать значения и она выдает такой же результат, то есть -1.29 Ядро же выдает значения фазы, которые довольно сильно (на мой взгляд отстают от эталонного), вместо -1.29 выдает результат в районе -1.77 и т.д., то есть значения пляшут +- 0.5 Не знаю, возможно это нормально, но мне кажется, это большой погрешностью, но может быть ошибаюсь Буду дальше копаться с ним, однако, все равно вопрос остался открытым -

atan2 на Verilog

Zalman_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый вечер! Есть задача в реализации atan2 в ПЛИС Ранние темы на форуме видел (пробовал варианты кода, которые были прикреплены) Также пробовал варианты с OpenCores Они работают, но неизвестно правильно или нет (некоторым вариантам реализации уже больше 5 лет, а с автором нет возможности связаться, так как он не заходил больше 2 лет) В связи с этим вопрос Есть ли какие-то реализации atan2 на Verilog на примете, которые можете кинуть и с автором которого можно проконсулироваться по работе корки? -

Спасибо, изучу более детально

-

Про SRRC понял, спасибо Да, я заметил, что во всех моделях есть тот самый переход на 2 и 1 sps, однако не понимал, что и где копать То есть по факту тактирование детектора Гарднера и тактирование интерполятора должно быть в одном clock domain, то есть в 2sps. Понятно, что на выходе интерполятора будет 2sps, а вот откуда и зачем нам нужен 1sps? Хорошо, спасибо, буду искать

-

Добрый вечер! Копаюсь с Вашей моделью Мне непонятны следующие моменты (я новичок в этой тематике и многих вещей еще не знаю) 1) У Вас модулятор создает 8PSK, затем в канале перед АБГШ стоит downsample (в нем значение 2) и по факту из 8PSK делаете QPSK. Зачем так делать и что это дает? 2) В модуляторе SRRC имеет значение wc = 1/4, а в приемнике стоит wc = 1/2. Понятно, что тот самый блок downsample снизил значение sps в 2 раза и теперь вместо 4 sps у вас 2sps, но зачем так было сделано? Знаю, что SRRC на передающей и приемной стороне должны быть идентичны, но у Вас они различны. Можете объяснить ? 3) Рассматривая систему STS есть - Interpolator, TED, Loop Filter, Interpolation Control. Мне непонятно вот что, что конкретно нужно крутить и менять, чтобы адаптировать систему под свою задачу, то есть если я в лоб выставлю значения 4sps (на обеих SRRC) и уберу блок downsample (чтобы значение sps было неизменным в канале), а также в NCO поменяю значение константы у блока Math Function (операция mod) на 4, то ничего не работает, хотя больше в модели ничего не меняю. Сразу отвечу на вопрос по поводу Loop Filter, в нем я тоже пытался крутить параметры, а результат все равно был отрицательным. Под отрицательным результатом я понимаю следующее. В процессе работы Вашей модели я вижу 4 точки для QPSK, но через время происходит рассинхронизация и эти точки превращаются в мешанину, после чего проходит какой-то интервал времени и вновь эти 4 точки находятся. Я не знаю, что скрывается за этой проблемой, так как не делая свою модель, а используя Вашу как эталон, получаю отрицательный результат даже казалось бы в настолько правильно сделанной модели. Можете объяснить где я ошибаюсь и что не до конца понимаю в этом всем?

-

Спасибо за советы, буду ковыряться

-

Большое спасибо Буду разбираться

-

Вопрос, а можете сказать как тема называется или же ссылку дать? Буду очень признателен (над неработающей STS сижу уже не первый день)

-

Выскажу небольшое предположение Возможно вся система работает некорректно по причине того, что используемый детектор Гарднера работает на скорости 2 выборки на символ, а SRRC на модуляторе и демодуляторе выдают 10 выборок на символ Может ли быть в этом проблема или нет, как думаете?

-

Прикрепил модель для 20a и для 18b qpsk_electronix.slx qpsk_electronix_18b.slx

-

Хорошо, я делал это все на версии 20a Для какой версии сохранять?

-

Опишу проблему Как понятно из заголовка пытаюсь сделать символьную синхронизацию для QPSK системы Основываясь на информации из книги "Michael Rice - Digital Communications: A Discrete-Time Approach", символьную синхронизацию делал по принципу: 1) Interpolator - Piecewise структура фильтра Фарроу 2) Timing Error Detector - Детектор Гарднера 3) Loop Filter 4) Interpolation Control - структура "Modulo-1 Counter" В чем проблема ? Проблема в том, что система символьной синхронизации одновременно работает и нет, то есть периодически повторяется следующий процесс: 1) Система находит оптимальный момент выборки (максимального раскрытия глазка) 2) Система теряет оптимальный момент выборки На осциллограмме input и output фильтра Фарроу наблюдается картина как на скриншоте ниже

-

Отклик SRRC в QPSK демодуляторе

Zalman_ ответил Zalman_ тема в Алгоритмы ЦОС (DSP)

Добавив CIC и FIR после гетеродинирования проблема оставалась (то есть сигнал на входе будет по форме такой же, только с меньшей частотой дискретизации и если поставить компенсирующий, то ВЧ составляющая уйдет) В процессе я понял, что изначально фильтр в модуляторе на нужной мне частоте подавлял эту частоту на 120 дб)) (мой косяк и невнимательность) Исправлю и посмотрю что будет Да, как раз систему ФАПЧ я накидал, однако мне не нравилось то, что выходило из SRRC на демодуляторе, поэтому ее отложил на потом, потому что разобраться с фильтром более важная задача Не разбираюсь, а пытаюсь сделать то, что было описано в теории Не получилось так как должно - написал сюда Вот -

Отклик SRRC в QPSK демодуляторе

Zalman_ опубликовал тема в Алгоритмы ЦОС (DSP)

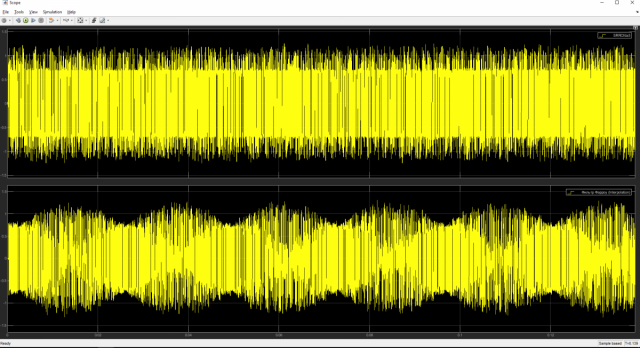

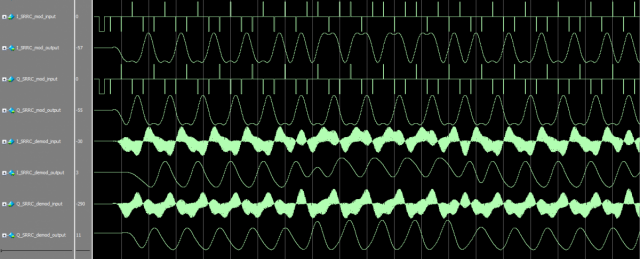

Добрый день, столкнулся с такой проблемой. Делаю демодулятор QPSK на FPGA Есть QPSK модулятор и соответственно QPSK демодулятор. В модуляторе используется SRRC, что автоматически добавляет такой же SRRC на сторону приемника. В процессе модуляции все происходит корректно и передается на приемник. Замечу, что так как проект сделан на ПЛИС (на данный момент только в коде, то как таковой задержки в чем-либо между модулятором и демодулятором нет). Также отмечу, что SRRC, NCO и частоты идентичны друг другу. По идее, на приемной стороне с выхода SRRC на синфазной и на квадратурной составляющей я должен видеть примерно ту же "картину", что и на выходе SRRC, который стоит в модуляторе. Однако при идентичности параметров и фильтров на приемной стороне SRRC выдает специфичный сигнал, который вроде бы и похож, но тем не менее не соответствует сигналу, получаемому из SRRC в модуляторе. Скрин приложил Скрин из программы ModelSim На скрине входы и выходы SRRC на I и Q в модуляторе и демодуляторе. -

Да, написал на входе FIR 12'heff Благодарю за помощь и совет И назрел вопрос Имеет ли смысл так сильно гнаться за ядрами фильтров, если можно сделать фильтр в том же MATLAB?

-

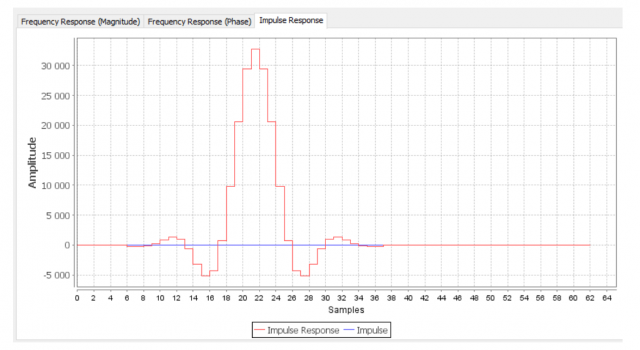

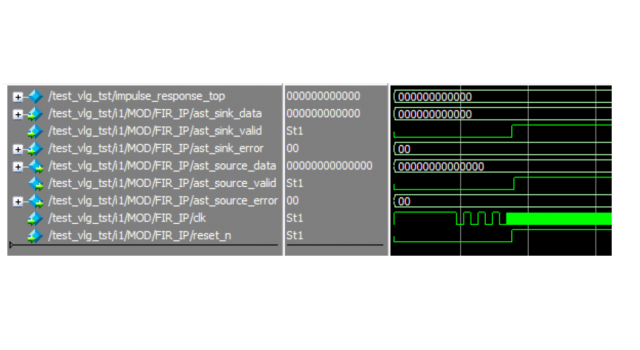

Да, вы по всей видимости были правы с моей ошибкой в "битности" выходной шины Вот так выглядит ИХ при полной разрядности в 33 бита Тогда напрашивается соответствующий вопрос Где можно найти информацию о том, как не допускать таких ошибок в дальнейшем? Точнее как правильно обрезать ненужные биты. 33 бита это хорошо, однако много на мой взгляд

-

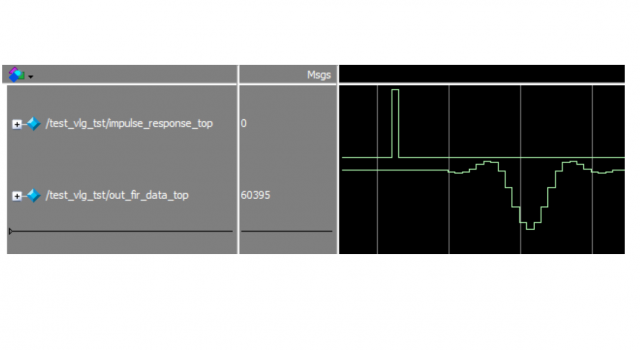

Попробовал данный вариант. Вот ИХ, которую отображается в ядре FIR II При моделировании в ModelSim получил следующее Видно, что вершина ИХ "инвертируется" Вот с другого "ракурса" в MATLAB К вопросу о "Но если у вас на выходе ломовые шумы без сигнала на входе - то фильтр у вас уже не работает." Как видно из ModelSim при отсутствии сигнала на входе, выходной сигнал равен 0

-

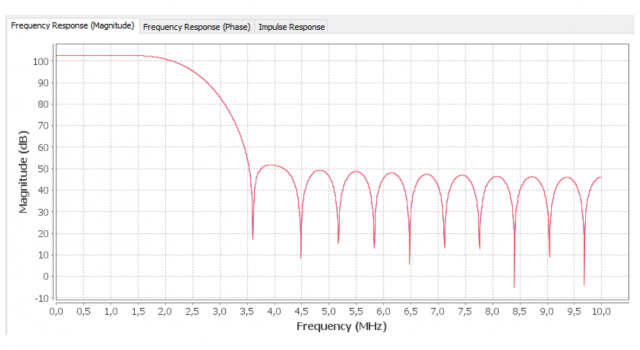

И да и нет При загрузке коэффициентов построение АЧХ, ФЧХ и ИХ действительно происходит, однако с АЧХ есть некоторый "фокус". При проектировании фильтра в MATLAB я указываю, что "FIR filter cutoff frequency in Hz (4e6 as default): 1.2e6", однако, рассматривая АЧХ фильтра в IP ядре частота среза увеличивается в 2 раза. Вашу идею с связкой NCO-FIR сейчас тестирую (пока что результат отрицательный и на выходе нет явного пика на частоте в 1 МГц, хотя судя по АЧХ она там явно должна быть). Спасибо за идею, попробую. По результатам напишу

-

Данная связка: 1) компилируется в Quartus без проблем 2) ModelSim моделирует без проблем 3) при анализе спектра в MATLAB (ModelSim записывает в .txt файл выходные значения сигналов с выхода NCO, CIC, FIR) FIR фильтр работает не так, как должен В железо не заливал даже Это скорее "тестовый стенд" для того, чтобы попытаться понять почему у меня не работает FIR фильтр и как сделать так, чтобы он работал Этот стенд никогда не попадет в железку)

-

Согласно документации на FIR II сигнал reset_n имеет активный ноль. То есть у меня FIR (как и CIC) находятся в состоянии сброса до тех пор, пока NCO не начнет генерировать сигнал. Насколько я понимаю, так фильтр и должен работать. Причем отмечу то, что при полной разрядности в 33 бита фильтр проявляет себя лучше (то есть спектр становится лучше). НО 33 бита это слишком большая разрядность. Отвечу сразу на вопрос. Да, я делал разные варианты "битности". То есть из предлагаемых мне 33 бит, выбирал отдельные куски (как в сторону LSB, так и в сторону MSB). То, что я написал в самом начале (LSB = 9 MSB = 10 ) оказалось субъективно наиболее оптимальным вариантом.