OslikIA

Участник-

Постов

17 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о OslikIA

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

А мне непонятно... В Gerber-ах увидели что-то (что) или прошли импорт в Cam350, и получили то же, что и у меня? Я благодарен, что Вы тратите время, но мне-то нужно разобраться, а не узнать, что Вы разобрались...

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Нашел бяку. Оказывается, есть 2 Symbol.smb - один в корне инсталляции, другой - в каталоге \Symbols\. Тот, что в \Simbols\, судя по дате, был модифицирован уже у меня, после инсталляции, и в нем и лежит эта куча Custom апертур (но я его руками не трогал, видимо, как-то спровоцировал Cam350 на такое действие). Снес все Custom апертуры. Больше не ругается (пока, только открывал\закрывал уже настроенные файлы с паннелями, полный процесс импорта с нуля не проводил еще).

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Выкладываю. А у Вас так и не воспроизводится Warning? Не знаю, профэссоры из диссернета тоже так говорят. А совпадение текста идеальное... CPI3_PM1_PSU1_v3.zip Но я же сохранял свежий cam-файл, и notepadom просматривал - нету там мусора... А не выложите свой Symbols.smb?

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Нашел множественные совпадения (прямо как в Диссернете) мусора в выложенном файле с файлом Symbols.smb из каталога, где инсталлирован Cam. Похоже, он оттуда их тащит, да еще и несколько раз пытается это делать, и на свои же действия ругается. Т.е. минимальное решение найдено - игнорировать сей warning, а если надоедает - снести мусор notepadom. Максимальное решение было бы понять, как этого избежать... В принципе, это кейс для команды поддержки Cam, но мне {почему-то:)} стыыдно обращаться.

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Покопался в импортируемых Gerber-ах, ничего похожего на на Custom Aperure не нашел. Если я правильно понимаю, в Gerber это строки вида: G04* G04 D10 : "Ellipse X0.050mm Y0.050mm H0.000mm 0.0deg (0.000mm,0.000mm) Draw"* G04 Disc: OuterDia=0.0500* И еще вопрос - в одном из проектов - не в том, что выложен - есть PAD особой формы с полигонами. Я его в тексте Gerber не смог найти. Может, знаете волшебное слово - где его поискать... Или он в Gerber уже расструктурирован - не является апертурой?

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

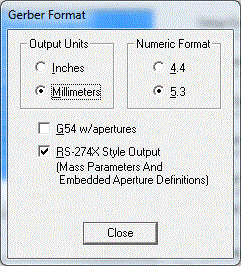

При открытии Cam, Tables\Apertures пустой, но, как показывают предыдущие опыты, это ни о чем надежно не говорит. При открытии файла Cam же тоже про Custom Apertures молчит, хотя в тексте глючного файла они есть. А "ерунда" действительно повторяется - готовлю три разных массива, и везде... Раскопки PCAD и Gerber еще не успел провести... Кстати, сделал сохранение пустого файла Cam и просмотрел его в notepad - никакого похожего мусора не обнаружил.

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

И проделал еще один опыт: Открываю файл, захожу в Tables/Apertures, имею 75 апертур. Нажимаю [Go To Custom], показывает сообщение "No Custom in aperture table". Перехожу в Panel Data (показывает помянутый Warning), в таблице апертур уже 285 штук, [Go To Custom] показывает длиннючий список. Делаю [Compress], количество сокращается до исходного, [Go To Custom] снова показывает, что Кастомов нет. Дальнейшие переходы CamEditor <==> PanelEditor умножение апертур не производят. После выхода из программы с новым входом история повторяется. Смущает то, что при открытии файла, не трогая PanelEditor, Custom в списке апертур не появляется. Партизанское редактирование, действительно, помогло. Все Custom в тексте были, удалил. Интересны два вопроса: 1 - Почему на них не действует Compress? 2 - Где я их мог подцепить и как этого избежать? Теперь полезу смотреть так же по партизански PCAD и его экспортированные Gerber - там ли определены эти Апертуры. (перед экспортом в PCAD делал PadStyles/PurgeUnused...)

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Весьма странно, что не повторилось. У меня та же версия 10.0.1 (build 309). Может, у Вас "более настоящая"... Сообщение выскакивает при переходе с CamEditor на PanelEditor (нажатие кнопки Panel Data внизу паннели Navigation Pane). С партизанским редактированием cam-файла побалуюсь, отпишу. Спасибо.

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Здравствуйте, Mef. Спасибо за участие. Файл прилагаю. А панель-едитор меня прельстил быстротой обновления группы при изменении исходника - все-таки меньше рукодействия, чем при копировании... cpi3_pm1_psu1_v3.zip

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

Здравствуйте. Делаю мультиплицирование (массив одинаковых плат) в CAM350 V10.0. Исходник - экспорт из PCAD 2004 (gerber+ncDrill). После импорта одиночной платы никаких проблем, результат удовлетворяет. После настройки паннелизации тоже все замечательно, экспортировал gerber+drill панели, импортировал полученные gerber+drill в новый проект cam350, визуально никакой разрухи не замечаю. НО: При повторном открытии проекта с настроенной паннелизацией, при переходе в редактор паннелизации, вылезает Warning: [ Like custom apertures detected: ... ]. Вопрос - это неадекватное сообщение, которое можно игнорировать? Или я незаметно создал какую-то проблему? (я встречал обсуждения такого сообщения при зоздании панели с разными платами, но у меня-то регулярный массив...) Дополнительно, провел такой опыт: открываю файл с паннелизацией, делаю Menu/Tables/Apertures [Compress...], получаю сокращение списка апертур до 95 штук. Сохраняю файл. Выхожу, захожу, открываю файл, имею те же 95. Перехожу в паннелизацию, получаю тот же warning, имею уже 259 апертур. Пробовал сохраняться и с 295, и с 95 апертурами (делая или не делая им [Compress]), warning не исчезает. И каждое открытие редактора паннелизации опять множит апертуры. Это аргумент за то, что warning неадекватен?

- 19 ответов

-

- cam350

- pannelization

-

(и ещё 1 )

C тегом:

-

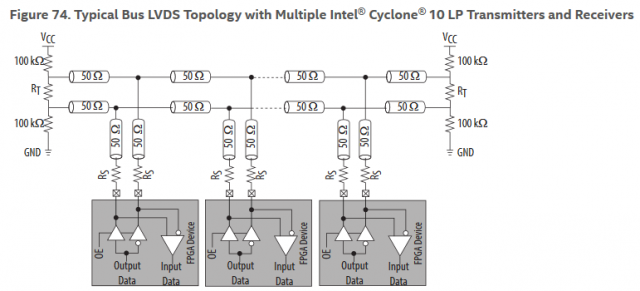

Отвечаю сам себе (чтобы образумиться, надо выступить и опозориться...) Мне же Intel не написал, что значение Rs = 50 Ohm, Intel изобразил отвод линии с импедансом 50 Ohm. Всё, полез менять резисторы.

- 1 ответ

-

- lvds

- cyclone 10 lp

-

(и ещё 1 )

C тегом:

-

busLVDS на cyclone 10 LP

OslikIA опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте, господа и товарищи. Вопрос на границе схемотехники и Quartus. Пытаюсь реализовать LVDS с переключением направления линии прием/передача между двумя Cyclone10LP. Решил сделать это как частный случай bus-LVDS. Схемотехника по рекомендации Intel на рисунке, у меня проще - около каждого Rt стоит приемопередатчик. К каждому из дифф.выводов последовательно 50 Ohm, далее Rt=100 Ohm, и в линию кабеля USB 3.1. Выводы настроены в PinPlanner на стандарт busLVDS, питание банка 2.5 V. При выводе сигнала уровень дифференциального напряжения ~0.6V (если точнее, сверху вниз: Vcc=2.5; pin1=2.1; Rt(up)=1.6; Rt(down)=1.0; pin0=0.3; gnd=0) Собственно, вопросы: 1. Не великоват ли дифф. уровень (вроде д.б. 350mV) 2. Видел ли кто описание от Intel, где было бы понятно - они в busLVDS работают с ноги источником тока или источником напряжения? и параметры. Я что-то не смог найти. 3. Если предположить, что работают источником напряжения (а пока кажется, что так), то надо ли увеличить последовательные резисторы для получения дифф. напряжения 350mV ?. 4. Возможно, я что-то не доделал в настройках или схемотехнике, и поэтому ноги передатчика ведут себя не так, как д.б. ? С уважением, Иван.- 1 ответ

-

- lvds

- cyclone 10 lp

-

(и ещё 1 )

C тегом:

-

До подробностей загрузки еще не дошли мысли - пока идет оценка - мой-ли это кандидат. Предполагается использовать как "интерфейсную морду" для проекта на cyclon 10 LP (Eth1000+USB2.0). Пока исследую возможности посадить cyclone на PSRAM-интерфейс. Транзакции напрямую из процессоров (что M4, что A7) идут меее...дленно (порядка 200-300 ns). Когда запускаю через MDMA, идут быстро, в соответствии с параметрами flexible memory controller, т.е. делаю вывод - ограничение не в FMC. Но, я чувствую, мы погружены в разные темы, может позже пересечения возникнут. Рад общению.