oleg679976

-

Постов

29 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные oleg679976

-

-

11.01.2021 в 17:18, RobFPGA сказал:

Приветствую!

Опять вы себе жизнь усложняете

Где в задании сказано что инициализировать mystr по умолчанию надо рандомными словами?

Где в задании сказано что инициализировать mystr по умолчанию надо рандомными словами?

То есть объявление string mystr = "bla bla bla и еще 18 символов!" как раз укладывается в условие задачи

Если же хочется заполнят рандомными словами тогда да - придется в цикле сначала генерировать эти слова а уж затем склеивать их в строку.

Ну и получив строку через $value$plusargs (или взяв то что задали по умолчанию) придется парсить выделяя слова в пробелах.

По умолчанию массивы инициализируются константами через = `{....}.

Удачи! Rob.

Спасибо за ответ! Правда в задании указано: "Создать массив строковых переменных и заполнить их словами из исходной переменной. ", поэтому и задал вопрос) Что-то нет настроения заморачиваться с парсерами, учитывая сколько всего еще предстоит изучать.

-

Коллеги, может кто-нибудь объяснит про инициализацию массива словами из строковой переменной?

Задание звучит так: "Объявить строковую переменную mystr. По умолчанию переменная должна быть инициализирована строкой содержащей больше 30 символов. Заполнить строку используя функцию $value$plusargs("MYSTR=%s",mystr) Строка может содержать любое количество символов пробела, разделяющие строку на слова, слов более одного. Создать массив строковых переменных и заполнить их словами из исходной переменной. Размер строки может изменяться в ходе проверки задания и передаваться через +MYSTR параметр. В конце и начале строки могут быть доп пробелы. Слова могут быть разделены множеством пробелов.

-

В консоль вывести содержимое строки в формате:

- MYSTR=<строка>

-

В консоль вывести содержимое массива в формате

- MYSTR[1]=<строка>

- MYSTR[2]=<строка>"

- У меня два вопроса: 1) Если необходимо задать использовать слова из строки, то получается нужно каким-то образом организовать сортировку слов и пробелов? Выделить слова из строки, класть в переменные слова, а потом из них рандомом инициализировать?

- 2) Есть какой-нибудь метод инициализации массивов? Посмотрел на вышеупомянутых сайтах, ничего такого не увидел, только через цикл.

- Пока набросал такой код, в нем просто рандомно инициализировал:

-

// Code your testbench here

// or browse Examples

module task4;string mystr;

integer myarray [0:9] = '{1, 1, 1, 1, 1, 1, 1, 1, 1, 1};

initial begin

if ($value$plusargs("STRING=%s", mystr))

$display("GOT STRING");

foreach (myarray) begin

$display("Array element %d: %d", i, myarray);

//fork

#1 myarray = $random % 14539876;

#1 $display("Array element %d: %d", i, myarray);

//join

end

endinitial

$monitor("%t Array %p", $time, myarray);

endmodule

-

В консоль вывести содержимое строки в формате:

-

37 минут назад, RobFPGA сказал:

Приветствую!

Вам же в задании не сказано инвертировать все поля разом? Ну так и инвертируйте поэлементно! Зачем себе жизнь усложнять

var1 = '{36, "453", 234, 434}; initial begin var1.field1 = ~var1.field1; var1.field3 = ~var1.field3; var1.field4 = ~var1.field4; ...

Удачи! Rob.

Спасибо, понял!

-

8 часов назад, andrew_b сказал:

В задании же написано:

Надо сделать логическую инверсию тех полей, которые не строковые и не целые.

my_struct var2 = '{36, "453", !234, !434};

Так получается? Я другого способа не вижу, может подскажете чего. -

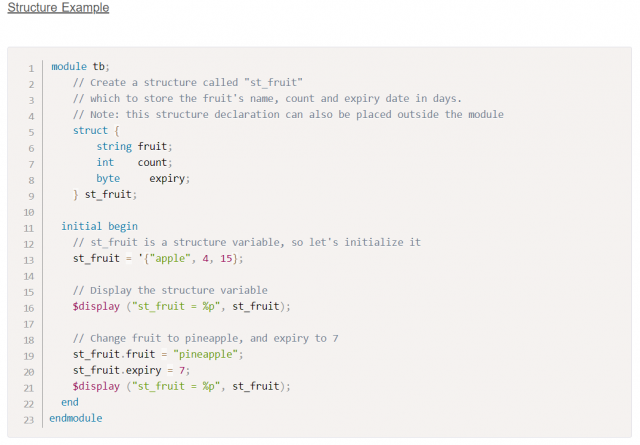

Добрый день, коллеги! Начал изучать SV по материалам с данного сайта http://simhard.com/wiki/index.php/Спец_курс_(Верификация_цифровых_схем)/Практические_задания_(Лекция_1). Для закрепления естественно проделываю практические задачи. Пришел сюда, так как ни google, ни chipverify, ни testbench.in не помогли мне найти ответ.

Сейчас выполняю задание: "Создать тип данных структура, содержащую 4 различных поля. Поля должны иметь тип целочисленный, строковый, бит-вектор. Создать две переменные полученного типа. Проинвертировать все битовые поля в первой переменной. Значение всех полей первой и второй переменных типа структуры вывести в консоль.

Формат вывода:

VAR1 FIELD1: <value>

VAR1 FIELD2: <value>

...

VAR2 FIELD1: <value>

VAR2 FIELD1: <value>

..."

Не могу никак понять как проинвертировать структуру? Исходя их формулировки задания есть ощущения, что это должно делать в одно действие, но простое инвертирование, как в Verilog дает ошибку, с другой стороны смущает, что типы данных в структуре абсолютно разные и инвертировать string, как-то странно.

Код симулирую на EDAPLAYGROUND в Aldec Riviera Pro 2020.04:

// Code your testbench here

// or browse Examples

module task_2;

typedef struct {integer field1;

string field2;

bit [10:0] field3;

logic [10:0] field4;} my_struct;

/*my_struct var1, var2;

var1 = '{36, "453", 234, 434};

var2 = var1;*/

my_struct var1 = '{36, "453", 234, 434};

//my_struct var2 = ~var1;

//my_struct var2 = !var1;

my_struct var2 = var1;

initial begin

$display("var1 field1: %p", var1.field1);

$display("var1 field2: %p", var1.field2);

$display("var1 field3: %p", var1.field3);

$display("var1 field4: %p", var1.field4);

$display("var2 field1: %p", var2.field1);

$display("var2 field2: %p", var2.field2);

$display("var2 field3: %p", var2.field3);

$display("var2 field4: %p", var2.field4);

end

endmoduleТакже вопрос по декларации и инициализации структуры. Данный код выдает ошибку:

/*my_struct var1, var2;

var1 = '{36, "453", 234, 434};

var2 = var1;*/Так нельзя задавать? Просто на сайте chipverify задается так, или дело в операторе initial?

-

Опубликовано · Изменено пользователем oleg679976 · Пожаловаться

1 час назад, yurik82 сказал:вы должны продлить свою волноводную линию хотя бы на 1/2 лямбды от антенны и вонзить её в Rad слой

Мне казалось, что Radiation мы должны ставить далеко, подразумевая, что мы смотрим ДН на этих плоскостях, а ДН мы смотрим в дальней зоне, разве не так? Уточняющий вопрос: PML_radiation (прямо название из шфсс) и Radiation, которое фигурирует в обсуждении - это одно и то же или нет? Просто есть PML_radiation в ветке Boundaries, а есть, как я понимаю, сфера из ветки Radiation в дереве проекта.

Руководствуясь действиями разработчика в серии видео ANSYS HFSS: Designing a Dipole Antenna с youtube-канала Ansys How To Videos, я сделал Box вокруг структуры, достаточно далеко от всех элементов антенны, выделил все грани и настроил PML Setup Wizard, это правильно?

-

Спасибо за ответ, стало намного яснее, но не до конца)

Дело в том, что я смоделировал структуру с узлом питания, осуществив ввод мощности сосредоточенным портом, расчёт прошёл успешно. Проблема в том, что мне хочется исследовать импеданс антенной структуры, которую я считаю, то есть без питающего узла. Я рассчитывал, что можно это рассчитать каким-то образом.

Из вашего сообщения я понял, что для такого случая подходят только волновые порты. Правильно ли я понял, что антенны в модели должны быть далеко от Radiation Box, а вот эти полоски можно вогнать прямо на грани и там ставить волновой порт? Еще вопрос, получается мне с помощью Reference Line необходимо задать моду, которая будет идти в порт? Или мода выбирается сама? Я новичок, help читаю, но прогресс медленный(

Подскажите пожалуйста как метод расчёта для антенн лучше: modal или terminal?

6 минут назад, Александр Мылов сказал:Можно сделать проще,

В установке Wave порта в параметре Deembed указать расстояние.

HFSS посчитает.

Спасибо за ответ, это делает решение проблемы более удобным, буду знать)

-

Три полоска это начало антенн, в университете дали задание запитать и прогнать расчёт так, чтобы в одном случае по бокам была земля, внутри фаза, в другом случае внутри земля, по бокам фаза. Нужно обсчитать сделанный макет просто, а питание макета осуществляется цанговым зажимом, получается нужно использовать сосредоточенный порт из того, исходя из того, что Вы написали.

-

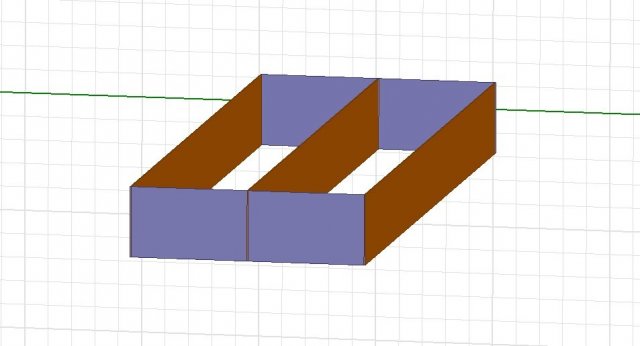

Добрый день! Необходима помощь более квалифицированный специалистов. Хочу запитать следующую структуру и проанализировать для двух случаем: по бокам фаза, внутри земля, и по бокам земля, внутри фаза. Это часть другой структуры, подвод питания к антеннам. У меня проблема с установкой портов, шфсс выдает ошибки. Для lumped port только одна грань должна питаться фазой, reference conductor задается без проблем. При установке wave port выдает ошибку, что его можно только снаружи ставить (на vacuum, как я понимаю), но в моем случае для антенны я делаю radiation плоскость много больше антенны и не могу поставить wave port нормально). Как лучше такую структуру рассчитывать? Какой способ решения лучше выбирать и какие порты ставить.

Какие советы есть по расчёту антенн в шфсс, я новичок, буду благодарен, это ускорит мое продвижение. Заранее спасибо.

-

1 минуту назад, Lmx2315 сказал:

always @(posedge clk) frnt<={frnt[1:0],in}; <-каждый такт тактовой частоты записываем в сдвиговый регистр состояние входа

if (frnt[2:0]==3'b011) sch<=sch+1; <-проверяем условие фронта, ищем совпадение с эталоном

Если на входе постоянно ноль то сдвиговый регистр заполнится нулями будет : 3'b000

если на входе появляется еденица то сдвиговый регистр станет выглядеть так:3'b001

на следующий такт : 3'b011

на следующий такт : 3'b111

если пропадёт еденица со входа то: 3'b110

на следующий такт : 3'b100

на следующий такт : 3'b000

Спасибо за объяснение! Весьма интересное решения, я б до такого не додумался. Плюс сразу понял к чему здесь запас по частоте.

-

15 минут назад, Lmx2315 сказал:

Люди считают импульсы по фронтам и без инверсных клоков (если есть запас по тактовой) на верилоге это вот так:

module frnt_sch (input wire clk,input wire rst,input wire in,output reg [7:0] sch);

reg [2:0] frnt=0;

always @(posedge clk) frnt<={frnt[1:0],in};

always @(posedge clk)

if (rst==1) sch<=0;

else

if (frnt[2:0]==3'b011) sch<=sch+1;//поиск фронта

//if (frnt[2:0]==3'b110) sch<=sch+1;//поиск спада

endmodule

К сожалению, не понял как работает модуль. Был бы очень благодарен, если бы вы объяснили подробнее сюда или в личные сообщения. Или, если бесит мой низкий уровень знаний и понимания верилога, можно не объяснять)

1 минуту назад, gibson1980 сказал:Все верно

Тогда получается импульс выделения фронта или спада будет длительностью в период клока. Поэтому я и считываю спадом. Других способов не смог пока придумать.

-

4 минуты назад, gibson1980 сказал:

Я делаю так:

if sig=1 & t_sig=0 begin ... фронт; end else if sig=0 & t_sig=1 begin ... спад; end t_sig <= sig; // задержка на такт

Это получается чисто выделитель фронта или спада, правильно?

В силу того, что работаю в схемном редакторе делаю так как здесь с помощью триггера и логики - https://marsohod.org/verilog/157-verilogedges -

1 час назад, Bad0512 сказал:

Не требует, по крайней мере у Xilinx. Проблема с инверсным клоком в другом - в два раза ухудшается времянка при переходах с логики, тактируемой прямым и инверсным клоком соответственно. Ну и дурной тон конечно, это да.

Я даже на своем уровне знаний про ПЛИС и цифровую схемотехнику в целом, в принципе понимаю, что синхронный автомат должен изменять свои состояния по фронту, так что использовать инверсные клок не лучшая идея. У меня в проекте инверсный клок нужен для того, чтобы считать импульсы выделения фронта или спада сигналов. Насколько я понимаю их по-другому не считать.

21 час назад, iosifk сказал:Похоже на то, что сам принцип проектирования у Вас неправильный. Потому как инверсный клок требует соответственно своего дерева распространения сигналов в ПЛИС. А это довольно дорогой ресурс...

Если хотите, то могу рассказать это подробнее....

Попробуйте сделать автомат, который будет "в середине" проекта. Тогда все проектирование станет гораздо проще. И, как правильно замечено выше, можно заменять не весь проект, а по-частям...

К сожалению, я не силён в устройстве ПЛИС, видел пару картинок устройства элементарных ячеек, но пока глубоко не разбирался в этих вещах. Поэтому не думаю, что мне это поможет. Каюсь, и осознаю, что такие вещи необходимо знать.

-

21 час назад, Lmx2315 сказал:

а вы не замещайте всё - я вам написал два готовый тригера, сделайте из них графические блочки и ставьте себе в схему.

Спасибо!

-

2 часа назад, Lmx2315 сказал:

а вы пишите на verilog-е , там это просто делается posedge или negedge .

module pos_trig ( input wire clk,input wire d, output reg q); always @(posedge clk) q<=d; endmodule module neg_trig ( input wire clk,input wire d, output reg q); always @(negedge clk) q<=d; endmoduleДа, я знаю, что verilog намного удобнее, но я в прошлом вопросе писал, что все горит уже, и тратить доп время на перевод в verilog нет возможности

-

Добрый день! Я новичок и вопрос соответствующий. Изучая файл Timing Analysis of Internally Generated (видать от Altera, чьё авторство не знаю) наткнулся на то, что использовать инвертор для инверсии clk не рекомендуется, и проинвертировать clk можно с самом триггере. А у меня в Quartus эта функция недоступна. В силу того, что работа идёт на ПЛИС Altera Flex10KE у меня стоит Quartus 9.0. Может быть дела в версии Quartus или семейство не поддерживает такую возможность? Или может сначала в где-то надо определить clk?

-

Спасибо за ответы!

-

Полностью согласен, изучая готовые модули понял, что на языке проще реализовать синхронное устройство. Есть большое желание перейти на Verilog, но это дело не одного дня, а уже проект надо сдавать, а к переходу на язык надо еще тестбенчи писать научиться.

-

Всем добрый день! Прошу помощи! Я новичок в ПЛИС и писал прошивку ПЛИС в графическом редакторе. Сделал 3 различных блока прошивки в 3 разных проектах в Quartus. Как их правильно объединить в один, чтобы все нормально работало? Делал выгрузку схемы 2-ух проектов в виде блок-символа и добавлял в библиотеки третьего, но сомневаюсь в правильности такого подхода. Прочитал у умных людей про верхний уровень иерархии и задумался. Плюс при создании мегафункций разных проектов не изменял имена и в итоге теперь выдает ошибки из-за этого. Можно ли как-то исправить это при объединении не изменяя имена мегафункций в каждом проекте?

P.S. Прошу прощения, если с такими простыми вопросами создал ветку не в том разделе форума, хотел податься в "Помощь новичкам", но подумал, что правильнее спросить в разделе САПРы. -

В 31.01.2019 в 11:32, MegaVolt сказал:

process (Clk) begin if (Clk'event and Clk = '1') then Data_Shift <= Data; end if; end process; Rise <= Data and not Data_Shift; Fail <= not Data and Data_Shift; Front <= Data or not Data_Shift; ShiftData <= Data_Shift; Data_plus1 <= Data or Data_Shift; Data_minus1 <= Data and Data_Shift;Генерилка ништяков:

Rise - единичный импульс по переднему фронту 0->1Что делают остальные можно посмотреть в симуляторе :)

Большое спасибо за помощь, очень помогли!

Так же большое спасибо всем проявившим участие! -

Предложенное в той теме решение безусловно мне помогло и я сделал предложенный измеритель, но на асинхронном RS-триггере из-за особенности единичных импульсов. Самостоятельно придумать схему генерации импульсов длительностью в период clk я не смог, поэтому и задал вопрос уже в теме для новичков, вдруг кто-нибудь сталкивался с этим или знает как это сделать. Хочется все-таки сделать на синхронном RS-триггере.

17 минут назад, Herz сказал:Так в той теме Вы указали, что вопрос решился.

-

Безусловно, суть построения мне объяснили, вопрос теперь у меня в другом, а именно в формирователе единичного импульса по фронту метки.

В предыдущей теме единичные импульсы сказали посылать на синхронные входы RS-триггера.Скорее всего, я чего-то не понимаю, поэтому и решил создать эту тему.

Я нашёл в инете схему формирователя на двух триггерах, который по фронту генерит импульс. Этот импульс по длительности равен длительности импульса clk. И я вот не понимаю как мне его по этому самому clk считать, а схему формирователя единичного импульса, который бы генерил единичный импульс длительностью период clk, чтоб его можно было считать нормально в триггере.

Либо я чего-то не понимаю и импульс длительностью импульс clk спокойно можно считать в триггере.

-

Доброго времени суток! Есть потребность в генераторе единичного импульса по приходу разрешающего сигнала! Нашел схему на двух триггерах, она работает, но генериться импульс длительностью импульса clk, а мне бы надо, чтобы генерился единичный импульс длительностью период clk, чтоб его можно было считать нормально. Ибо с генерацией импульса длиной импульс clk считать его нормально по clk не получается, либо я, возможно, чего-то не понимаю.

-

1 минуту назад, MegaVolt сказал:

Как?

Так генерацией единичного импульса по фронту метки. Раньше я триггер возводил самой меткой.

Статья по методам машинного обучения в гибридном формировании луча

в Предлагаю работу

Опубликовано · Пожаловаться

Добрый день. Необходима помощь в написании статьи ВАК на тему применения алгоритмов машинного обучения в гибридном формировании луча. Обязательно нужна экспериментальная часть хоть какая-то, главное чтобы приняли в журнал. По цене договоримся.