-

Постов

484 -

Зарегистрирован

-

Посещение

Весь контент MaratZuev

-

А батника нет, собственноручно написанного, как этот: rmdir /s /q db rmdir /s /q greybox_tmp rmdir /s /q incremental_db rmdir /s /q output_files rmdir /s /q "Output files" rmdir /s /q simulation rmdir /s /q work del /q *.bak del /q *.dbg del /q *.ddb del /q *.done del /q *.pin del /q *.qarlog del /q *.qdf del /q *.qws del /q *.rpt del /q *.summary del /q *.smsg del /q *.sof del /q transcript del /q vsim.dbg del /q wave.do del /q *.wlf Ок, конечно, в до-qsys-овскую эпоху написан, но, вдруг? Хотя, скорее, в *.qsf или как он сейчас называется прописано. Ну не в реестре же? Чудес-то не бывает. Или проект давайте на всеобщее растерзание: вдруг, кто чего и найдёт? Да, ещё дурная мысль: а поиском по всем файлам с вхождением искомого текста не ищется?

-

Всё, нашли. Спасибо. 1408, если не вру.

-

Отечественный ОУ с питанием +- 20В - есть ли такой?

MaratZuev опубликовал тема в Микросхемы

Всем добра! Просьба пнуть в нужном направлении и/или задавать наводящие вопросы. -

Merging Mentor Graphics (Questa)'s ucdbs

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

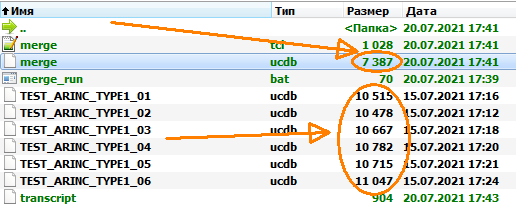

Всем добра! Имею намерение объединить несколько файлов баз данных по покрытию типа ucdb в один посредством команды merge QuestaSim. Выполняю следующий tcl: variable testBenchDir [file normalize [pwd]] variable merge_ucdb ${testBenchDir}/merge.ucdb if {[file exists $merge_ucdb]} { file delete -force $merge_ucdb } variable fileList {} foreach fileName [glob -nocomplain -type f ${testBenchDir}/*{.ucdb}] { lappend fileList ${fileName} } vcover merge -stats=none -strip 1 -totals -silent ${testBenchDir}/merge.ucdb {*}${fileList} И в результате получаю Я что-то делаю не так, или что-то не понимаю, что скорее? Как эти базы, суммируясь, дают ещё меньший размер, чем каждая база по отдельности? Всё сопутствующее прилагаю. Short.zip -

Увы и ах: Опция, как я понял, именуется -autoorder. Но с ней ничуть не полегчало:

-

А, это как мы в группе в телеграмме код вставляем моноширинным шрифтом для отображения оного комильфо? Ну так и приходится делать, чтобы не пойми что не отображалось Всё-равно вносить коррективы в сгенерённый скрипт, как написал товарищ выше, чем и займусь далее..

-

Да, но только там сильно ограниченное подмножество вариантов формата, что даже bat (cmd) отформатировать не нашёл чем Итого, сформирован, например такой батник: Вот в нём ключ -p создаёт пустой каталог с именем -p. Вопрос: накой?!

-

Спасибо, но, похоже, другого пути нет: Исходный скрипт Ментор создаёт два скрипта. Mentor_QuestaSim64_2020.1_Quartus_x64_11.0sp1_208_verilog.tcl и Mentor_QuestaSim64_2020.1_Quartus_x64_11.0sp1_208_vhdl.tcl их, видать, и править.. PS. За подсказку про спойлер отдельное спасибо, а то всю жизнь ползовался кодом (а он зачем, в таком случае?)

-

Еще раз: vcom вызывается quartus_sh с ключём --simlib_comp, а у этого ключа никаких других, кроме как указанных мною выше, вариантов нет.

-

Сам квартус эту квесту вообще не видит: Для кого эта опция есть? Если для quartus_sh, то его help по опции компиляции библиотек Даёт следующее: где я никаких опций не вижу. Не там смотрю?

-

Всем добра! Решил обойти GUI и написать свой же batch, хотя на много % уверен, что делаю тоже самое, что и GUI. Итого при нахождении требуемых инструментов по требуемым путям формирует скрепку (там, впрочем, всё, включая сам батник). Формируются три лога, один из которых формирует сам батник, два других - Questa. Один, формируемый Questa - для библиотек verilog, второй - для VHDL. Первый из них, Mentor_QuestaSim64_2020.1_Quartus_x64_11.0sp1_208_verilog.log, выглядит так: Второй - Mentor_QuestaSim64_2020.1_Quartus_x64_11.0sp1_208_vhdl.log, так: Вопрос: что за ошибки в файлах Mentor_QuestaSim64_2020.1_Quartus_x64_11.0sp1_208_verilog.log и Mentor_QuestaSim64_2020.1_Quartus_x64_11.0sp1_208_vhdl.log? На что ругается Questa? QuestaSim 2020.1 Quartus 11.0 sp1 build 208 Libraries.zip

-

Да там, похоже, и тех библиотек, что нет в составе, подгрузить не удастся: https://www.eremex.ru/products/delta-design/simtera/

-

А я вот так и не смог перенести параллельным переносом проект в скрепке с ModelSim на Active-HDL. Наверное, не сильно упорствовал? RoadMap.zip

-

-

Разве с любыми другими б/у также нарваться нельзя? Меня просто заинтересовало, почему именно израильские? Как понимаю, был единичный опыт, но из этого совсем не следует обобщение? Нет, я никого не защищаю, просто "не могу понять" (с) "В августе 44-го"

-

За наводку спасибо: с Lattice уже связался - в процессе переговоров.

-

По этой плате очень уж стрёмно - один отзыв, да и то пустой (впрочем, я сам этим грешу), а покупок вообще не вижу. Кстати, хромовский плагин выдаёт следующее, но оно, вроде ни о чём: Что касается Ebay и остального online: сильно сомневаюсь, что для такой организации, как наша, это - приемлемый путь. Нам нужен официальный поставщик. Спасибо в любом случае. А вот это прошу прокомментировать особо

-

Спасибо. Кит бы к нему найти, чтобы мороки ещё меня было. Для пятого вот, вроде, что нашёл: Starter Platform for OpenVINO™ Toolkit Может, дадите побаловаться за соразмерное нематериальное спасибо? Спасибо, пошёл курить мануалы и искать пути доставания. Что для меня важно - есть, с чем сравнить (вариантом, подсказанным товарищем выше)

-

Второе

-

FPGA + PCIe ASIC - куда смотреть?

MaratZuev опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем добра. Стоит задача подружить внешний мир ПК с внутренним посредством заданного интерфейса. На заре своей трудовой деятельности стыковал PCI9050 (она же 9052), позднее пересев на 9054 и Altera Flex10k50, позднее переехав на Acex1k100. В любом случае сейчас ни на контроллер шины, ни на производителя ПЛИС жёсткой ориентации нет, и рассматриваются все варианты. Что хотелось бы: сразу купить кит и начать играться. Второй по значимости вариант, конечно - пнуть в направлении контроллера (сейчас PLX, упомянутый выше, купил Broadcom) - есть ли альтернатива? А если у кого (желательно в первопрестольной) есть своя разработка, которой он мог бы (не безвозмездно, конечно) поделиться бы - был бы раз услышать. -

Does ModelSim ME support the code coverage feature? No, code coverage is a licensed option for ModelSim PE/SE. You need to purchase a license to use this feature. Once you have a license, you need to set the code coverage option for compile and then load the design with coverage enabled and then the menus are enabled. The code coverage chapter of the ModelSim User Manual includes all the relevant information. Warning: <SystemVerilog file>: (vlog-2186) SystemVerilog testbench feature (randomization, coverage or assertion) detected in the design. These features are only supported in Questasim. Description This warning may appear in the ModelSim-Altera Edition software when there is randomization, coverage, or an assertion in a SystemVerilog file used for simulation. The ModelSim-Altera Edition software does not support randomization, coverage, or assertions. Lines with this feature in your simulation files are ignored. Workaround/Fix To work around this problem, use a simulation tool that supports these features, such as QuestaSim or VCS. The simulation results are not affected when these features are used.

-

Применить лицензионное ПО, которое наше ПАО может купить официально. Сименс с нами не дружит. для нас будет двойная пересадка: с win на linux и с одного ПО на другое. Но, если другого выхода не будет, то дорогу осилит идущий. Запрос в https://www.synopsys.com я уже сделал. боюсь, это - не наш вариант. Я не компетентен в вопросе, но есть подозрение, что DO-254, по которому мы работаем, не предполагает использование подобного рода ПО за табличку спасибо, но из неё глаз цепляется только за то, что Вы упомянули выше

-

Всем добра! Чем, кроме Active-HDL, можно заменить ПО указанной в теме компании в целях верификации (временной и покрытия)?

-

Сам вопрос задал, сам и отвечаю: не может. Вопрос считаю закрытым.

-

Были бы coding rules, я был бы счастливее, а пока приходится искать и подглядывать чужое. Вы бы не могли, так сказать, не безвозмездно, конечно, дать взглянуть на Ваш код? "Клянусь, я никому не скажу!" как сказал Воланд Берлиозу в сцене встречи на Патриарших из "Мастера и Маргариты" Михаила Афанасьевича Булгакова.