valerony

Участник-

Постов

20 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о valerony

-

Звание

Участник

-

помогите с вопросом по созданию собственных компонентов в Qsys, а именно: как указать конкретный путь сохранения итоговой оболочки- файла _hw.tcl? проблема в том что имея готовые файлы описания-HDL, запуская Quartus без открытия проекта, и запустив там Qsys (для создания компонента) он без ведома установит по пути c:/altera, а мне нужно как положено в папку ip (как и все остальные компоненты лежат). Если оставить так получится неразбериха, плюс могут возникнуть проблемы с использованием данного компонента, т.к. Qsys его не обнаружит. Единственный выход который на данный момент я нашел, это для будущего компонента в нужной папке специально собирать проект для данного модуля, и только тогда _hw.tcl файл сохранится в нужной папке. Может быть есть какой то более правильный и легкий способ добавления собственного компонента?

-

Вопрос по DDR3

valerony ответил _sda тема в Работаем с ПЛИС, области применения, выбор

хотелось бы записывать/считывать данные в блоках памяти (ее наличие как таковой и способность запоминать ))...), как написал aaarrr, можно выключить режим DLL, тогда частоту можно снижать, вплоть до частоты обновления. Пока буду пробовать на CycloneIII, надеюсь что-нибудь получится... -

Вопрос по DDR3

valerony ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Если бы это было для конкретного проекта, то я бы естественно поставил хоть SRAM, но стоит задача в функциональной проверке именно DDR3 -

Вопрос по DDR3

valerony ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Спасибо за ответ. Т.е. минимальная работа DDR3 на частоте 300МГц. У меня задача состоит в том, чтобы хоть как-то проверить функциональность этой памяти. Поддерживаются DDR3 начиная с CycloneV, отладочные платы с ними есть, но там выведены только GPIO, и память туда не подключить. Придется делать свою многослойную печатную плату, паять BGA корпус... -

Вопрос по DDR3

valerony ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Товарищи, у меня тоже вопрос по DDR3. Можно ли запустить работу DDR3 памяти на CycloneIII, хотя бы на пониженной частоте, например 50МГц? В квартусе контроллеры DDR3 для 3-го циклона не доступны, и вопрос как раз в том, по какой причине. Или это физически невозможно, или просто 3-й циклон не тянет те частоты, тогда контроллер можно написать самому, хотя бы для запуска памяти на низкой частоте. -

Все, разобрался... необходимо чтобы в системе (в диспетчере устройств) был хотя бы 1 COM порт, иначе программа не обнаружив ни одного COM порта выдает такую ошибку. После подключения программатора работающего по виртуальному COM порту, все заработало

-

Помогите понять в чем может быть проблема, на некоторых ПК openmsp430-minidebug.tcl запускается без проблем, на других выходит ошибка: Точнее пробовал на двух ПК (на каких была возмножность) на работе, все запускается, даже непосредственно с флешки (Windows8, Windows10). А дома на нетбуке (Windows7), и на ПК (Windows10) выходит такая ошибка, как будто проблема с портами uart...

-

Все! получилось запустить! Пишу и запускаю команды на компиляцию в notepad++, загружаю и отлаживаю в minidebuger. Оказалось можно обойтись и без MinGW, я использовал make от AVR Studio4 который был установлен, наверняка можно и от какого либо другого тулчейна на gcc. В планах переделать "под себя" rtl, сделать несколько версий: полную, среднюю, и минимальную. Возможно получится его уменьшить в размере, впереди много интересного...

-

В intrinsics.h написано /* Insert an eint instruction. This enables maskable interrupts, such as those from peripheral devices. */ void __eint (void); т.е. нужно написать эту функцию самому. Странно что они сами ее не написали, вроде для всех msp430 она должна быть одинаковой.

-

in430.h присутствует в старых компиляторах, в некоторых он заменяется intrinsics.h, в общем с этим понятно, но теперь компилятор не понимает функцию __eint() , т.е. непонятно то ли файла не хватает, то ли в ручную прописывать что-то нужно

-

Когда запускаю компиляцию утилитой make, сообщает что отсутствует файл in430.h И действительно, такого файла нигде нет ни в компиляторе mspgcc, ни в RedHat версии. Подскажите какой компилятор взять?

-

Спасибо, похоже на то... Я в своем проекте просто их закомментировал, и вообще модуль pll не включил. Похоже это для увеличения "fanout". Короче проект с имеющимся .mif с мигающим портом работает. Огромное спасибо автору особенно за этот mif т.к. позволил оценить функциональность. По поводу makefile разбираюсь..., пока нашел литературу по утилите make, как с ней работать и в таком духе...

-

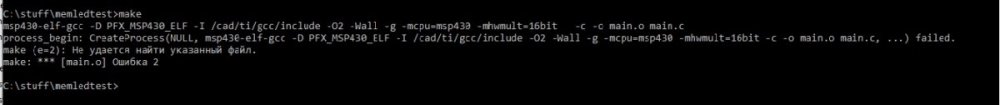

Остановился на этапе конвертирования в формат mif. Поставил MinGW, mspgcc отсюда: https://sourceforge.net/projects/mspgcc/files/latest/download, прописал в переменную Path расположение их /bin (от MinGW и mspgcc). В командной строке захожу в папку с проектом memledtest, ввожу "make" и получаю ошибку: MinGW вроде как отдельно работает- компилирует. Может mspgcc не подходит, (не подходящая версия), хотя пробовал и другие, и такой же результат был. Или в MinGW не хватает какого-то пакета, в чем может быть проблема? Что необходимо устанавливать в MinGW чтобы было достаточно для нормальной работы?

-

Помогите разобраться пожалуйста. В файле OpenMSP430_fpga.v две строчки: global gbuf_clk_sys (.in( oc25m ), .out( clk_sys ) ); global gbuf_reset_n (.in( ~oRst ), .out( reset_n ) ); Выглядит как установка двух экзепляров модулей "global", но таких модулей в проекте я не нашел. Кто подскажет может это какие-то стандартные блоки veriloga типа "and"? Где можно увидеть их описание?

-

Спасибо, теперь понятно, не внимательно смотрел )