el.d

Участник-

Постов

42 -

Зарегистрирован

-

Посещение

Весь контент el.d

-

Скляр, разомкнутые символьные синхронизаторы

el.d ответил el.d тема в Алгоритмы ЦОС (DSP)

Вот да, есть такое подозрение. Возможно, перевод кривоват, надо бы найти оригинал. Кстати, раз пользовались, то какую нелинейность использовали? Так импульсы тактовой частоты и не изображены на картинке. Вообще, они в книжке Скляра вообще нигде не рисуются (возможно ошибаюсь, так как читал её не полностью). В аналоговом виде не катит, надо в цифровом. Это же возможно? :05: -

Скляр, разомкнутые символьные синхронизаторы

el.d опубликовал тема в Алгоритмы ЦОС (DSP)

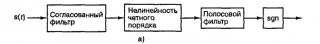

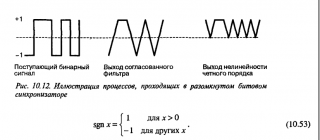

Здравствуйте. Возникли вопросы по тексту издания 2003 года книжки Скляра "Цифровая связь" (стр. 646-647). Схема и ряд поясняющих к ней картинок прилагается. 1. Судя по поясняющей картинке и тексту главы (по тексту написано некое "квадратичное устройство") , "нелинейность четного порядка" = возведение в квадрат выхода СФ. Поправьте пожалуйста, если ошибаюсь. 2. Получается, что на выходе нелинейности имеем гармонику в спектре сигнала на частоте тактового генератора. То есть, например, если я имею clock = 20 МГц и полосу сигнала 8 МГц, то для выделения синхронизированного сигнала мне нужен полосовой фильтр с центральной частотой 20 МГц и еще захватить 4 МГц влево-вправо от неё. Однако, если честно, не совсем понимаю как такой фильтр применять. Тактовая частота 20 МГц, и частота дискретизации отсчетов, поступающих на СФ, тоже 20 МГц. Получается, что цифровым фильтром я могу фильтровать от 0 до 10 МГц при таком раскладе. Получается, что надо перед полосовым фильтром поднимать частоту дискретизации? Я правильно понял? И еще: пользовался кто-нибудь данной схемой синхронизации? Если да, то был какой-нибудь ощутимый результат? -

Так если там ничего серьезного не предвидится, то зачем там TCP если можно обойтись UDP....

-

Корка хилых позволяет сделать КИХ фильтр сразу же дециматором/интерполятором...

-

Так ТС же написал, что ядро КИХ фильтра хилых использовал для этого дела

-

И я Только с другого факультета, по всей видимости (радиофизического).

-

Тогда децимацию (процедура понижения частоты дискретизации) вам в руки...

-

Vivado 2017.2 DSP блоки

el.d ответил el.d тема в Среды разработки - обсуждаем САПРы

В 2016.2 задействовано 100% DSP блоков. -

Vivado 2017.2 DSP блоки

el.d ответил el.d тема в Среды разработки - обсуждаем САПРы

Я вот прямо сейчас ради эксперимента откомпилил один и тот же проект в 2016.2 и в 2017.2. В 2016.2 проект собрался, в 2017.2 - нет. -

Vivado 2017.2 DSP блоки

el.d ответил el.d тема в Среды разработки - обсуждаем САПРы

Угу, пишет что надо 137% DSP блоков, а больше 100% она естестно использовать не может, а додуматься перекинуть часть операций на луты сама не может.... При этом в 2016я Вивада додумывалась, но 16ю мне неудобно использовать по ряду причин... -

Vivado 2017.2 DSP блоки

el.d опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Подскажите пожалуйста, как сказать Виваде, чтобы в случае если все DSP блоки задействованы, то остальную математику пускай делает на LUTах? Покрутил настройки синтеза - не получилось никак (( -

Vivado 2017.2 и ILA

el.d ответил el.d тема в Среды разработки - обсуждаем САПРы

Беру слова назад - это не баг, а фича. Пересобрал в версии 2016.2. Она не добавляет новых блоков, но сигнализирует о несоблюдении таймингов. Проблема решилась уменьшением разрядности шины probe. -

Vivado 2017.2 и ILA

el.d ответил el.d тема в Среды разработки - обсуждаем САПРы

Посмотрел куда он добавил блоки DSP и даже челюсть отвалилась. Есть у меня 6 блоков, абсолютно одинаковых - получены размножением при помощи generate. В них есть фильтры - собсно, основные потребители DSP блоков. Вивада в одном из этих блоков оставляет такое же число умножителей как до добавления ILA, а в остальных - увеличивает. Прикольные баги у хилых.... -

Vivado 2017.2 и ILA

el.d ответил el.d тема в Среды разработки - обсуждаем САПРы

Один probe на 1024 бита. Самое смешное, что если переместить ILA в любой другой блок, то всё собирается. -

Vivado 2017.2 и ILA

el.d опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте, коллеги. Есть ПЛИС Artix-7 и проект под неё. Проект собирается с большим запасом почти по всем ресурсам, аппартных DSP блоков остается еще 15% в запасе. Для отладки ставлю ILA, пытаюсь собрать проект - пишет, что DSP блоков не хватает и отказывается собирать. Смотрю отчет по синтезу - действительно, по какой-то причине после добавления ILA стало использоваться почти на 100 блоков DSP больше (я так и не понял почему). Были у кого-нибудь схожие проблемы? Как решали? -

Сравнение сигнала с эталонами

el.d ответил 2expres тема в Алгоритмы ЦОС (DSP)

Вы видимо пропустили то сообщение, где я говорил, что БПФ как раз и используем для вычисления свёртки принятого сигнала с эталоном. Еще раз: свёртка[принятый сигнал,эталон] = ОБПФ[БПФ[принятый сигнал]*БПФ[эталон]]. Это так называемая быстрая свёртка, по результатам - ничем не хуже классической. Доказательство можно посмотреть в любом учебнике по ЦОС. Однако, данный метод точно дает ускорение в случае относительно большого числа точек БПФ (тысячи). Даст ли этот метод прирост в вашем случае - зависит от того, что и как делать. -

Сравнение сигнала с эталонами

el.d ответил 2expres тема в Алгоритмы ЦОС (DSP)

Например, пик корреляционной функции сравнивать с неким порогом. Или сравнивать отклики корреляторов между собой и выбирать наибольший. Как выбрать порог - зависит от задачи. Вообще, то, что вам надо - это самая обычная задача различения сигналов. В любом учебнике по статистической радиотехнике написано, как это делать оптимально в том или ином смысле. -

Сравнение сигнала с эталонами

el.d ответил 2expres тема в Алгоритмы ЦОС (DSP)

Потому что корреляционная функция (результат свёртки принятого сигнала с эталоном) - это функция от времени. После применения БПФ к принятому сигналу или к эталону получается функция от частоты. Не надо никакие амплитуды считать. Тем более, что амплитуда у принятого сигнала очень вряд ли будет для всех наблюдений постоянной. Или в вашей системе если у принятого сигнала амплитуда меньше чем у эталона, но временная диаграмма один в один - то это уже не совпадение? Вам тут уже правильно подсказали почитать про согласованный фильтр. -

Сравнение сигнала с эталонами

el.d ответил 2expres тема в Алгоритмы ЦОС (DSP)

Да, скорее всего выигрыш от вычисления свёртки через БПФ будет весомым для бОльшего количества точек. Правда, ТС ничего про МК не говорил. -

Сравнение сигнала с эталонами

el.d ответил 2expres тема в Алгоритмы ЦОС (DSP)

Ну вы писали, что у вас сигнал из 128 отсчетов. Следовательно, БПФ тоже должен быть на 128 точек - получается, для сравнения сигнала с одним из эталонов надо 2 БПФ, 128 умножений и ОБПФ. -

Сравнение сигнала с эталонами

el.d ответил 2expres тема в Алгоритмы ЦОС (DSP)

Это называется преобразование Гильберта. Только зачем оно здесь? Разве в описанном методе есть какое-то сравнение сигнала с эталоном? Что касается вопроса ТС. Да, можно применить преобразование Фурье. Для сравнения сигналов используют понятие корреляции. Вычисление корреляции двух сигналов = вычисление свёртки этих двух сигналов. БПФ можно использовать для вычисления так называемой быстрой свёртки. В спектральной области свёртка заменяется на простое умножение. То есть, схема примерно такая: есть принятый сигнал s(t) и набор эталонов Ai(t). Вычисляем БПФ[s(t)] и БПФ[Ai(t)]. Вычисляем x = БПФ[s(t)]*БПФ[Ai(t)]. В конце вычисляем ОБПФ[x]. -

Я лично для себя не могу понять, с чем у вас проблема. По сути, то, что описали - это просто обобщение пункта 2. То есть, вы говорите, что грубо говоря в одной VHDL архитектуре встречали множество маленьких процессов. По сути, каждый такой процесс можно рассматривать как отдельный блок, и тогда получаем структуру из пункта 2, разве нет?

-

А разве всегда надо пихать конечный автомат?

-

Однако, если например сделать раз: logic [15:0] test; Сделать два: test = 0; То например та же Vivado ничего не скажет о том, что 32 битное число обрезается до 16 бит. Вопрос, собсно, был вызван тем, что я примерно также и думал, но поигрался с этим делом немного в Vivado 2017 и есть честно не заметил никакой разницы по ресурсам или сообщений синтезатора, что имеются какие-то неиспользуемые биты, которые отбрасываются. Да и работало оно как задумывалось что в симуляции, что в железе. И как бы если нет разницы (интересно было бы послушать, если кто-то эту разницу реально ловил), то зачем писать более длинную конструкцию?

-

А можно вопрос, оффтопом? В чем разница между SPI_Data_Reg = 8'b00000000; SPI_Data_Reg = 8'h00; и SPI_Data_Reg = 0; ?