GREGOR_812

Участник-

Постов

37 -

Зарегистрирован

-

Посещение

Весь контент GREGOR_812

-

Не забудьте ещё погуглить про HELV Motors и его "кофаундеров". Как минимум один из них связан с МММ. Достойные партнёры, иными словами)

-

Спасибо, буду знать)

-

Спасибо за ответ, позвольте уточнить, ёмкость напрямую ставят между базой и эмиттером? Или можно шунтировать верхнее и среднее плечо делителя?

-

Вы указали источники тока на схеме, если я их просто на эмиттерном повторителе выполню, такой вариант подойдёт? Я планирую смотреть фронты тока в цепи лазера ЛД ноунеймовый с алиэкспресс :) 850 нм, 50 мВт, называется HLD850050N5T

-

Спасибо за совет, попробую по Вашей схеме работать. Генераторы подойдут простые, типа эмиттерного повторителя? Или нужно что-то посерьёзнее. Точность установки тока меня в текущей задаче не интересует, главное хорошие фронты меандра.

-

Вы правы, пороговый ток я как раз обеспечиваю смещением, которое я считал так: если на входе у меня размах 3,3 В, то на эмиттере примерно 2,7 В, значит, чтобы нижний транзистор как раз был на границе насыщения, надо чтобы на его коллекторе было около 3 В. Отсюда смещение на верхний транзистор 3,6 В. Да, согласен, он будет входить в насыщение, этого я не учёл, т.к. падение на ЛД приведёт к напряжению на его коллекторе ниже напряжения на базе. Вывод: нужно либо повысить напряжение питания, либо уменьшить эмиттерный резистор, но он и так уже очень маленький, это может к нестабильности смещения привести (хотя тут даже ток покоя довольно существенный, так что может и не приведёт). Меня волнует вопрос, насколько сильно входной сигнал будет влиять на верхний транзистор через цепь смещения и как это подсчитать.

-

В рждшных вагонах номинальное бортовое напряжение 110 В (на самом деле, +- 20 % легко может быть) В вагонах метро номинальное бортовое напряжение 75 В (опять же разброс может быть дикий) Все остальные напряжения: 12, 24, 36, 50(55) это уже специальные напряжения для определённых узлов (например, 55 для АЛС в старых локомотивах). Вообще, вопрос очень размытый, запрашивайте ТЗ у заказчика, там это должно быть указано. Ещё надо помнить, что земли вагона и контактной сети (КС) могут быть как связаны, так и развязаны, поэтому вместо 0 В в жд технике могут говорить -110 В или -3,3 кВ, подразумевая под этим землю вагона или землю КС. Надо уточнять в каждом конкретном случае.

-

Модуляция каскодного источника тока

GREGOR_812 опубликовал тема в Вопросы аналоговой техники

Всем привет! Для модуляции маломощного лазерного диода решил попробовать схему каскодного источника тока. Параметры модуляции: меандр 2 МГц, амплитуда 0-3,3 В, выход -- ножка МК. Параметры лазера: излучаемая мощность 50 мВт, пороговый ток 15-25 мА, рабочий ток 75-85 мА, рабочее напряжение 1,8-2,4 В. Какие могут быть проблемы с этой схемой? Спасибо за внимание -

Большое всем спасибо за советы, чуть позже обновлюсь с учётом всего вышесказанного

-

Что-то я в ступоре, как мне сделать всё-таки тактирование напрямую от SCK, если в зависимости от CPOL и CPHA задвигать данные нужно по разным фронтам. Получается у меня multiple driver

-

Вообще здравая мысль) сейчас попробую сделать именно так

-

Тут опять же зависит от CPHA, если этот бит установлен в 1, то первый бит выставляется на шину только по первому изменению sck, не раньше. Ну и в сам shiftReg данные откуда-то закидываются же) по другому клоку, системному. Опять же получается плодим клоки

-

С этим есть некоторые проблемы: при CPHA = 0 данные выставляются на шине не по sck, а по фронту/спаду (в зависимости от того, какой выбран активный уровень) cs. Клока sck в этот момент ещё нет, поэтому нужно либо ставить отдельный триггер, тактирующийся от cs, либо кидать внешний клок, следящий за изменением cs. Я не хочу плодить клоки

-

Спасибо, уже работаю над ошибками по коду и стилю) Получается, MOSI тоже надо засинхронизировать? Тогда выходит, что у меня основная частота должна быть хотя бы в 3 раза выше, чем частота sck. Что касается автоматических тестов, можете привести пример, как это вообще делается? Я пока ещё не совсем въехал)

-

Мой модуль SPI slave

GREGOR_812 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

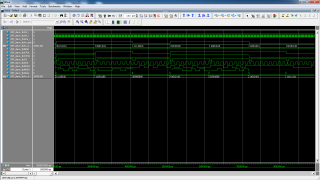

Всем привет! Хочу поделиться (и заодно получить ревью кода) самописным SPI slave модулем. Гитхаб Тестбенч там же, в репозитории. Вот небольшая вырезка из тестов) -

Разобрался) всё-таки действительно я невнимательно проверил код, у меня была запись в регистры по адресу, примерно так: regs[addr] <= w_data;

-

Спасибо. Я на сайте недавно нашёл ещё вот такой документ:MAX_10_Schematic_Review_Worksheet.doc Для других семейств тоже были подобные. Мне показалось, что это достаточно подробное описание

-

Приветствую всех Суть задачи: есть 32 таймера, каждый из них имеет 16-разрядный выходной регистр, где хранится текущее значение, вот его упрощённый код: module timer #( parameter TIMER_WIDTH = 16 )( input logic rst_i, input logic clk_i, input logic ena_i, //... output logic [ TIMER_WIDTH - 1 : 0 ] value_o ); always_ff @( posedge rst_i or posedge clk_i ) begin if ( rst_i ) begin value_o <= '0; end else begin if ( ena_i ) begin value_o <= value_o + 1'b1; end end end endmodule И есть модуль с регистрами шириной 8 бит, память под регистры я объявляю вот так: logic [ 2**ADDR_WIDTH - 1 : 0 ][ DATA_WIDTH - 1 : 0 ] regs; Значения, которые получаются в процессе работы таймеров, должны храниться в этом наборе регистров. Как нужно описать межсоединение таймеров с набором регистров так, чтобы не получалось "лишних" регистров? Пытался делать так (упрощённо): module registers #( parameter ADDR_WIDTH = 7, parameter DATA_WIDTH = 8, parameter NUMBER_OF_TIMERS = 32 )( //... input logic [ NUMBER_OF_TIMERS * TIMER_WIDTH - 1 : 0 ] timers_i, output logic [ NUMBER_OF_TIMERS * TIMER_WIDTH - 1 : 0 ] timers_o, //... ); //... genvar i; generate for (i = 0; i < NUMBER_OF_TIMERS; ++i) begin : some assign timers_o[(i + 1) * TIMER_WIDTH - 1 : i * TIMER_WIDTH] = regs[i * 2 + 1 : i * 2]; assign regs[i * 2 + 1 : i * 2] = timers_i[(i + 1) * TIMER_WIDTH - 1 : i * TIMER_WIDTH]; end endgenerate //... Затем в топе: module top ( //... output logic [ NUMBER_OF_TIMERS * DATA_WIDTH * 2 - 1 : 0 ] timers_o, //... ); //... logic [ NUMBER_OF_TIMERS * DATA_WIDTH * 2 - 1 : 0 ] timers_i; genvar i; generate for ( i = 0; i < 32; ++i ) begin : TIMER timer #( TIMER_WIDTH ) tim ( .*, .value_o ( timers_i[ ( ( i + 1 ) * TIMER_WIDTH - 1 ) : ( i * TIMER_WIDTH ) ] ) ); end : TIMER endgenerate registers #( ADDR_WIDTH, DATA_WIDTH, NUMBER_OF_TIMERS ) regs ( .* ); //... В итоге получаю вот такую картину: Не понимаю, откуда ещё берутся драйверы, если их нет. Я даже цепи сброса удалил, причём на остальные 500 цепей никаких ошибок не вылазит (или после какого-то числа ошибок компиляция завершается автоматически?) Заранее благодарю за помощь

-

Пока что работаю в Altium, всё устраивает) всем спасибо за ответы, буду копать

-

Чё-то тут тоже негусто, честно говоря)

-

Спасибо, я почему-то не додумался в этом разделе искать :rolleyes:

-

Всем привет! Столкнулся с одной проблемой: на сайте Altera не нашёл ни одного аппноута по схемотехнике или референсных схем. Буду очень признателен, если поделитесь ссылками или материалами на тему подключения и выбора дифф.пар, подключения служебных пинов чипа, подключения разных банков питания и прочая, и прочая. Заранее спасибо!

-

Contiki OS

GREGOR_812 ответил drozel тема в Операционные системы

Если ещё интересно Гиктаймс -

а сброс кто подключать будет? Да и нагрузку хоть какую на выход

-

Я, конечно, не гуру тестбенчей, но я не понял, какой модуль тестируется и где он, собственно, вообще в этом коде. Всё-таки: свой модуль или найденная подходящая корка? Какие-то пакеты импортируются, которых нет, какие-то экземпляры модулей объявляются, описания которых нигде нет в коде. Смешивается Verilog и SystemVerilog. Вы понимаете, что Вы делаете вообще?