-

Постов

36 -

Зарегистрирован

-

Посещение

Весь контент xanoy

-

Вопрос решен. Документацию на линкер читать повнимательней нужно было :) -l namespec --library=namespec Add the archive or object file specified by namespec to the list of files to link. This option may be used any number of times. If namespec is of the form ‘:filename’, ld will search the library path for a file called filename, otherwise it will search the library path for a file called ‘libnamespec.a’.

-

CoIDE CooCox. Проблема с линкером.

xanoy опубликовал тема в GNU/OpenSource средства разработки

Всем привет. ST недавно выложил скомпилированные библиотеки emWIN (GUI) от SEGGER под свои МК (http://www.st.com/web/en/catalog/tools/FM147/CL1794/SC961/SS1743/PF259225). Я попытался подключить данную библиотеку к проекту в CoIDE, но получил следующее сообщение от линкера: [cc] c:/program files/gnu tools arm embedded/4.7 2013q2/bin/../lib/gcc/arm-none-eabi/4.7.4/../../../../arm-none-eabi/bin/ld.exe: cannot find -lstemwin520d_cm4_gcc [cc] collect2.exe: error: ld returned 1 exit status Настройки линкера: -mcpu=cortex-m4; -mthumb; -g; -nostartfiles; -Map=VFMini_STM32F.map; -O0; --gc-sections; -L; -lm; -Llib\stemwinlibrary520d\lib\; -lstemwin520d_cm4_gcc; -L${linkdir}; -T${linkdir}/arm-gcc-link.ld; Toolchain: GNU Tools ARM Embedded 4.7 2013q2. То ли CoIDE не то подставляет линкеру, то ли библиотека не совсем под GCC. Подскажите пожалуйста в чем может быть проблема. -

Почему магниты притягиваются..:)?

xanoy ответил yrbis тема в Математика и Физика

Нужда в понимании процесса есть и будет потому как магнитное поле как и гравитационное до сих пор не изучено. А ведь если копать то и “гравитатор” получится может. Вот япошки например отжигают: http://www.youtube.com/watch?v=Hs4GXH5Q3Rk или вот это: http://www.youtube.com/watch?v=kCr3lOhMJCg...feature=related Вообще то на www.youtube.com по поиску фразы “magnetic motor” можно найти очень много интересного и не понятного. В общем есть над чем подумать . ;) -

Разные футпринты это круто, только когда для разного исполнения используется своя PCB. А есть возможность просто убирать шелкографию с неиспользуемого компонента на PCB?. Это пригодилось бы для генерации сборочного чертежа. Всем ответившим большое спасибо.

-

Всем привет. Интересует, есть ли в схемном редакторе таких программ САПР как CADANCE, ALTIUM, MENTOR GRAPHIC и т.д., опция, которая позволяет выделить компонент на принципиальной схеме который не должен попасть в BOM report (Bill of material, список к закупке, и т.д.). Данная опция была бы полезна для разных исполнений электронного блока. То есть, по полной принципиальной схеме разводится плата, а в зависимости от исполнения разработчик, отмечает на схеме элементы, которые не должны войти в данное исполнение электронного блока.(На схеме они видны, но автоматическая генерация BOM report не включает их в список. Было бы круто если бы выделенные таким образом компоненты были бы видны в САПР, а на печать выводилась бы схема без данных элементов и связей идущих к ним, или галочка где то в настройках – показывать/не показывать на схеме). Если пойти дальше, хотелось бы что бы данная опция не только определяла вносить ли данный элемент в автоматические отчеты, но и обеспечивала бы возможность в зависимости от исполнения электронного блока задавать разный номинал элемента. В первую очередь хотелось бы узнать есть ли что то подобное в Orcad Capture и в Altium Designer Summer. Просто на данный момент приходится работать с данными программами. Но было бы замечательно если бы откликнулись разработчики которые работаю в других САПРах. За ранее спасибо за ответы.

-

Вариант подходящий только написание ПО много времени займет. Этот чип обязательно закажу, плохо то что нет дров под FreeBSD. Жалко что Intel такие чипы не делает :crying:

-

Нужен чип PCI<->MAC<->MII

xanoy опубликовал тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Добрый день. Не подскажете чип Ethernet контроллера, который состоит из PCI моста и MAC контроллера с выходом на ружу MII интерфейса. Искал в инете подобного пока не нашел. :crying: Есть только чипы у которых наружу выходит media для непосредственного подключения транса, или сериализатор для оптики 1000FX Задумка такая: На PCI вешается Ethernet чип с PCI<->MAC<->MII. К чипу подключается через MII интерфейс PHY, в нутри которого есть сериализатор для внешнего оптического модуля 10/100FX. Реализация на IP core на ПЛИС, пока не подходит, хотя пока это единственный вариант. -

Где какой конденсатор применять.

xanoy ответил xanoy тема в Компоненты

http://klausmobile.narod.ru/appnotes/an_02_caps_pwm_r.htm -

Где какой конденсатор применять.

xanoy ответил xanoy тема в Компоненты

Вот нашел неплохую статью по алюминиевым кондерам. Power_Supplies.pdf -

Где какой конденсатор применять.

xanoy опубликовал тема в Компоненты

Всем привет. Возникла неразбериха на рынке конденсаторов. Появились новые типы конденсаторов, и каждому типу кондера свое применение. Хотелось бы где то нарыть информацию по параметрам кондеров и куда их лучше ставить (снуберы, DC/DC, фильтры). Например: DC/DC. В состав DC/DC в классике входят конденсаторы следующих типов: - высоковольтная керамика (ЭМИ) - электролиты (входной и выходной фильтр) - танталы (выходной фильтр) - низковольтная керамика (входной и выходной фильтр). - обратные связи - снуберы И каждый из перечисленных типов имеет свои параметры, и особенности включения. Хотелось бы узнать почему например тантал стоит в выходном фильтре а не в снубер цепочке, почему к татнатлам такое большое внимание нужно приделить (ESR, запас по напряжению, максимальный ток через тантал, почему от танталов хотят избавиться); электролитический кондер с какими параметрами должен быть в данном случае (токи утечки, напряжение, ????) чем лучше полимерный кондер, ну и т.д. -

Экспорт PCB в Hyperlinks

xanoy опубликовал тема в Altium Designer, DXP, Protel

Привет Всем. Возможен ли экспорт PCB из Protel 99SE в Hyperlinks ? Если да то как экспортировать. -

Расчет волнового сопротивления. Внутренний слой.

xanoy опубликовал тема в Работаем с трассировкой

Мне необходимо рассчитать волновое сопротивление (Zo) проводника во внутреннем слое. Так как внутренних сигнальных слоев два и они не разделены между собой землей, и так же сигналы что в 1-ом внутреннем слое что во 2-ом внутреннем слое не дифференциальные, то выбираю модель для расчета Broadside-coupled stripline. (Модель показана на рисунке который прикреплен к вопросу "BC_strip.JPG"). Мне не понятно почему проводники разных слоев на модели смещены друг относительно друга на величину S. Хотелось бы узнать, что за параметр S, почему смещены проводники друг относительно друга. Исходя из модели, можно предположить, что проводники во внутренних слоях не должны идти друг под другом, если они не дифференциальные. Но это только предположение. Так же для меня не понятна модель Coated Coplanar line (модель показана на рисунке CC_line.JPG). Подскажите, пожалуйста, что по ней рассчитывают. (проводник в шине, или проводник окруженный земляным полигоном, или...). -

Попробуй отдельно создать lib файл с моделью, сгенерить на основе его символ. А в создаваемом проекте в опциях PSpice в кладке library добавь модель как локальную или глобальную. Если заработает, то дальше можешь игратся с подключением модели к общим библиотекам.

-

Привет. У меня есть разводка JTAG программатора HiStar+ Только она в Orcade если нужно сделать гербера - без проблем. Пиши сделаю. Плату собрал - работает без проблем. HiStar_.zip

-

Похоже что разводчик налажал - забыл снять маску с отверстия :)

-

Еще вопрос о разводке диф. пар

xanoy ответил katz тема в Работаем с трассировкой

Потдерживаю. Линии тоже стараюсь вести рядом. Контроль длины и импеданса линии E1 в плате не контралирую - скорости не те. -

Изначально переходные под контактной площадкой использовались для СВЧ техники (как цифровой так и аналоговой), правда они и сейчас используются там же :). Соответсвенно под этот бздык подгонялась и технология монтажа таких плат. Следовательно если сборщик печатных плат может обеспечить качественный монтаж такого типа плат, то никто не заприщяет использовать эту технологию для минитюаризации железяки (но только не злоупотреблять этим (когда на плате есть куча свободного места, а разводчик все детали втулил в один угол, сделал проводники 0.15, переходные диаметром 0.1, и т.д.)). То что технологи ворчать - это нормальная ситуация - они всегда ворчат когда нужно немного напрячься, как и мы все когда нам дают на первый взгляд не подьемную задачу. Если бы небыло бы таких бздыков, небыло бы и технологий. Вобщем перед тем как сделать что то подобное на PCB нужно согласовать с технологоми на производстве PCB, и на монтаже PCB. Если технологи упераются - развязанный разговор помагает найти решение этого вопроса, или альтернативное решение. Удачи. PS. К сожелению не могу найти доку, где было подробно описанно про переходные под контактными площадками, и что самое главное - примеры в картинках :))

-

Vinnetu привет. Читаю эту тему с начала появления ее. Скачал все файлы книги. Просмотрел, и хочу от души поблагодарить Тебя за проделанный труд, который попал в массы. Спасибо за отсутсвие воды в книге и высокоинелектуально-професорско-теоретических оборотов (над присуцтвием которых настаивают некоторые личности - ребята это не та область где это необходимо, поверте). Просматривая книгу я наслаждался - увидел много своих шишек, которые набивал так же как Ты :), увидел много нужных мелочей которые ускальзали от меня до появленя этой книги. Вобщем большой респект Тебе от меня и моих знакомых. Извени что пока не критекую Твою книгу (не вплане граматических ошибок и отсутсвиии професорско-теоретических, высокоинелектуально - маразматических оборотов), просто пока не нашел в книге того места к которому можно было че то добавить. (Хорошим покупателем считается не тот который купил, и ушел, а ктороый может оставить пожилания или замечания которые кординально влияют на дальнейшее качество товара). У меня к Тебе вопрос. Некоторые люди не могут слить файлы с репиды по определенным причинам. Можно ли вылаживать Твою книгу на подобных репиде серверах? Как пример caxapa.ru/upload ?. Жду от Тебя ответа :) Лутшей книги на руском по процессу создания дизайна ПП я еще не встричал :)

-

Orcad 10

xanoy ответил iantonenko тема в Разрабатываем ПП в САПР - PCB development

Stackup settings - эт что за новорот такой? Чето в Layoute не вижу такого -

Странная заливка на PCB

xanoy ответил xanoy тема в Работаем с трассировкой

Я седне уезжаю на две недельки в отпуск, приеду поговорим ок? А за пример из жизни спасибо :) -

Странная заливка на PCB

xanoy ответил xanoy тема в Работаем с трассировкой

Плата от цифровой станции Ericsson - жудко навороченная, многооо слойная. Я ее купил на разборку за 20 баков :))) Привет Jul. Твой ответ более похож на правду, потому как дорожки на плате шириной примерно 0,1 а то и меньше, переходные отверстия тоже 0,1 или меньше - их практически не видно. А такого типа полигоны просматриваются как в верхних слоях так и во внутренних. Если все так как Ты говоришь, то поидее разработчику ПП не нужно заботится об протравке - это должен делать изготовитель ПП. В каком то CAD наверное есть какая то команда которая автоматом делает такие полигоны. И извени меня за то что проболаболил с переводом документации PADS на русский язык :( -

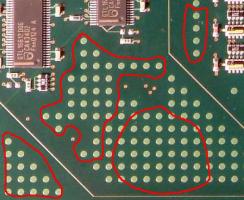

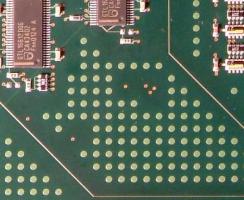

Странная заливка на PCB

xanoy ответил xanoy тема в Работаем с трассировкой

Точки без зеленки - эт переходные отверстия, интересуют более толстые точки покрытие зеленкой - вот(все что обведенно красным): Это чисто визуальное заключение или обмерены импедансы относительно возможных точек? Судя по картинке полигоны не такие уж маленькие, можно и не заметить коннект. Возможно конечно и для отвода тепла, но если есть полигоны то почему-бы их не использовать для повышения помехоустойчивости дизайна? Вот держу плату в руках. Никакого конекта к этим точкам- полигонам нет. А вот почему они не используют полигон для помехозащиты.. я и сам не знаю. Че и спрашиваю. -

Странная заливка на PCB

xanoy ответил xanoy тема в Работаем с трассировкой

Эти мелкие полигоны сидят только на текстолите, и не соеденены ни со дним сигнальным проводом. К стате такие полигоны я встречал только на многослойных платах (8слоев и выше). -

Странная заливка на PCB

xanoy опубликовал тема в Работаем с трассировкой

Такую странную заливку заметил уже давно, только вот не понятно зачем? Почему просто не залить все свобожное место платы сплошним полигоном и приконектить его к земле? Здесь же все свободное место заливается мелкими полигонами в виде круга, ромба и т.д., и эти полигоны никак не соединяются с землей. Мне товарищь примерно обьсянил для чего : что бы плата не коробилась при нагреве ее вместе с компонентасми в печке. Но так ли это? Если это так, то почему? -

Похоже этой опции в Orcad 9.2 небыло :unsure: Спасибо, буду разбиратся :)