chirik8807

Свой-

Постов

132 -

Зарегистрирован

-

Посещение

Весь контент chirik8807

-

ALTERA DE1-SoC Продам

chirik8807 ответил chirik8807 тема в Продам

UP - 17 тр. - Четверг-Пятницу буду в Питере. -

ALTERA DE1-SoC Продам

chirik8807 опубликовал тема в Продам

Продам плату ALTERA DE1-SoC с Cyclone V на борту и ARM ядром. Описание платы https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=836 Цена -19 тр - Москва 9251422748 Могу отправить почтой. -

Моя почта и тел Воробьев Александр 925_14_22_748 [email protected] Я на linkedin https://www.linkedin.com/in/alexander-vorobyev-46506a36/

-

И не подскажите почему в примерах при генерации dts в sopc2dts указывают опцию --bridge-removal all ??

-

Это я подправил, иначе он не компилировал .dtb )

-

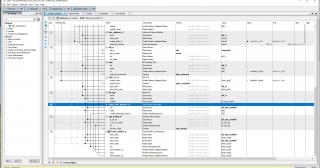

Всем привет! Взял за основу пример для платы DE10_Standard -> DE10_Standard_GHRD (quartus, qsys, soc_system.dts) 1) Добавил блок Frame Buffer II (и соответственно тестовую таблицу и вывод видео) 2) Добавил в hps еще один интерфейс f2h_sdram1 soc_system.rar Внес изменения в soc_system.dts но в нем есть места в которых я не уверен. мой DE10_GHRD_vip_soc_system.dts: DE10_GHRD_vip_soc_system.txt Описание в нем Frame Buffer II https://github.com/terasic/linux-socfpga/bl...eo/altvipfb.txt В нем почему то не строчки с клоком clocks = <&clk_0>; как в других блоках, так и должно быть? По ангиологии поправил описание моста Здесь жирным цветом, то что я добавил правильно ли? И в описании клоков clocks этот клок не задан, не совсем понял, что это за клок и нужен ли он мне?

-

При таком подходе проблем с sysid_qsys id и timestamp не возникает? они же будут не соответствовать заново генерированной системе из qsys ? sysid_qsys: sysid@0x100001000 { compatible = "altr,sysid-16.1", "altr,sysid-1.0"; reg = <0x00000001 0x00001000 0x00000008>; clocks = <&clk_0>; id = <2899645186>; timestamp = <1492500749>; }; //end sysid@0x100001000 (sysid_qsys)

-

Вручную подправил dts-файл, но линукс так и не стал грузиться - Bad Linux ARM zImage magic! С коллегой выяснили почему бьется zImage, все просто - после записи zImage в DDR память, эту же область памяти использует Frame Buffer и перезаписывает ее картинкой)

-

Т.е. из GHRD мы должны взять .dts или .xml и дописать туда свое. У меня же получается, что исходный GHRD проект от Terasic под ядро линукса 3.12 А дальнейшая инструкция с https://rocketboards.org/foswiki/Documentation/AVCVGSRD171 под более свежее ядро например. То правильно ли я понимаю, что даже если я сделаю свои .dtb их нельзя будет использовать под более свежие версии линукса?

-

hps_common_board_info.xml и soc_system_board_info.xml. И как вы с ними в итоге решили вопрос?

-

У меня проблема в Device Tree мне нужно сделать свои под DE1-SoC soc_system_board_info.xml и hps_common_board_info.xml я сразу на них не обратил внимание думал, что их генерит qsys. Сейчас попробую разобраться, что там и к чему...

-

В epcs только прошивка для плис. Спасибо за наводящие вопросы! но я начинаю думать на socfpga.dtb...

-

Не, с той же SD картой.

-

Интересно, а почему когда MSEL стояли на загрузку из EPCS, то ядро линукса начинало грузиться?

-

1) preloader-mkpimage.bin (Preloader image) свой генерил на основе своего проекта https://rocketboards.org/foswiki/Documentation/GSRDPreloader 2) socfpga.dtb (Device Tree Blob) свой генерил на основе своего проекта https://rocketboards.org/foswiki/Documentat...ceTreeGenerator 3) u-boot.scr (U-boot script for configuring the FPGA) стандартный по этой инструкции https://rocketboards.org/foswiki/Documentat...ProgrammingFPGA 4) u-boot-cyclone5.img (U-boot image) готовый брал от сюда linux-socfpga-gsrd-16.1-cv-bin.tar.gz https://releases.rocketboards.org/release/2016.10/gsrd/bin/ 5) zImage (Compressed Linux kernel image) готовый из linux-socfpga-gsrd-16.1-cv-bin.tar.gz 6) altera-gsrd-image-cyclone5.tar.gz (Root filesystem as compressed tarball) готовый из linux-socfpga-gsrd-16.1-cv-bin.tar.gz Собирал все это дело, как в описании скриптом make_sdimage.py https://rocketboards.org/foswiki/Documentation/GSRDSdCard

-

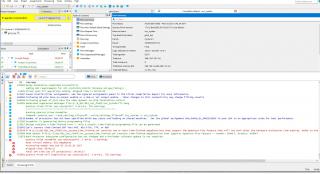

"если пины Bootsel выставлены на загрузку с SD карты, то считывание флешки epcs не должно происходить" И в правду я забыл о MSEL! Теперь прошивка FPGA грузиться, вижу свои полоски на VGA мониторе, но теперь Linux не начинает грузиться.. Hit any key to stop autoboot: 0 reading u-boot.scr 200 bytes read in 3 ms (64.5 KiB/s) ## Executing script at 02000000 reading soc_system.rbf 7007204 bytes read in 331 ms (20.2 MiB/s) ## Starting application at 0x3FF79584 ... ## Application terminated, rc = 0x0 reading zImage 4051904 bytes read in 192 ms (20.1 MiB/s) reading socfpga.dtb 18955 bytes read in 6 ms (3 MiB/s) Bad Linux ARM zImage magic! reading zImage 4051904 bytes read in 192 ms (20.1 MiB/s) reading socfpga.dtb 18955 bytes read in 6 ms (3 MiB/s) Bad Linux ARM zImage magic! SOCFPGA_CYCLONE5 #

-

"её на карту памяти под именем soc_system.rbf" - я так и делаю. по умолчанию это которая pof из EPCS. В этой статье говорят, что включение fpga2sdram необходимо выполнять в U-boot и добавляют следующие строки https://habrahabr.ru/company/metrotek/blog/263571/ ... fpgadata=0x10000000 fpgafile=/lib/firmware/fpga/fpga.rbf fpgaboot=setenv fpga2sdram_handoff 0x3fff; ext2load mmc 0:2 ${fpgadata} ${fpgafile}; fpga load 0 ${fpgadata} ${filesize} bridge_enable_handoff=mw $fpgaintf ${fpgaintf_handoff}; go $fpga2sdram_apply; mw $fpga2sdram ${fpga2sdram_handoff}; mw $axibridge ${axibridge_handoff}; mw $l3remap ${l3remap_handoff} bootcmd=run fpgaboot; run bridge_enable_handoff; run mmcboot ...

-

Всем привет! 1) Сделал пример в qsys: генератор картинки- > фрейм буфер на памяти DDR3 ARMa -> VGA генератор (за основу взял пример от terasic, и с их образом SD-карты мой пример работает - вижу цветные полосы на мониторе) 2) Делаю свою SD-карту по описанию https://rocketboards.org/foswiki/Documentation/AVCVGSRD161 3) Прошиваю образ на флешку и при запуске вижу следующее: - В fpga прошивка по умолчанию (судя по терминалу плис прошивается, но потом такое ощущение, что ресет проскакивает и плис снова с прошивкой по умолчанию) Hit any key to stop autoboot: 0 reading u-boot.scr 200 bytes read in 4 ms (48.8 KiB/s) ## Executing script at 02000000 reading soc_system.rbf 7007204 bytes read in 331 ms (20.2 MiB/s) ## Starting application at 0x3FF79584 ... **** - После загрузка останавливается Starting kernel ... [ 0.000000] Booting Linux on physical CPU 0x0 **** [ 1.041385] of_cfs_init: OK [ 1.047017] ttyS0 - failed to request DMA [ 1.051082] Waiting for root device /dev/mmcblk0p2... terminal.txt Я так понимаю, что запуск fpga2sdram не прошел. У меня есть подозрение, что я не могу использовать настройку u-boot.scr по умолчанию https://rocketboards.org/foswiki/Documentat...ProgrammingFPGA fatload mmc 0:1 $fpgadata soc_system.rbf; fpga load 0 $fpgadata $filesize; run bridge_enable_handoff; run mmcload; run mmcboot; Хочу узнать ваше мнение, это в u-boot.scr нужно дополнительно конфигурировать fpga2sdram ? И еще вопрос, почему прошивка плис не проходит?

-

Лицензия для Quartus решила это проблему.

-

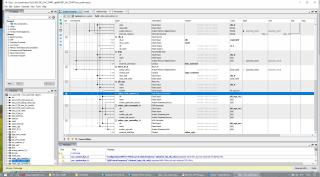

Проблема осталась. Делаю проект для DE1-SOC (взял за основу пример my_first_hps-fpga_base) 1) Добавил в qsys IP блоки генератор сигнала и vga генератор, которые из библиотеки University Program Все хорошо, проект компилируется, прошивается и работает. 2) Переделываю проект добавляю IP ядра Альтеровские Frame Buffer II из DSP/Video and Image Processing и другие... Компиляция останавливаться вот с таким сообщением: И я не понимаю, что приводит к останову компиляции, отсутствие лицензии на OpenCore Plus feature -- Vendor: 0x6AF7, Product: 0x00F5 ??

-

Если вам не нужна крутая графика, а просто вывод графика или графиков, то это можно сделать и на ПЛИС https://www.youtube.com/watch?v=8O06kx9tA2w https://www.youtube.com/watch?v=P2Jpszg-6YQ

-

Ок, спасибо! нашел инфу https://habrahabr.ru/company/metrotek/blog/235707/

-

Stewart Little, вы правы файл time-limited.SOF генерируется! это я не сразу догнал на что квартус ругаться и останавливает компиляцию. Warning (11713): The configuration of the Hard Processor Subsystem (HPS) within this design has changed. The Preloader software that initializes the HPS requires an update. Using hps_isw_handoff/soc_system_ddr3_0_hps/, run the Preloader Support Package Generator to update your Preloader software и как мне его запустить Preloader Support Package Generator ? soc_system_ddr3_0_hps.rar

-

Как это можно поправить?