shuric

Участник-

Постов

56 -

Зарегистрирован

Весь контент shuric

-

Altium Designer 19, Fix/UnFix

shuric ответил shuric тема в Altium Designer, DXP, Protel

popms, спасибо большое! -

Altium Designer 19, Fix/UnFix

shuric опубликовал тема в Altium Designer, DXP, Protel

Как можно зафиксировать и расфиксировать элемент от случайного перемемещения в Altium Designer 19 по аналогии с P-cad 2002 Fix/UnFix? -

Разобрался сам. Оказывается если в графе Comment Properties написать номинал резистора =1 без каких либо символов Om, kOm,или хотя бы пробела, Навигация этот резистор не перемещает. Спасибо всем за участие.

-

shuric Altium Designer 19, Навигация

shuric опубликовал тема в Altium Designer, DXP, Protel

При нажатии на элемент в окне Навигация, некоторые элементы не перемещаются, не смотря на компеляцию. Появляется сообщение - "Cannot be navigated due to the closure of owner doсument. Project should be recompiled before proceeding. " Подскажите, в чем причина. Спасибо. EXPER.PcbDoc EXPER.SchDoc PCB_Project.PrjPcb PCB_Project.PrjPcbStructure Project Group 1 EXPER.DsnWrk -

Altium Designer 19, Навигация

shuric ответил shuric тема в Altium Designer, DXP, Protel

В том то и дело, что компелировал и со схемы и с pcb, но почему то резисторы определенного типа не перемещает навигатор со схемы, хотя эти резисторы выполнены по тем же правилам, что и другого типа. -

Altium Designer 19, Навигация

shuric опубликовал тема в Altium Designer, DXP, Protel

При нажатии на элемент в окне Навигация, некоторые элементы не перемещаются, не смотря на компеляцию. Появляется сообщение - "Cannot be navigated due to the closure of owner doсument. Project should be recompiled before proceeding. " Подскажите, в чем причина. Спасибо. -

3D Модель

shuric ответил shuric тема в Altium Designer, DXP, Protel

Hermound, большое спасибо, Вы мне очень помогли. -

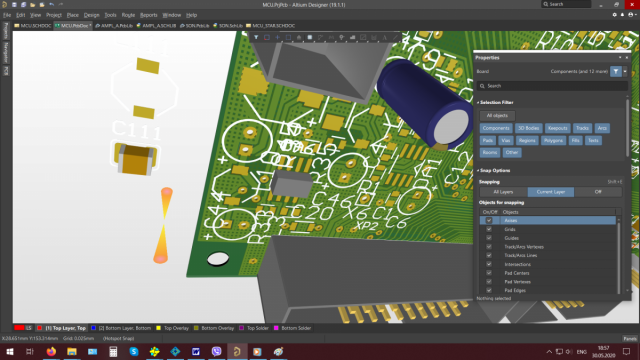

3D Модель

shuric опубликовал тема в Altium Designer, DXP, Protel

Помогите скачать из интернета бесплатно 3D модель разъема KGR 80 с расширение .step. или .stp. -

3D Модель

shuric опубликовал тема в В помощь начинающему

Помогите скачать из интернета бесплатно 3D модель разъема KGR 80 с расширение .step. -

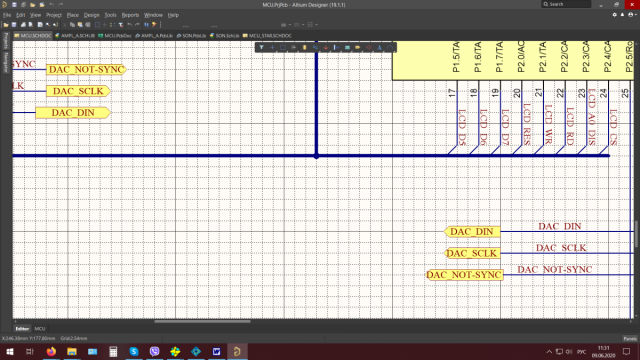

Имелось ввиду ошибка - details floating net label DAC_DIN, а не шина связи. Еще по поводу этих же цепей возникает такая ошибка "Net DAC_DIN has no driving source (Pin DD1-7,Pin DD2-28)" А насчет "Сделайте все цепи Global" Спасибо. Нужно почитать матчасть, или там просто где то галочку поставить? Тогда может подскажете где.

-

Подскажите, кто знает, если возникает ошибка - details floating net label, это означает, что соответствующие цепи на плате не будут соединены? И для их соединения необходимо обязательно их связывать с шинами? Очень громоздко и неудобно!

-

Спасибо Lninio. Обновил и все получилось.

-

Я и говорю, что при переносе на плату пропадает слой 3D шелкографии ( нет характерной зачерченной розовой области ), хотя в библиотеке 3D вид отображается. Согласен, Lninio, нужно все сказанное Вами переварить и проанализировать. Надписи я действительно никакие не делал.

-

Altium Designer 19, изчезает слой шелкографии

shuric опубликовал тема в Altium Designer, DXP, Protel

Создал патен L111 3D Body в 13 мех. слое. В *.LibPcb патен визуализируется, как в 2D так и в 3D. При установке этого патена на плату *.PcbDoc пропадает слой шелкографии 3D и в объемном виде патен L111 не визуализируется, хотя при этом патен С111 визуализируется, как в 2D так и в 3D. Помогите пожалуйста разобраться. -

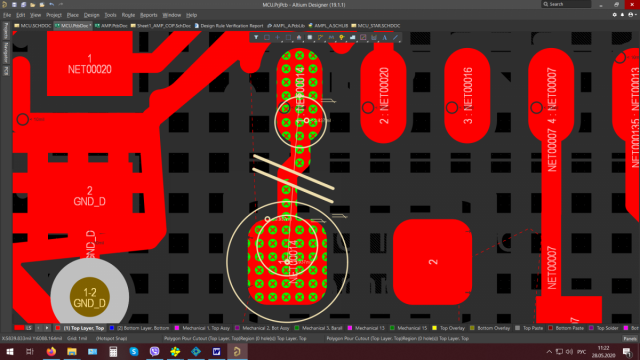

Designator86 - это первичное наименование, просто не стал переименовывать, ничего под ним не лежит. Тыщу раз проверено. Я выбрал другой Footprint, который на этом месте работает. Видимо,что то некорректно с Footprint. Разобраться конечно хотелось бы, но и времени жалко. Спасибо всем за участие.

-

В том то и дело, что все контакты и треки имеют соответствующие цепи. Что то видимо с патеном. Скачал с библиотеки другой патен и все заработало. Но почему же тогда этот патен работает на другой плате? И ошибка какая то стрнная - контакт сам с собой коротит, так вроде и должно быть.

-

Конечно Place\Track

-

Altium Designer 19, ошибки трассировки

shuric опубликовал тема в Altium Designer, DXP, Protel

При установке патена на плату, сразу после соединения его контакта линией связи с другим контактом с соответствующей цепью, моментально возникает непонятная ошибка: Clearance Constraint (Gap=3.937mil) (All),(All) Clearance Constraint: (Collision < 3.937mil) Between Pad Designator86-1(5692.693mil,6120.861mil) on Top Layer, Top And Pad Designator86-1(5692.693mil,6120.861mil) on Top Layer, Top Clearance Constraint: (Collision < 3.937mil) Between Pad Designator86-1(5692.693mil,6120.861mil) on Top Layer, Top And Track (5692.693mil,6120.861mil)(5692.693mil,6164.452mil) on Top Layer, Top Clearance Constraint: (Collision < 3.937mil) Between Pad Designator86-1(5700mil,6220mil) on Top Layer, Top And Track (5700.621mil,6181.52mil)(5700.621mil,6210.964mil) on Top Layer, Top Back to top Short-Circuit Constraint (Allowed=No) (All),(All) Short-Circuit Constraint: Between Pad Designator86-1(5692.693mil,6120.861mil) on Top Layer, Top And Pad Designator86-1(5692.693mil,6120.861mil) on Top Layer, Top Location : [X = 5692.693mil][Y = 6120.861mil] Short-Circuit Constraint: Between Pad Designator86-1(5692.693mil,6120.861mil) on Top Layer, Top And Track (5692.693mil,6120.861mil)(5692.693mil,6164.452mil) on Top Layer, Top Location : [X = 5692.693mil][Y = 6130.649mil] Short-Circuit Constraint: Between Pad Designator86-1(5700mil,6220mil) on Top Layer, Top And Track (5700.621mil,6181.52mil)(5700.621mil,6210.964mil) on Top Layer, Top Location : [X = 5700.621mil][Y = 6204.209mil] При этом при установке этого же патена на другой плате такой ошибки не возникает! Помогите пожалуйста разобраться. -

Спасибо, есть все таки некоторые отличия между компонентами, буду сопоставлять и исправлять.

-

Переименование необходимо, чтобы совпали имена NET в схеме и плате, которые рисовались к сожалению по отдельности.Совпадают только библиотечные элементы и соответствие платы схеме по разводке.

-

А так, чтоб не ставить? У меня очень много таких цепей. И к тому же некрасиво и громоздко, вся схема будет в надписях. В P-cad такого недостатка нет.

-

Altium Designer 19, переименование цепей Wire

shuric опубликовал тема в Altium Designer, DXP, Protel

Как переименовать цепи Wire (Netы) Altium Designer 19 Schematic? -

Спасибо, Владимир. Видимо опыта у меня маловато. Где бы об этом поподробнее почитать?

-

Проблема не не в том, чтобы просто графически нарисовать рамку, а чтобы она была не активна при копировании листа, как в схемном варианте, если Вы в курсе.

-

Altium Designer 19 Форматки для чертежей.

shuric опубликовал тема в Altium Designer, DXP, Protel

Где взять форматки для чертежей плат, или, как создать их самому, нигде не нашел материала. Может поможете? У меня Altium designer 19.