-

Постов

292 -

Зарегистрирован

-

Посещение

Весь контент xor.kruger

-

IMX6 NAND Bad Blocks на одном и том же адресу

xor.kruger опубликовал тема в Linux

Приветствую! Есть девайс с IMX6UL с NAND flash. На разных платах одного и того же самого устройства возникают по одним и тем же адресам что в u-boot что в linux bad blocks В загрузчике nand erase и nand scrub не помогают NAND erase: device 0 offset 0x0, size 0x7000000 Skipping bad block at 0x06000000 Erasing at 0x6fe0000 -- 100% complete. OK NAND scrub: device 0 offset 0x0, size 0x7000000 Erasing at 0x5f20000 -- 85% complete. nand0: MTD Erase failure: -5 Erasing at 0x6fe0000 -- 100% complete. OK В чем может быть причина? В какую сторону стоит копать ? Спасибо за любой совет! -

Реализация обработчика для USB запроса Set Descriptor

xor.kruger опубликовал тема в NXP

Приветствую Реализовывал ли кто нибудь обработчик реквеста Set Descriptor для устройства usb-девайс ? Имеется проблема по данному вопросу: -Каким должен быть корректным ответ девайса на данный запрос. В частности интересует реализация на микроконтроллерах семейства Kinetis фирмы NXP. В предложенными NXP есть usb стек, но в нем отсутствует реализация Set Descriptor. По аналогии с другими реквестами был реализован и Set Descriptor. В результате он срабатывает но не удается получить доступ к полю Data Но также будет полезен любой пример. -

Kinetis and EZPORT

xor.kruger ответил xor.kruger тема в NXP

Нет, т.к. производитель явно указывает что EZPORT явно предназначен для first time programming -

Kinetis and EZPORT

xor.kruger опубликовал тема в NXP

Всем привет! Имеются процессоры NXP, семейства Kinetis MK24. В данных процессорах есть т.н. интерфейс EZPORT которые предназначен для внутрисхемного программирования МК. EZPORT сам по себе представляет по сути SPI интерфейс. Если перед использованием EZPORT с МК работали (программировали) по средством J-Link'a, то проблем никаких нету, но если процессор "голый", только запаянный или у процессора была стерта вся flash-память с помощью J-Link'a - в таком случае при чтении по EZPORT'у статусного регистра - все биты установлены в единицу (0xFF) и МК не отвечает на команды. Но стоит МК снова перепрошить J-Link'ом, как ЕZPORT опять корректно себя ведет. Кто-то сталкивался с подобной проблемой? -

Разводка PCI шины

xor.kruger ответил xor.kruger тема в Работаем с трассировкой

Спасибо большое ответившим! 2 hsoft - то что нужно! буду изучать их разводку на выходных! 2 Serhiy_UA - подскажите, пожалуйста, какие двунаправленные буфера используете? (на том девайсе, фото которого Вы выложили) Может еще кто нибудь подскажет о подводных камнях, которые нужно учитывать при разводке PCI и о которых мало где указанно. -

Разводка PCI шины

xor.kruger опубликовал тема в Работаем с трассировкой

Доброго времени суток! Суть вопроса в принципе понятна из ее названия! Имеется PCI(32bit 33MHz) мастер реализованный на ПЛИС, и достаточно много слейвов: 1. SATA контроллер; 2. PCMCIA контроллер; 3. PCI BUS мост; 4. MiniPCI разъем. В стандарте на PCI указано что длина клоков должна быть 2,5 дюймов, а остальных сигналов 1,5 дюйма, но это при подключении точка-точка. Как быть когда слейвов много, какие допуски на длины цепей? Ну и основной вопрос: какая топология разводки должна быть? Сквозная или дерево (например как у DDR2, при разводке нескольких "банок") ? Если бы кто нибудь поделился примером, можно даже скриншотом PCBшки или gerbor'ов, то было бы вообще замечательно! :rolleyes: Заранее благодарен за любую помощь или совет! -

Надыбал эту старую темку. Решил ответить как я тогда решил данный вопрос. Использовал USB HOST контроллер CY7C67300. Садится на параллельную шину и также просто и отлично работает в GNU/Linux.

-

Сравните все данные из регистров доступных по MDIO, и потом по даташиту ковыряйте.

-

Vivado 2016.1

xor.kruger ответил Alex77 тема в Среды разработки - обсуждаем САПРы

Доброго времени суток! Пробую установить данную версию Вивадо под Windows 7 64 bit. Запускаю xsetup.exe - и глухо как в танке :( (Никаких сообщений об ошибке и окон не выскакивает, просто ноль реакции). Пробовал так же от имени админа - тоже тишина. Может кто-то сталкивался с подобным ? В чем может быть загвоздка ? -

Для этого есть спец. утилита от Xilinx. data2mem называется.

-

Microblaze USB HOST

xor.kruger опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Условно есть достаточно старая ПЛИС от Xilinx - Spartan 3A 3400 DSP. На ней крутится Microblaze и GNU/Linux. Необходимо "прикрутить" USB HOST 2.0 (на крайняк и 1.1 сойдет) контроллер (впринципе неважно как именно, будь то ULPI, Cypress'овский внешний контроллер с паралельной шиной и т.д.) который бы отлично "стыковался" со всей системой и поддерживался Линухом. Максимальная скорость передачи не принципиальна. Пробовал до этого связку со старой коркой xps_usb_host_v1_02_a и внешним фитером USB3300 но под ОС так и не заработало :smile3046: . Грешу на работу самой IP-CORE. Вообщем решал ли кто-то подобные задачи и каков был успех. Заранее благодарен за любую инфу :cheers: -

Проблемы с сетью в Microblaze

xor.kruger ответил gshadow2 тема в Linux

Смотрите Buildroot и Busybox - разобратся с ними не составит никаких проблем. -

настройка тактирования в embedded linux

xor.kruger ответил Zelepuk тема в Linux

2 Zelepuk: Сюда смотрели ? ../arch/arm/mach-davinci/da850.c -

Проблемы с сетью в Microblaze

xor.kruger ответил gshadow2 тема в Linux

Замените номер phy с 7 на 1. Вот так: phy-handle = <&phy0>; mdio { #address-cells = <1>; #size-cells = <0>; phy0: phy@1 { compatible = "marvell,88e1111"; device_type = "ethernet-phy"; reg = <1>; }; Должно помочь. -

Проблемы с сетью в Microblaze

xor.kruger ответил gshadow2 тема в Linux

Приведите кусок DTS файл в котором описан ethernetLite. -

Попробую поменять DRIVE на меньшее значение. Сейчас оно равно 12 мА. Кстати, с таким как-то раз реально столкнулся - на VGA. Линии вертикальной и горизонтальной синхронизации близко разместил на плате и в результате чего взаимные наводки "рушили всю идилию", помогло уменьшение значения DRIVE.

-

Скажу проще: есть два модуля - у них есть IDC-ные разъемы - вот туда подключается "приблуда" с ответной частью на котором разъем и карта. Тоесть разъем и карта памяти одна и таже. На столе два модуля. 3E - работает. 6 - нет :(

-

Да, одна и та же

-

Частоты полностью одинаковы - 25 МГц 3,3 V - в двух проектах Блин, уже даже и не знаю куда копать :(

-

Microblaze SPI MMC

xor.kruger опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Доброго времени суток! Есть проект на Spartan 3E - Microblaze с кучей периферии и интерфейсом SPI к которому подключена карточка MMC; на системе стоит Linux и все отлично работает - карточка определяется, чтение запись проходит отлично. Перевел проект на Spartan 6 - все тоже самое, все отлично работает кроме MMC. Софт тот же. Вот такая проблема, так как программная часть как и в предыдущем варианте, остается грешить на ПЛИС. Смотрел осцилографом - данные бегают. Я грешу на поведение пинов в шестом Спартане. Что подскажите уважаемые специалисты ? Заранее благодарен за любой совет! ЗЫ: и в первом и во втором случае карточка подключена напрямую к пинам ПЛИС. -

Спасибо за консультацию!

-

Для этой цели собственно и был выбран LP2995. Наверное так и буду делать. Но скажите честно, Вы так делали в связке FPGA<->DDR? :) Просто переспрашиваю, боюсь что бы не стабильно работало.

-

Скопипастить как вариант, но хотелось бы разобраться :) Не понимаю почему у Xilinx написано по одному а сделано по другому.

-

одна

-

Spartan 3A и DDR SDRAM

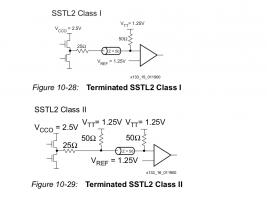

xor.kruger опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Развожу плату со стареньким Spartan 3A и памятью Micron - MT46V128M8P-6T. При подключении памяти используется стандарт SSTL_2 который требует Vref и Vtt. В качестве источника напряжения Vref и Vtt используется техасовский DDR Termination Regulator - LP2995. В стандарте на SSTL_2 (class I) указано что необходимо два резистора - один последовательный на 25 Ом, второй параллельный на 50 Ом подтянутый к Vtt. (Скриншот из ксайлиновского даташита в аттаче). Решив все перепроверить, скачал схему на фирменную отладочную плату Xilinx (только со Spartan 3Е и подобной памятью) и наблюдаю следующую картину: параллельные термирующие резисторы отсутствуют, а последовательные имеют номинал - 75 Ом. С этой платой давненько приходилось работать - все отлично. Собственно вопрос - как необходимо правильно делать :) Заранее благодарен за любой совет !