-

Постов

231 -

Зарегистрирован

-

Посещение

Весь контент serg_Fry

-

Добрый день. Нужен один экземпляр приемника временной синхронизации NVS-GNSS-MTA. С действующей (еще хотя бы 2-3 мес.) поверкой, но оформленной не позднее 24.02.2021. Нужен для исользования в Казахстане, там еще не успели продлить срок действия сертификата типа средства измерения. Ограничения по датам поверки позволит избежать волокиты. По этой же причине не вышло просто купить новый. Нужен один экземпляр. Готовы приобрести за наличные или б/н от юр. лица. Либо взять в аренду на несколько месяцев. Готовы обсуждать варианты. +7(916)914-2O58 Сергей

- 1 ответ

-

- nvs-gnss-mta

- поверка

- (и ещё 6 )

-

500 об./мин. - это, как я писал выше, нижний порог рабочих оборотов. В среднем без редукторов-ремней можно рассчитывать на 2000 об./мин. Будем пробовать несколько вариантов. Напишу здесь что получим по результатам. Вы же сами выше возмущались некорректному обращению. Теперь сами проявляете себя не лучшим образом. Я указал применение т.к. считаю это правильным, когда консультируюсь с кем-либо. Сама задача реальная и коммерческая . Требования основаны на существующей практике. Подобные тренажеры уже давно есть на рынке. Нужно сделать just another. Аккумулятор и автономность - конкурентное преимущество. Заказчик занимается этой темой не первый год и постановка задачи выглядит вполне зрелой. Я готов обсуждать задачу шире, если есть желание. Тема интересная. Но не в этом специализированном разделе. Готов принять в качестве конструктива, что термин "телеметрия" может не совсем отражает роль электронной части в данном случае. Пусть будет "система сбора данных." :)

-

Вопрос про чувствительность нагрузки от генератора для спортсмена действительно неоднозначный. Это тренажер для гребли на байдарке. Усилие на руки через весло. В составе тренажера есть регулируемый воздушный тормоз, который дает нагрузку и работает постоянно. По данным аналогичных тренажеров при таком темпе спортсмен выдает мощность порядка 60 Вт. То есть генератор добавит примерно 25% к нагрузке. Это нижний порог интенсивности тренировок - худший случай. Скорее всего достаточно будет учитывать потери на генератор при расчете основных параметров тренировки и понимать, что сколько-то теряем снизу от диапазона регулировки нагрузки (можно скомпенсировать за счет ослабления воздушного тормоза). В самом худшем случае придется ограничивать ток заряда при малых оборотах. По поводу ощущения дискретности усилия на генераторе для спортсмена: мне кажется, если в составе генератора будет 6 и более магнитов, не должно быть явно заметно на таких оборотах. Но это нужно проверять. Заявленное потребление (15 Вт) - это максимально возможное потребление электроники с небольшим запасом. Причем потребление не зависит от темпа в котором работает спортсмен. Логика простая: чтобы тренажер был автономен, в среднем генератор должен выдавать больше чем потребляет электроника. Обороты в 500 об./мин, которые я указал в первом сообщении выбраны аналитически. Это условно возможные минимальные обороты, которые могут удерживаться значительное время. Понятно, что могут быть специфические тренировки например восстановительного плана при которых спортсмен ооочень медленно работает и в принципе не способен покрыть штатное потребление электроники тренажера. Поэтому в целом гарантировать автономность невозможно. На практике, руководствуясь средними реальными значениями, - можно для подавляющего числа случаев. Рад, что есть относительное единство мнений в типе мотора. Поле для выбора претендентов на попробовать сузилось. Еще вопрос: грубо можно оценить запас на КПД механики+генератора? на выходе хотим чистыми 15 Вт, значит нужно брать электромотор с заявленной мощностью ??? Вт (берем худший случай, для оборотов 3000 об./мин.). С учетом, что заявленная мощность мотора не для режима генератора, а наоборот. Субъективно, мне кажется мотор от самоката или героскутора в 250Вт+ - это многовато как-то. Не хочется иметь дело с щетками и их заменой. Возможно это предрассудки. В любом случае, если в бюджет влезет бесщеточный вариант, то он предпочтителен.

-

Подскажите, пожалуйста, наиболее подходящий класс электродвигателей. Нужно сделать систему телеметрии тренажера. Есть желание реализовать заряд аккумуляторов от вращения вала, который приводит в движение спортсмен. Есть вал, нижний порог рабочих оборотов: 500 об./мин. Думаю, сможем поставить ременную передачу или редуктор и поднять обороты на валу планируемого генератора. Предварительно это будут единицы тысяч оборотов в мин (3000-7000 об./мин.) . В конечном счете нужно получить 5VDC 2.5А+ (12.5 Вт). Пока рассматриваем вариант трехфазных бесколлекторных моторчиков, которые применяются в коптерах. Но выбор в значительной степени интуитивный и несистемный. Поэтому хочется проконсультироваться с экспертами в данном вопросе.

-

Спасибо за подсказку. Да, обратная связь по току экрана. Экран довольно инерциальный на затухание. Поэтому скорее интегральным. Да. Я выше писал про ёмкость фотокадод-выход_МКП и емкость вход-выход_МКП. Эти 2 ёмкости существенно отличаются. Поэтому их совместная коммутация будет заведомо медленнее (фронты) чем только коммутация нагрузки ФК-вход_МКП. И то и другое. Импульсное управление существенно расширяет рабочий диапазон вх. яркостей в сторону яркого света. При достаточно коротком минимальном импульсе отпадает потребность в защитных диафрагмах на дневном свете. Про смотреть на солнце - не хочу загадывать, все зависит от того, какие фронты и мин. длительность импульса сможем обеспечить. И собственно управление получается довольно скоростное, что позволяет сделать качественный автомат регулировки яркостей чтобы наблюдатель с комфортом работал даже в условиях вспышек и резких изменений освещенности сцены. Плюс вроде бы расширяется динамический диапазон (пока экспериментально не проверяли). И это тоже. В тумане, в дождь, под водой и прочее подобное. Это называется "активно-импульсная подсветка". Похоже у вас есть опыт по этому направлению.

-

Интересная идея. Ёмкость МКП существенно больше чем у фотокатода. В результате фронт будет получаться по худшему условию. Но это нужно оценить количественно, может приемлемо получится. Да, вариант с каскадированием - рабочий. Будет ступенька на фронтах. И они, соответственно, будут больше. Так и есть. Это два основных приоритета: короткие фронты и по возможности малое потребление, боремся за каждый мВт и нс. Не очень понятно, как будет работать наш случай, униполярного отрицательного напряжения (0, -800В). Боюсь, не понял вопрос. Транс делает питание, которое нужно коммутировать, на выходе нужны импульсы. Нашли интересный вариант. Пока проверили на малых напряжениях. Генератор выдает биполярные импульсы ±2.5В. Со средней точки снимаем уже униполярные импульсы, смещенные в отрицательную область. Ровно как нам нужно. Получается что-то типа недоумножителя напряжения.

-

Этот вариант рассматривали, но еще не пробовали. Попробуем. Боюсь не смогу показать: не все в команде согласны. Не уверен, что понял идею про полумост и мост. У нас сейчас просто с трансформатора диодом обрезается нижняя полуволна. Можно поставить полный мост и это позволит уменьшить коэфф. трансформации. Но на выходе нам по-прежнему нужно -800В. МПК мы не коммутируем, там постоянное напряжение. И с землями в схеме все сложно. Одним словом, так не получится сделать.

-

Разрабатываем высоковольтный источник питания для ЭОП. Для импульсного управления фотокатодом нужно формировать ШИМ-сигнал: уровни: -800В (Low), 0В (High); фронты - не более 15нс. Нагрузка (фотокатод ЭОП'а) - емкостная, 20пФ; длительность импульса от 65нс до 990мкс; частота повторения - 1 кГц; Не можем найти подходящий высоковольтный (напряжение пробоя сток-исток менее -800В) P-канальный полевой транзистор. Размер корпуса важен. Токи мизерные, поэтому к мощности никакие требования. Запустили свою схему пока с TC1550 от Superex Inc (ныне Microchip). Все работает, но нужно 800В, а он может только 500. Буду благодарен за любые советы и предложения.

-

HV P-channel MOSFET (BVdss<-800v)

serg_Fry опубликовал тема в Транзисторы

Разыскиваю высоковольтный (напряжение пробоя сток-исток менее -800В) P-канальный полевой транзистор. Времена фронтов - не более 15нс. Работать будет на емкостную нагрузку (20пФ). Корпус SMD, размер критичен, как можно меньше. В идеале пару P+N в одном корпусе. Сейчас успешно используем TC1550 от Superex Inc (ныне Microchip). Но он всего на 500В, хочется больше. Буду благодарен за любые советы и предложения. -

удлинитель wifi антенны 20+ метров

serg_Fry ответил serg_Fry тема в RF & Microwave Design

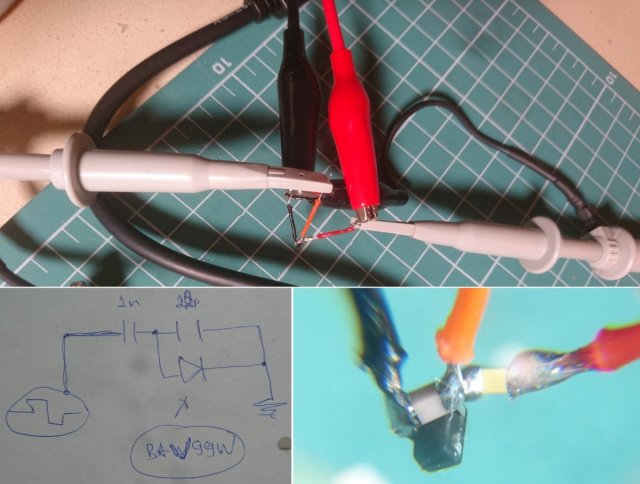

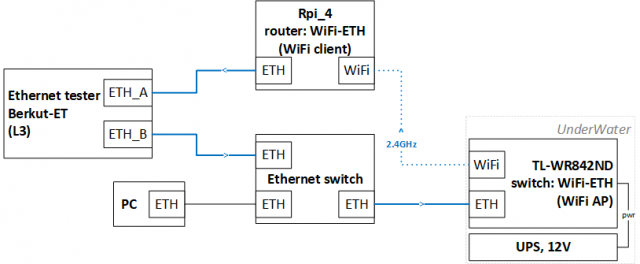

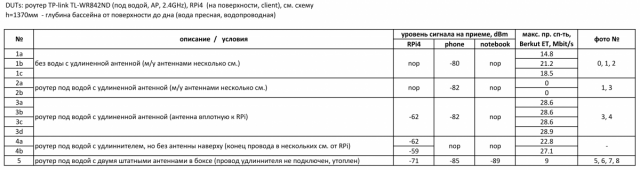

Результаты первичных тестов под водой: * удлинитель антенны 2.4 GHz WiFi: RG-178 (20м); * глубина бассейна: 1370мм (пресная водопроводная вода без хлорки); * DUTs: RPi4b; router TL-WR842ND; Berkut-ET; *фото эксперимента: * Структурная схема тестов (односторонний трафик, т.к. WiFi полудуплексный и потенциальная камера будет иметь сильно асимметричный трафик): * результаты замеров: Резюме: 1. Уровень сигнала с учетом потерь на удлинителе (20м. провод, ручная пайка разъемов, антенна) и примитивной антенне на поверхности порядка -65dBm при минимальном расстоянии м/у антеннами (вплотную, на RPi планарная антенна на плате). Реальная пропускная способность при этом 28 Mbit/s. 2. Самое удивительное: 2 штатные антенны в подводном боксе пробиваются из-под 120+см. глубины: -71dBm, 9Mbit/s (провод удлинителя отсоединен на подводной стороне и затоплен под воду чтобы исключить влияние). -

удлинитель wifi антенны 20+ метров

serg_Fry ответил serg_Fry тема в RF & Microwave Design

Пока требование к кабелю заявлено как строгое. Попробуем на практике. Если все плохо, то можно использовать активный усилитель, как выше предложил Aner. -

удлинитель wifi антенны 20+ метров

serg_Fry ответил serg_Fry тема в RF & Microwave Design

Есть строгие требования к толщине и гибкости (радиус изгиба) кабеля. Отсюда такой выбор. У RG-178 для 2.4ГГц затухание получается порядка 265 db/100м. То есть оценка потерь в проводе длиной 20м получается порядка 53db. Передатчик выдает 16 dBm. Если для уверенного приема на расстоянии 1 метра на поверхности нужно иметь >-29 dBm, то получается мощности не хватает (16-53=-37dBm). Все правильно понял? Что касается питания, то расчетное потребление подводной части порядка 2-3 Вт. На поверхности есть исходные 5VDC. Поэтому если с передачей по антенне все получается, то нужно поднять напряжение до 24 или 48 В (выберем по факту уточнения потребления нагрузки) . Мы заказали провод (30м RG-178) и разъемы для экспериментов. Для начала попробуем утопить роутер в герметичном контейнере. RF специалистов в команде нет. Хочется не совсем вслепую пробовать варианты с антенной. Просьба не ругать за глупые вопросы. Изначально планировали к торчащему из вод концу прикрутить родную антенну от того же роутера. И попробовать подпаять постоянное питание: + на сердечник землю на экран и снять его снизу. Штатные антенны дешевых роутеров, как я понял, имеют штыревую конфигурацию (оголенный сердечник длиной в 1/4 длины волны, ~31мм). Правильно? Попробуем и GP вариант. -

удлинитель wifi антенны 20+ метров

serg_Fry опубликовал тема в RF & Microwave Design

Есть прикладная задача: вытащить wifi (2.4 ГГц) сигнал из-под воды. Глубина 15-20 метров. Расстояние от торчащего из воды конца до управляющего ПК/телефона менее метра. То есть допустимо существенное затухание на проводе-удлинителе. Провод - в первом приближении RG-178. 1. Для эксперимента нужно рассчитать длину и выбрать конфигурацию антенны (нужны ли ёмкости, дроссель?). 2. Еще дополнительно хотелось бы попробовать передать питание по этому же проводу (DC по центральной жиле). Вопрос: Есть ли подобный опыт/статьи/расчеты...(любые материалы по теме)? -

Есть разовая задача: Приобрели полупроводниковые диоды 1064nm, CW, 100mW. Производитель не предоставляет некоторые параметры, которые нам необходимы. В частности: - распределение интенсивности в световом пучке (beam profile); - позиционирование тела излучения относительно корпуса диода; Ищу лабораторию, где в качестве услуги нам помогут обмерить образцы диодов. Буду благодарен за любые идеи, ссылки.

-

На всякий случай: это просто плата AC-DC с выходом 5В 3А. Можно применять для чего угодно. Габаритные размеры: 59х44х24 мм

- 1 ответ

-

- globalscale

- acdc

- (и ещё 6 )

-

После доработки одноплатных компьютеров SheevaPlug осталось 600 шт. их штатных плат питания. Провод с вилкой 220В в комплекте. На всех 600 шт. обрезан шлейф выхода 5VDC. Сейчас там обрезки проводов даже короче чем на фото. При необходимости можно оперативно выпаять и очистить отверстия от припоя. Платы находятся в Москве. Возможна продажа по б/н расчету от юр. лица. sеrg.sikоev(гaв)gmаil.com +7(916)914-2O5[восемь] Сергей

- 1 ответ

-

- globalscale

- acdc

- (и ещё 6 )

-

Удалось получить модели. Если кому-то понадобятся, пишите в личку.

-

IBIS модели получилось найти. Нужны именно Spice.

-

Для моделирования нужны Spice модели IO блоков семейства UltraScale. На их сайте есть соответствующий раздел, но для скачивания нужны какие-то привилегии. Если у кого-нибудь есть, буду благодарен.

-

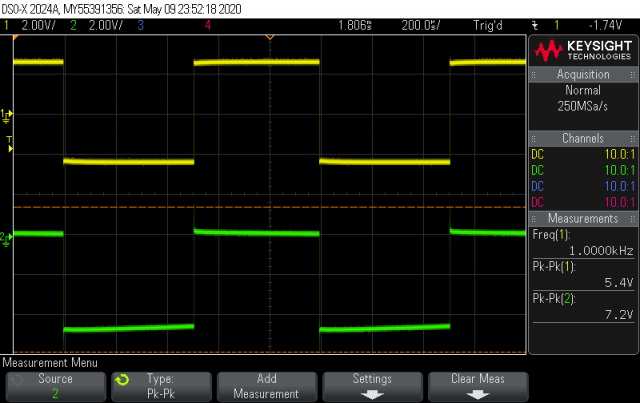

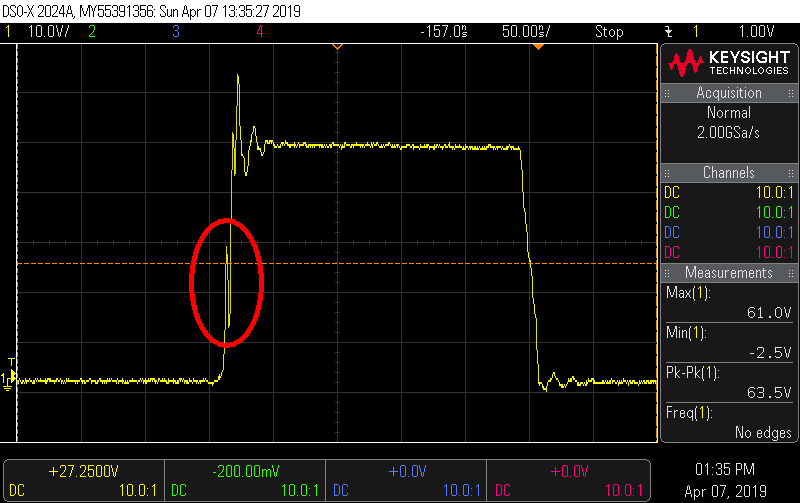

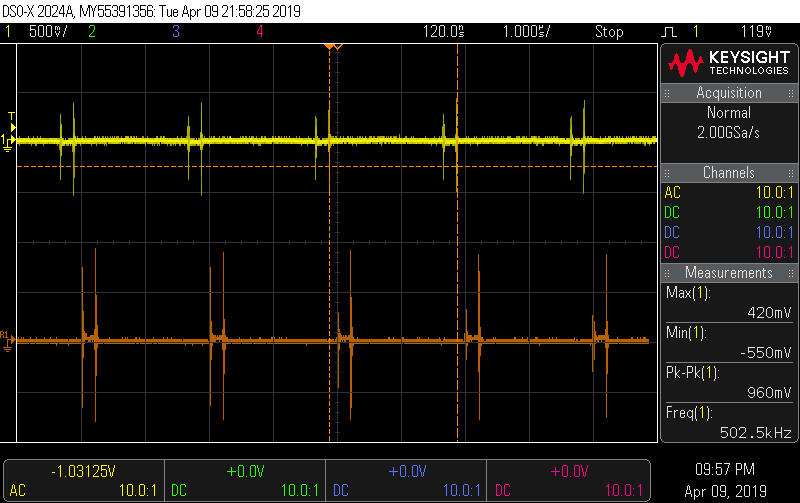

Все верно написали. Именно так и обстоят дела. Помеха в первую очередь идет по эфиру и наводится на щуп. Разница крокодил против пружинки весьма ощутима. Разница с разных сторон от нашей платы тоже заметна. Сделали ход конем, перевернули плату вверх ногами. М/у нами и критичным узлом теперь наш земляной полигон. На целевой плате на входе стоит тантал, на нем уже все чисто с учетом описанных мер. Со снаббером сделали попытку, один фронт завалился, но стал без выбросов и колебаний. Зато на втором образовался большой глитч. В целом стало хуже. Наверняка можно рассчитать снаббер с оптимальными параметрами, но решили с этим не заморачиваться. Еще пробовали поставить на выходе Common Mode Choke фильтр (в частности этот). Сразу после него все чисто, на проводах помеха снова появляется. Понятно, это не устраняет первопричину.

-

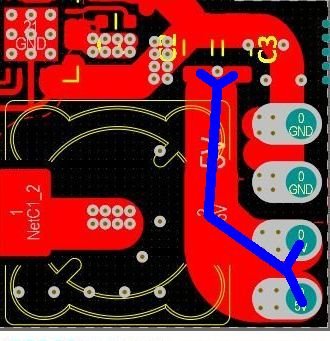

На входе перед преобразованием 48-5В есть еще кусок схемы, отвечающий за защиту от переполюсовки. Чтобы не смущать, обрезал картинку с топологией выше. И там и там измерял с землей на конце щупа, пружинкой. Завтра попробую повторить под нагрузкой.

-

Для сравнения снял выход прямо с обкладок вых. конденсаторов (С2, С3). На картинке: Рыжий(сохранен в Ref) - на клеммнике, куда нагрузку цепляю; Желтый - на вых. конденсаторах. Щуп в режиме AC. Измерял без нагрузки (ХХ). Разница по амплитуде примерно в 2 раза. Ощутимо, но это еще не победа. Кстати, частота колебаний на фронтах, которая лезет помехой порядка 100МГц (см. первый пост). 500кГц - частота работы преобразователя.