MasterElectric

Свой-

Постов

77 -

Зарегистрирован

-

Посещение

Весь контент MasterElectric

-

Распределение памяти, H7, Keil.

MasterElectric ответил Allregia тема в STM

AVI-crak Да нет, просто стартап на асме так удобнее потом переносить в другие проекты. -

Распределение памяти, H7, Keil.

MasterElectric ответил Allregia тема в STM

.equiv RCC_ , 0x58024400 .equiv RCC_AHB2ENR , 0x0DC /* включение SRAM1, SRAM2, SRAM3 */ ldr r0, =RCC_ ldr r1, [r0, #RCC_AHB2ENR] orr r1, r1, #((1 << 29) | (1 << 30) | (1 << 31)) str r1, [r0, #RCC_AHB2ENR] включите в стартапе SRAM -

Помогите отремонтировать J-Link (клон)

MasterElectric ответил MementoMori тема в ARM

jcxz, спасибо за наводку. Купил вчера на otladka.com.ua вроде все нормально, обновился без проблем. -

может причина в этом http://we.easyelectronics.ru/STM32/crc32-na-stm32-kak-na-kompe-ili-na-kompe-kak-na-stm32.html

-

Помогите отремонтировать J-Link (клон)

MasterElectric ответил MementoMori тема в ARM

А можно подробнее где их можно купить или как сделать? -

Это все потому что некоторые регистры буферизируются и их обновление идет при событии Update. TIM16->EGR = TIM_EGR_UG; как раз программно и делает этот Update.

-

STM32H742VG Hardfault

MasterElectric ответил IRBaboon тема в STM

А вы что записываете программу во второй банк? И выбран ли этот адрес в Opton byte? Все-таки что-то не так с адресами флеша. -

Проблема при стирании страниц.

MasterElectric ответил jenya7 тема в ARM

17к для бутлоадера на юарте? А чей код вначале представлен. А то лежат кинетисы и что-то у них с доками ну прям не так как у stm32, на сайте пяток документов и все. Думаю стоит ли их вообще трогать. -

Ну я сразу давал ссылку на статью про аппаратный блок CRC, но судя по всему ТС нужен CRC для обновления прошивки, а свободного времени в бутлоадере 99%, тем более с аппаратным CRC при расчете CRC32 не все нормально.

-

Перемудрил)... нужно еще улучшать

-

STM32H7 испльзование HSEM

MasterElectric ответил smk тема в STM

HSEM есть у всей линейки H7. Под H745 создается как бы два проекта, я бы сказал что там нужно две РТОС использовать. Еще Джозеф Ю писал что для меж ядерного взаимодействия есть специальный интерфейс, но ничего конкретного насколько я помню. -

да и ты чтобы сбросить CRC предлагаешь создавать новый экземпляр класса? Набор штампов как не следует давать советы, подробнее о побочных эффектах пожалуйста и чем это локальная статическая отличается от глобальной кроме зоны видимости?

-

http://we.easyelectronics.ru/STM32/crc32-na-stm32-kak-na-kompe-ili-na-kompe-kak-na-stm32.html вот тух хорошо расписано почему так вышло)

-

STM32H7 испльзование HSEM

MasterElectric ответил smk тема в STM

А М4 что все это время спит? или нужно мгновенно начать действия? Зачем через прерывания? -

STM32H7, SPI, прием с DMA

MasterElectric ответил sst78rus тема в STM

smk а SPI заработал с ДМА? Какая у вас ревизия чипа? -

STM32h743 стирание данных из флешь

MasterElectric ответил Alex_Golubev тема в STM

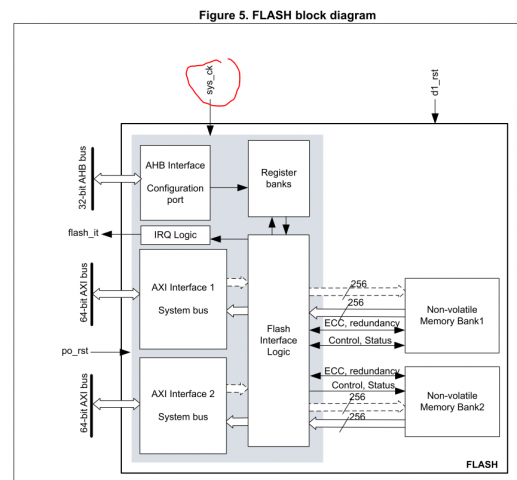

AleksBak, вы же видели картинку контроллера флеш памяти и наверняка заметили что за один раз он считывает по 256 бит данных (даже есть FIFO небольшой), а это 16 инструкций или в худшем случае 8. Шина AXI 64 битная и пересылки идут по 64 бита. Не так все и плохо. А для циклов кэш как раз и хорошо дополняет. Но запустив DWT вы всегда можете сравнить что да как. -

STM32h743 стирание данных из флешь

MasterElectric ответил Alex_Golubev тема в STM

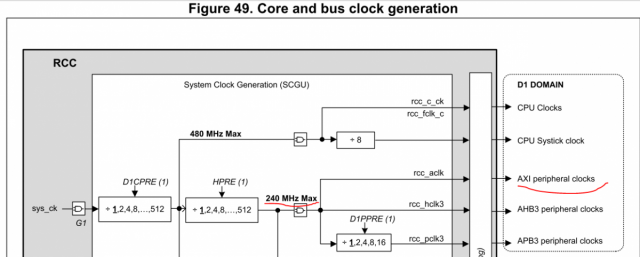

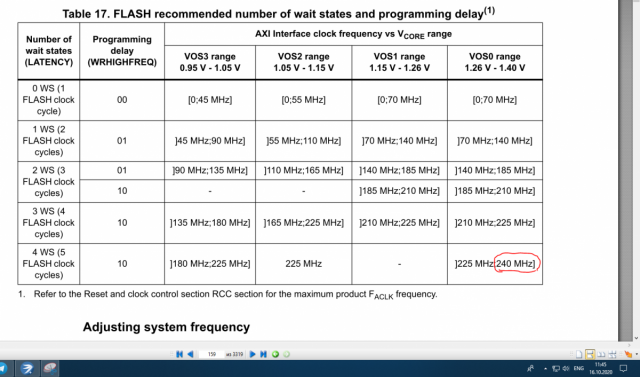

VOS0 range 1.26 V - 1.40 V, где оно пониженное? как раз на таком напряжении ядра и возможно тактирование при 480. это стандартная опция, можно и так и так. Кстати по этому поводу в Y есть эррата что на самом деле не делит, в V исправили. -

STM32h743 стирание данных из флешь

MasterElectric ответил Alex_Golubev тема в STM

Смотрите. Модуль FLASH. Далее по тексту табличка с сигналами и написано что sys_ck - D1 domain bus clock (embedded Flash memory AXI interface clock), т.е. это тактовая шины AXI. Хотя название сигнала sys_ck странно выбрано. -

STM32h743 стирание данных из флешь

MasterElectric ответил Alex_Golubev тема в STM

Alex Golubev Вам нужно все-таки почитать Reference manual, табличка оттуда, страницу видно на скрине. en.DM00314099.pdf -

STM32h743 стирание данных из флешь

MasterElectric ответил Alex_Golubev тема в STM

-

STM32h743 стирание данных из флешь

MasterElectric ответил Alex_Golubev тема в STM

FLASH->ACR = FLASH_ACR_LATENCY_3WS | FLASH_ACR_WRHIGHFREQ_1; -

а почему QSPI именно 66 МГц, шина вроде как должна уметь 133 МГц или это ограничение вашей памяти?

-

короткая таблица это только системные прерывания. т.е. нет смысла создавать таблицу которая будет просто висеть, вектора то в ОЗУ. Ну это не тот случай много все-таки телодвижений еще нужно сделать... плохая идея.

-

_Desh, еще для экономии флеша можно сделать короткую таблицу прерываний во флеше, экономит приличное количество памяти. Вы собираетесь что затирать весь флешь и бутлоадер тоже?

-

SEGGER SystemView для FREERTOS10

MasterElectric ответил zorromen тема в ARM

Интереснее было бы с исходниками. Я хотел бы изучить возможности этой SysnemView и хотел бы прикрутить к своему диспетчеру задач.