PCB.Designer

Участник-

Постов

30 -

Зарегистрирован

-

Посещение

Весь контент PCB.Designer

-

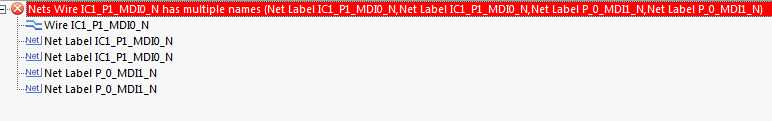

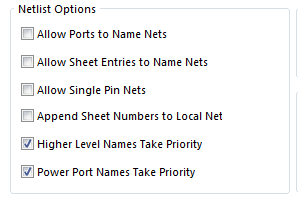

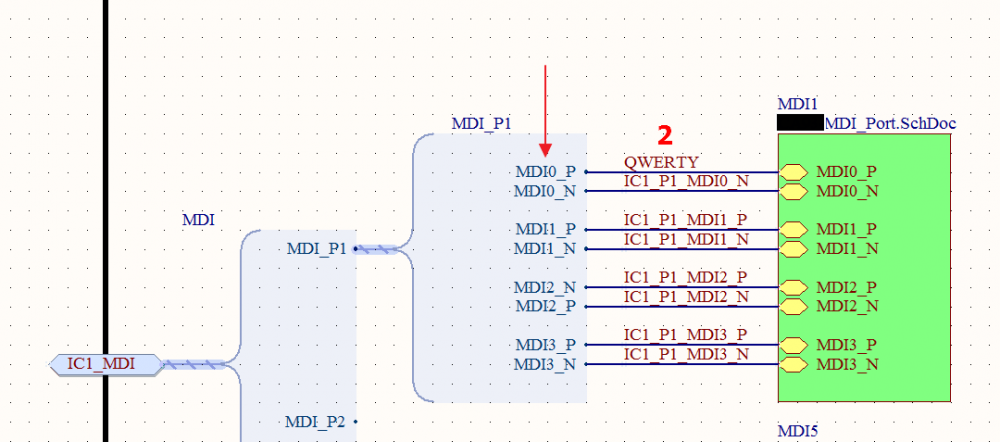

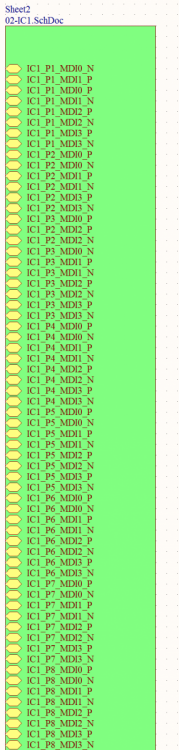

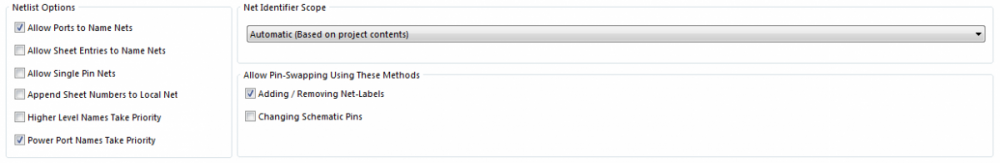

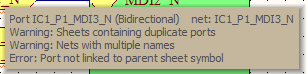

спасибо, так и сделал. Владимир, насколько я знаю NetLabel в AD назначает локальное имя цепи на листе. Почему тогда AD ругается, что цепь имеет несколько названии? Метка IC1_P1_MDI0_P на разных листах, а AD считает что она глобальна. Вот опции по названиям цепей

-

Не знаю, хочу оставить Repeat, а как реализовать без Harness не знаю пока как.

-

Вот тебе и гибкость AD :( Жаль.

-

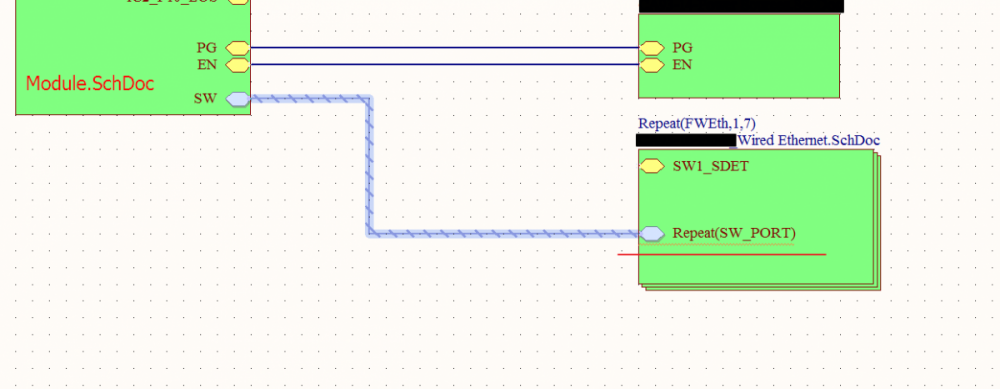

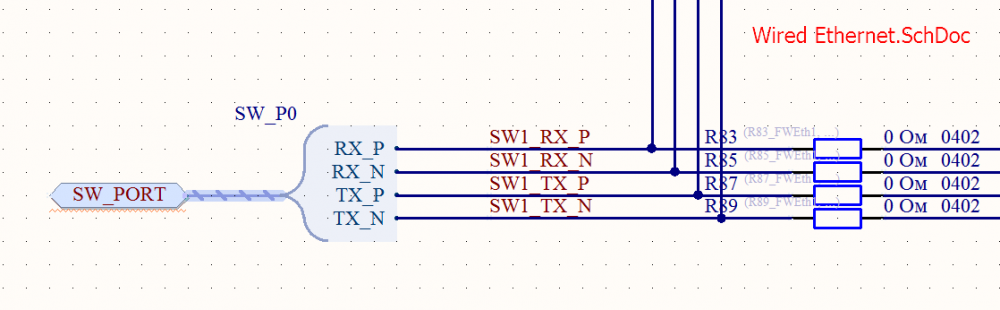

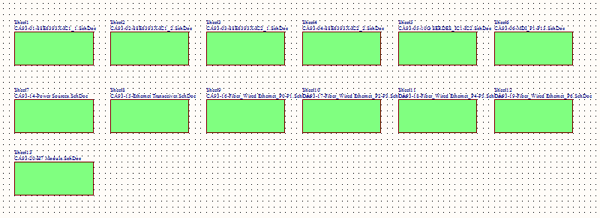

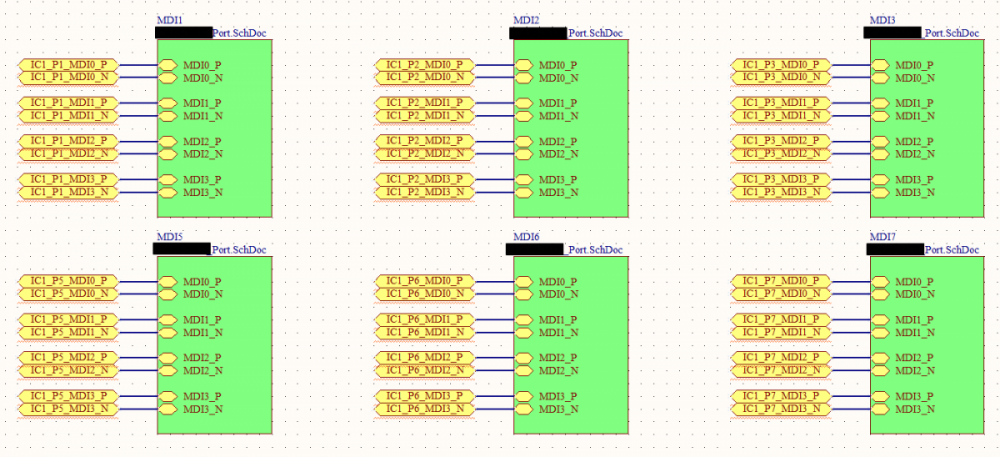

Владимир, подскажите, что тут не так? Пытаюсь сделать 7 кусков схемы Wired Ethernet.schdoc через Repeat, но вижу, что делаю что-то не так.

-

Владимир, а Port 'ы могут иметь одинаковые названия на разных дочерних листах ???

-

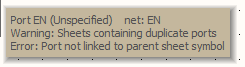

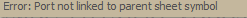

Видимо из-за отсутствия опыта работы со жгутами, пока так оставлю. Не знаю что сделал, видимо довел все порты, волнистая исчезла. Владимир, так же можно передать сигнал EN вверх через метку и порт? И почему тогда ошибка у порта EN? пишет про дубликаты портов, хотя на этом дочернем листе ОДИН PORT EN и 8 штук NetLabel EN. NetLabel можно ставить в одном месте, не обязательно на всех листах, или вообще не ставить Понял, спасибо.

-

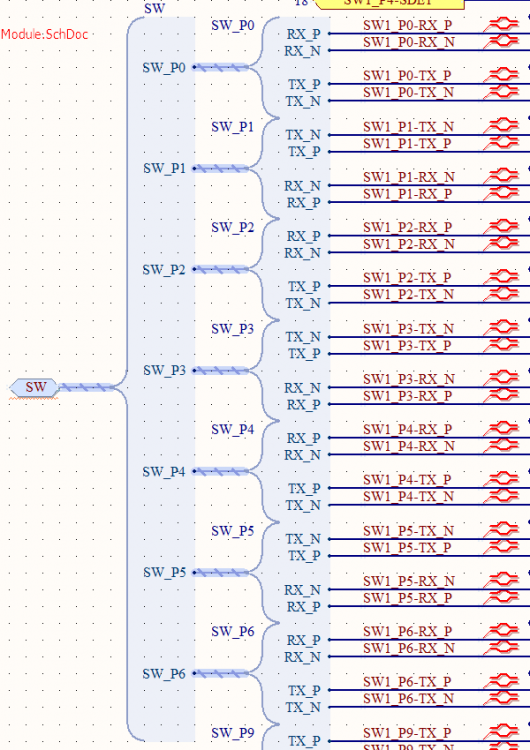

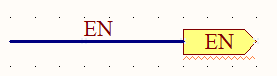

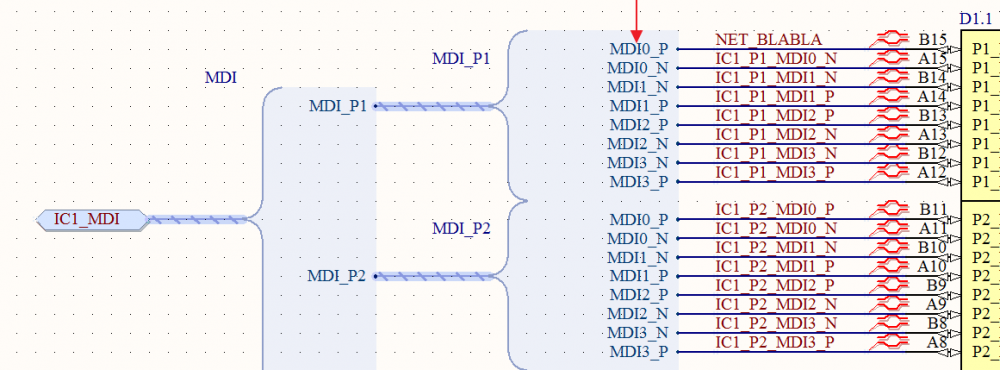

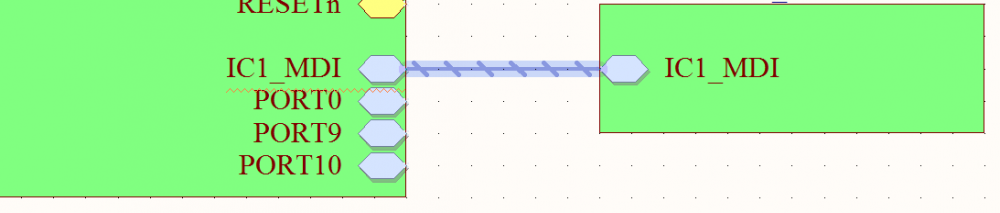

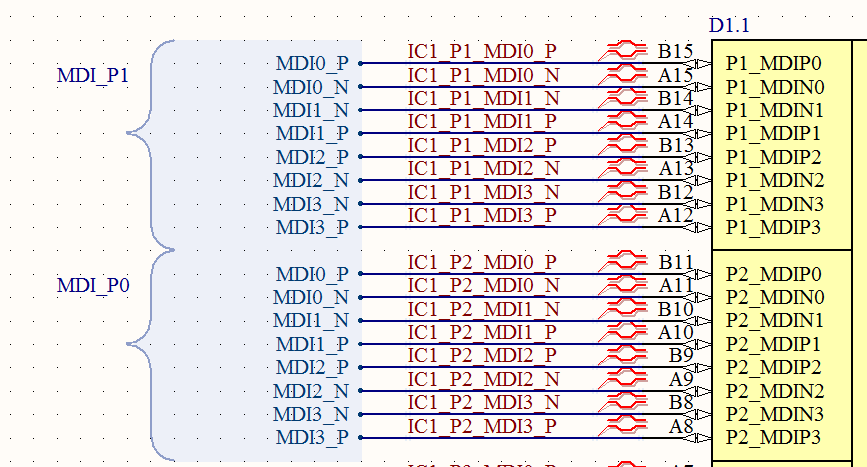

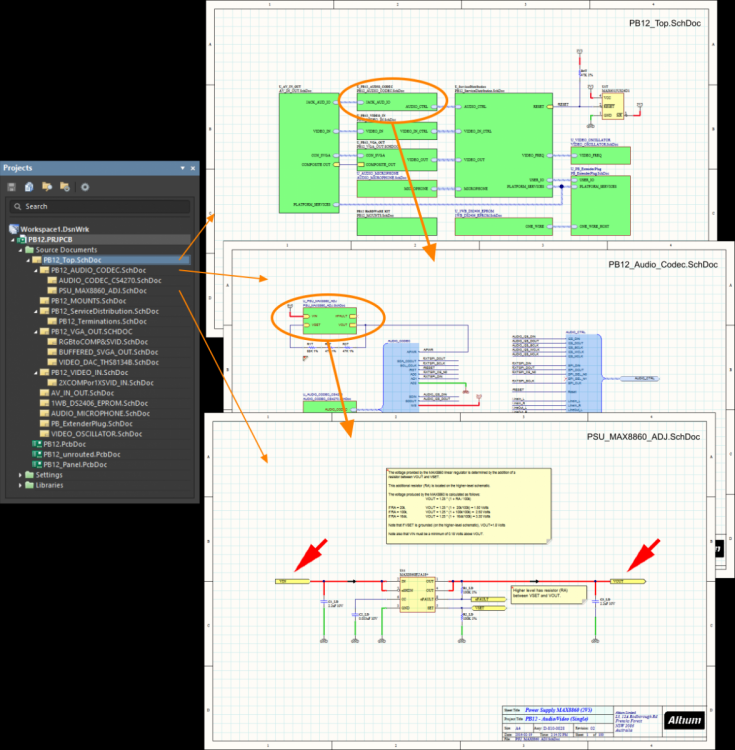

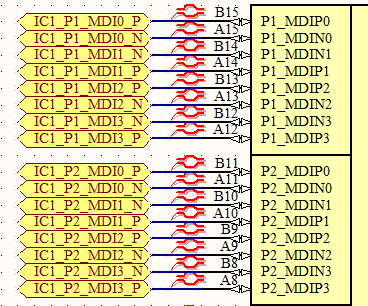

Владимир, а правильно я понимаю, что когда передаем на верх цепи через Harness conector и Порт, то важно чтобы Harness Entries имели одинаковые названия (показал стрелками)? И в этом случае можно не давать названия цепям через NetLabel, так? см рис. я специально дал разные названия NetLabel для MDI0_P. Как по вашему, можно еще как-нибудь это сократить? на главной странице вот так у меня

-

Более менее ясно. Подскажите, я правильно начал использовать Harness connector для передачи цепей с дочернего листа на верх ? порты еще не нарисовал. И нужно ли давать разные имена для Harness connector MDI_P1, MDI_P2 (они идентичны по значению) в моем случае ?

-

Владимир, по поводу вашего листа выше, синий цвет - это жгуты, а оранжевый - это что? И почему на жгут поставили NetLabel? для чего это?

-

Я просто пытаюсь понять как работает эта многоканальность, я до этого никогда с Sheet Symbol не работал, все проекты были Flat. Про Harness только слышал, сейчас надо разбираться что это такое. По вашему листу видно что Port вообще не используются, я этого не знал к сожалению, порты в Hierarchical Design работают только снизу-вверх. Спасибо, за помощь! буду дальше разбираться.

-

А можно как-то обойтись без SheetSymbol с кучей sheet entry ??? Ведь есть лист с микросхемой и нужно просто соединить ее цепи с цепями тех каналов , которые я создал через SheetSymbol. Вот как можно обойтись без этого (см. SheetSymbol с кучей sheet entry ) ? когда есть лист с микросхемой , но через Ports я не могу соединить ее сигналы с SheetSymbol .

-

Так эти порты находятся на верхнем уровне , а не в дочерних листах. Получается что Ports не работают в таком виде! в Иерархическом проекте Ports "работают" только в нижнем уровне, так ведь??? Даже на картинке в документации AD показаны Ports только в нижнем уровне. Так как мне соединить дифф. цепи от SheetSymbol с микросхемой, когда они находятся на разных листах?

-

первый лист у меня такой. Через шину именовать + netlabel? Так же проще именовать цепи. ГДЕ? нет одинаковых названий. А обязательно выводить sheet entry в SheetSymbol ? это поэтому компилятор ругается? - если не сложно, киньте плиз доступный для понимания материал по этому вопросу. главное развернутый, можно на англ. языке. спасибо.

-

Имеется ввиду сам объект Port в AD? И что в этом случае поможет? и да, AD говорит что после компиляции нет связи дифф пар от SheetSymbol к микросхеме. как ее сделать тогда?

-

Мультиканальность в схеме.

PCB.Designer опубликовал тема в Altium Designer, DXP, Protel

Всем привет! Ни разу не делал многоканальные проекты. Возникли вопросы. Есть кусок схемы (Port.SchDoc) и его надо размножить на 16 каналов. Для краткости сделал скриншот на 6 каналов . Что я сделал: 1.Вставил SheetSymbol , указал для него путь к схеме Port.SchDoc, вытащил из схемы 8 sheet entry (4 дифф.пары) 2. Размножил на 16 SheetSymbols . 3. Соединил все дифф. пары от 16 SheetSymbols на одну микросхему. Во-первых компилятор выдаёт такие ошибки 1. Почему он ругается что листы имеют дубликаты портов? 2. что значит Port not linked to parent sheet symbol? 3. Что я делаю не так? :) -

Подскажите, есть проект из инета (https://github.com/MinnowBoard-org/design-files) , так вот там файла .sbk вообще нет, в какой папке хранятся листы схемы?

-

Всем привет! Есть схема Э3 в файле .sbk. Как и чем её открыть? В итоге хотелось бы конвертнуть её в Altium. Какие есть варианты? Предполагаю, что схема была сделана в Mentor-Expedition, поправьте меня, если это не так! Спасибо!

-

А попробуйте посмотреть окно Messages сразу после того, как появится ваше окно с "Differences detecteted". Там наверняка AD укажет на что он ругается.

-

2018 Вопросы начинающих

PCB.Designer ответил Sanchosd тема в Altium Designer, DXP, Protel

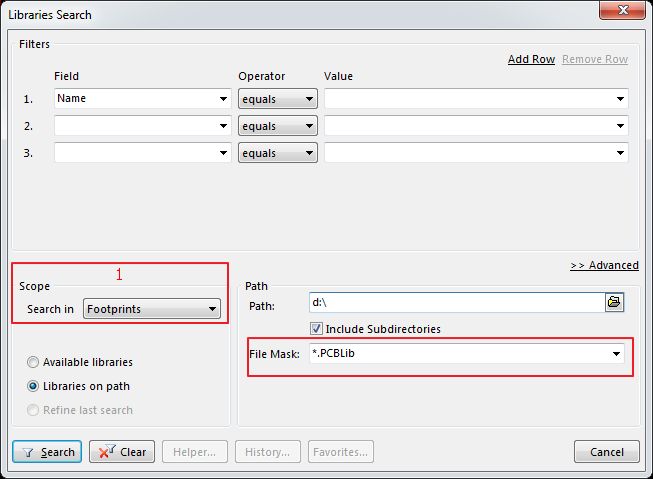

Попробуйте выставить в полях Operator для Name и Footprint одинаковое значение - contains , а в Value использовать поиск с маской * , например *0402*. у меня так находит. А подключены ли у вас библиотеки ? у вас стоит галка Search ... in available Libraries . Проверьте. -

2018 Вопросы начинающих

PCB.Designer ответил Sanchosd тема в Altium Designer, DXP, Protel

Чтобы найти нужный Footprint: 1. установить в поле границ поиска - Footprints. 2. Для быстрого поиска можно задать маску *.PCBLib или *.* -

Сборочный чертеж

PCB.Designer ответил Elena17575751 тема в Altium Designer, DXP, Protel

Можно и не разбивать ничего, указать в PCBFilter строку (Layer = 'TopOverlay') и выделятся все объекты в слое TopOverlay и спокойно переносите через PCB Inspector в другой механический слой. Попробуйте открыть свой DXF в другой программе. Или возможно при экспорте из AD что-то было пропущено. -

В 19-й?

-

Пользовательские параметры не передаются в файл PCBDoc, поэтому в панели PCB List вы их там не увидите, как минимум там будут Component Comment, Footprint , Component Type.

-

-

Владимир, а не подскажете где это правило (как называется) ?