# Приложение: выдержки из даташита на кодек РСМ1808

#### СИНХРОИМПУЛЬСЫ СИСТЕМЫ

PCM1808 поддерживает режимы 256  $f_S$ , 384  $f_S$  и 512  $f_S$  как синхроимпульсы системы, где  $f_S$  - частота выборок. Или, иначе,  $f_S$ =CLK / [256;384;512]

Синхроимпульсы системы должны подаваться на SCKI (вывод 6).

У РСМ1808 есть схема обнаружения синхроимпульсов системы, которая автоматически реагирует, если синхроимпульсы системы работают в режиме  $256f_S$ ,  $384f_S$ , или  $512f_S$  для режима ведомого устройства. В ведущем режиме частотой синхронизации системы нужно управлять через последовательный вход управления, который использует MD1 (вывод 11) и MD0 (вывод 10). Синхроимпульсы системы подаются на автоматический делитель, чтобы сгенерировать частоты  $128f_S$  и  $64f_S$ , которые используются, чтобы управлять цифровым фильтром и сигма-дельта модулятором, соответственно.

В Табл.1 показаны несколько типичных зависимостей между частотой выборок и частотой синхронизации системы, а илл.17 показывает выбор времени синхроимпульсов системы

| Таблица 1. Частота выборок и частот | а синхронизации Системы |

|-------------------------------------|-------------------------|

|-------------------------------------|-------------------------|

| SAMPLING FREQUENCY (kHz) | SYSTEM CLOCK FREQUENCY (fSCLK) ( |                    |  |

|--------------------------|----------------------------------|--------------------|--|

|                          | 256 f <sub>S</sub>               | 384 f <sub>S</sub> |  |

| 8                        | 2.048                            | 3.072              |  |

| 16                       | 4.096                            | 6.144              |  |

| 32                       | 8.192                            | 12.288             |  |

| 44.1                     | 11.2896                          | 16.9344            |  |

| 48                       | 12.288                           | 18.432             |  |

| 64                       | 16.384                           | 24.576             |  |

| 66.2                     | 22.5792                          | 33.8688            |  |

| 96                       | 24.576                           | 36.864             |  |

# ФУНКЦИИ ПЛАВНОГО НАРАСТАНИЯ И ПЛАВНОГО УБЫВАНИЯ СИГНАЛА

У РСМ1808 есть функции плавного нарастания и плавного убывания сигнала на DOUT (вывод 9), что позволяет избежать тресков и помех при работе. Изменения уровня от 0 дБ или приглушение уровня к 0 дБ выполняются, используя вычисления псевдо характеристики S-shaped с обнаружением пересечения нуля.

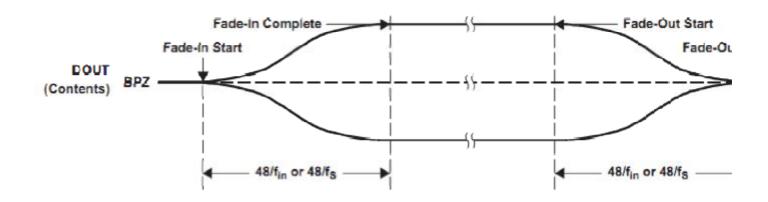

Из-за обнаружения пересечения нуля время, необходимое для плавного нарастания и плавного убывания, зависит от частоты аналогового входного сигнала (fin). Время нарастания или убывания равно 48/f до конца обработки. Если нет никакого пересечения нуля во время  $8192/f_S$ , DOUT усиливается или ослабляется за время  $48/f_S$  (TIME OUT). На Рис. 18 показаны режимы плавного

нарастания и плавного убывания.

Рис.18. Режимы плавного нарастания и плавного убывания сигнала

#### Включение

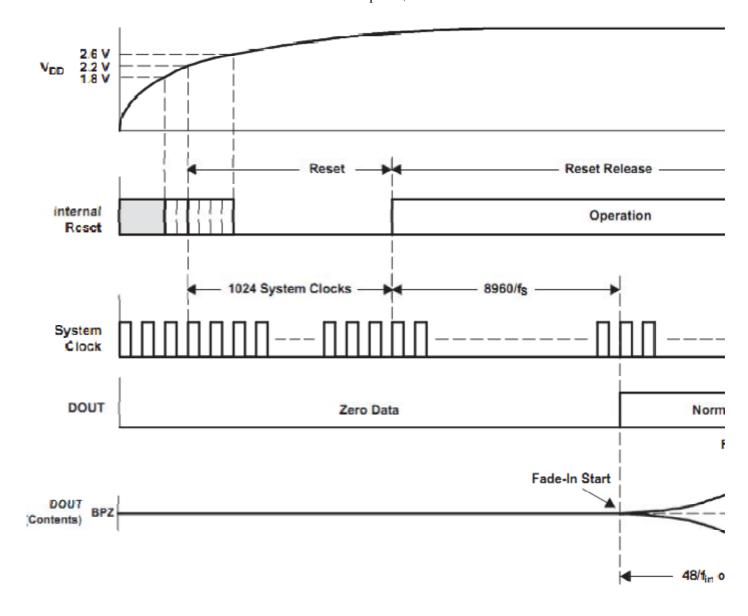

РСМ1808 имеет внутреннюю схему сброса после включения и инициализации, которая срабатывает автоматически при напряжении питания около 2.2 В. Пока  $V_{DD} < 2.2$  В и в течении 1024 циклов системной частоты при  $V_{DD} > 2.2$  В, РСМ1808 находится в состоянии сброса, а цифровой выход в лог.0. Данные на цифровом выходе становятся верными после окончания сброса в течении времени 8960/fs. Так как режим нарастания включается автоматически, данные на цифровом выходе станут соответствовать входному аналоговому сигналу в течение 48/fin или 48/fs. На рис.19 показаны временные характеристики включения.

Рис.19. Временные характеристики включения

Для частоты 18.432 МГц и fS=48 ksps получим: 1024 + (8960/48)/0.05425 + (48/48)/0.05425 = 1024 + 3440 + 18 = 4482 такта CLK. Примерно столько тактов занимает включение кодека.

Не включился... После экспериментов выяснил, что вместо 180 мкс кодек приходит в режим синхронизации 180 мс...

## Функция отключения и сброса при остановке синхроимпульсов

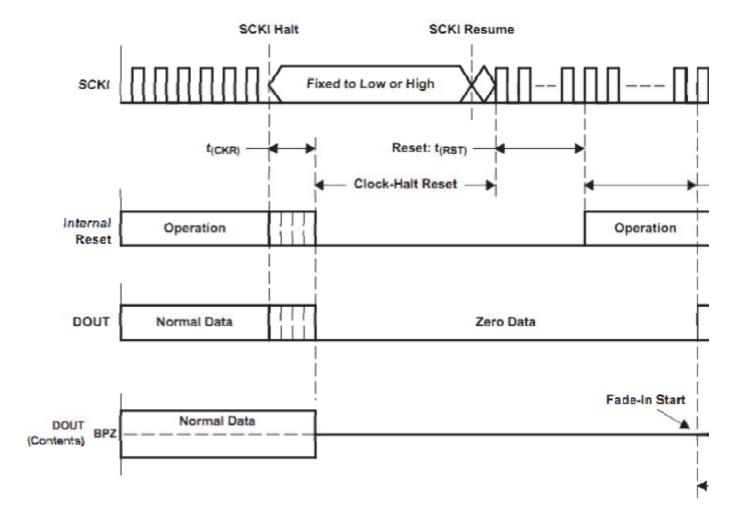

У РСМ1808 есть функция отключения и сброса, которая запускается при остановке SCKI (вывод 6) в режимах ведущего и ведомого устройств. Функция доступна в любое время после включения. Сброс и выключение выполняются автоматически за 4 мкс (минимум) после того, как SCKI остановлен. В то время как происходит сброс по остановке синхроимпульсов и РСМ1808 пребывает в сбросе и режиме отключения, на выводе DOUT (вывод 9) устанавливается уровень лог.0. SCKI должен продолжаться, чтобы закончить режим отключения и сброса. На цифровом выходе устанавливаются действительные данные в течение времени 1024 SCKI + 8960/f<sub>S</sub> после того, как состояние сброса закончено. Поскольку режим плавного нарастания выполняется, он занимает время 48/f<sub>IN</sub> или 48/f<sub>S</sub>, пока не установится уровень, соответствующий уровню аналогового входного сигнала. На Рис. 20 показаны временные характеристики режима сброса

при остановке синхроимпульсов.

Чтобы избежать ухудшения работы ADC, BCK (вывод 8) и LRCK (вывод 7) обязаны синхронизироваться с SCKI в пределах  $4480/f_{\rm S}$  после того, как SCKI возобновляется. Если время синхронизации с SCKI больше, чем  $4480/f_{\rm S}$  для BCK и LRCK, SCKI должен быть маскирован (отключен), пока синхронизация не достигается снова, принимая во внимание глитчи и джиттер. См. на Рис.26 типичную схему соединения.

Чтобы избежать ухудшения работы ADC, сброс по остановке синхроимпульсов также должен быть выполнен, когда на лету изменяется частота синхроимпульса SCKI или сигналов звукового интерфейса BCK и LRCK (значение выборки  $f_S$ ).

| SYMBOL | PARAMETER                                    | MIN | MAX                 |

|--------|----------------------------------------------|-----|---------------------|

| t(CKR) | Delay time from SCKI halt to internal reset  | 4   |                     |

| t(RST) | Delay time from SCKI resume to reset release |     | 1024 SCKI           |

| t(REL) | Delay time from reset release to DOUT output |     | 8960/f <sub>s</sub> |

Рис. 20. Временные характеристики в режиме отключения и сброса

## Последовательный аудио интерфейс

#### Режимы интерфейса

Последовательный аудио интерфейс PCM1808 образуют сигналы LRCK (pin 7), BCK (pin 8), и DOUT (pin 9).

PCM1808 поддерживает режимы Ведущего или Ведомого устройств, которые выбираются MD1 (pin 11) и MD0 (pin 10), как показано в табл.2. MD1 и MD0 должны быть установлены до подачи питания.

В ведущем режиме РСМ1808 обеспечивает временные характеристики передачи данных между РСМ1808 и микропроцессором или внешней схемой. В режиме ведомого устройства РСМ1808 получает сигналы с нужными таймингами для передачи данных от внешнего контроллера.

Таблица 2. Режимы интерфейса

| MD1 (Pin 11) | MD0 (Pin 10) | INTERFACE MODE                                                                          |

|--------------|--------------|-----------------------------------------------------------------------------------------|

| Low          | Low          | Slave mode (256 f <sub>S</sub> , 384 f <sub>S</sub> , 512 f <sub>S</sub> autodetection) |

| Low          | High         | Master mode (512 f <sub>s</sub> )                                                       |

| High         | Low          | Master mode (384 f <sub>S</sub> )                                                       |

| High         | High         | Master mode (256 f <sub>s</sub> )                                                       |

## Формат данных

## Ведущий режим

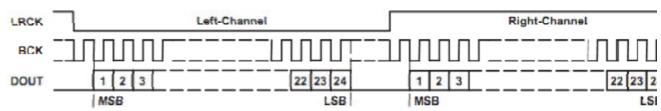

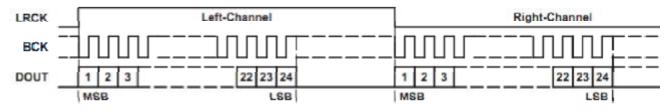

В ведущем режиме BCK и LRCK работают как выходы и управляются от схемы синхронизации PCM1808. Частота BCK устанавливается как 64 BCK/frame.

#### Режим ведомого устройства

В режиме ведомого устройства ВСК и LRCK работают как входы. PCM1808 принимает 64-BCK/frame или 48-BCK/frame формат (только для  $384f_S$ ), но не 32-BCK/frame формат. В данном контексте frame=полный цикл LRCK.

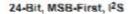

РСМ1808 поддерживает два формата аудио данных и режиме Ведущего и в режиме Ведомого устройств. Формат данных выбирается сигналом FMT (вывод 12), как показано в Табл.3. На Рис.21 показаны форматы данных в режимах Ведомого и Ведущего устройств.

Таблица 3. Формат данных

| FORMAT NO. | FMT (Pin 12) | FORMAT                 |

|------------|--------------|------------------------|

| 0          | Low          | 12S, 24-bit            |

| 1          | High         | Left-justified, 24-bit |

## FORMAT 0: FMT = LOW

#### FORMAT 1: FMT = HIGH

#### 24-Bit, MSB-First, Left-Justified

**Рис.21. Формат аудио данных** (LRCK and BCK работают как входы в Slave Mode и как выходы в Master Mode)

# Синхронизация с микроконтроллером

В режиме ведомого устройства PCM1808 управляется сигналом LRCK (вывод 7), синхронизированным с системной частотой SCKI (вывод 6). PCM1808 не требует определенной зависимости фазы между LRCK и SCKI, но нужна синхронизация LRCK и SCKI.

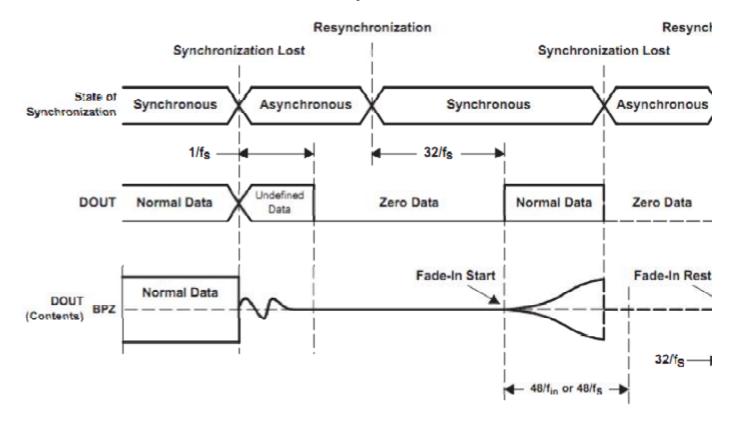

Если зависимость между LRCK и SCKI изменяется больше чем на  $\pm$  6 BCKs для 64 BCK/frame ( $\pm$  5 BCKs для 48 BCK/frame) за время одного периода выборки, из-за джиттера LRCK или SCKI, происходит операция останова ADC в пределах  $1/f_S$  и цифровой выход устанавливается в 0 (код BPZ), до пересинхронизации между LRCK и SCKI.

В случае изменений меньше чем  $\pm 5$  BCKs для 64 BCK/frame ( $\pm 4$  BCKs для 48 BCK/frame), пересинхронизации не происходит и цифровой выход не отключается.

На рис.25 показан отклик цифрового выхода при потере синхронизации и пересинхронизации. В это время выходные данные не определенны и PCM1808 может произвести некоторый шум в аудио сигнале. Кроме того, переход от нормальных данных к неопределенным создает цифровой шум в аудио сигнале. Цифровой выход действителен после пересинхронизации в течении 32/f<sub>S</sub>. Поскольку выполняется режим плавного нарастания, он занимает время 48/f<sub>IN</sub> или 48/f<sub>S</sub>, пока не будет достигнут уровень, соответствующий сигналу аналогового входного сигнала. Если синхронизация теряется во время режима плавного нарастания или плавного убывания, включается режим остановки и на DOUT (вывод 9) немедленно устанавливается лог.0. Режим плавного нарастания возобновляется после пересинхронизации за время 32/f.

Рис.25. Поведение цифрового выхода ADC во время потери синхронизации и пересинхронизации

#### Дизайн платы и размещение деталей

Линии цифрового и аналогового питания PCM1808 блокируются керамическимм конденсаторами 100 нф и электролитическими конденсаторами 10 мкф для достижения максимальных динамических характеристик АЦП.

#### Выволы AGND и DGND

Для достижения максимальных динамических характеристик АЦП аналоговая и цифровая земли не имеют внугреннего соединения. Эти земли должны иметь низкий импеданс, чтобы цифровой шум не попал в аналоговую землю.

Чтобы избежать проблем с шумами, эти земли должны быть соединены друг с другом под корпусом РСМ1808

## Выводы $V_{IN}L$ и $V_{IN}R$

Входы  $V_{IN}L$  и  $V_{IN}R$  являются самодостаточными. Это значит, что в них интегрированы антиалиасинговые ФНЧ, которые отсекают ВЧ-составляющие и шумы от аудио-диапазона. Если параметры этих фильтров недостаточны для реализованной схемы, то можно добавить внешние пассивные RC фильтры (например, от R=100 и C=10 нф до R=1K и C=1 нф).