# PCI Express™ Logic Analyzer Probing Design Guide for Agilent Technologies

Design Guide

| Table of Contents                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview and Configuration Support 2 Link configuration support                                                                                            |

| Mechanical Design3Midbus LAI3Reference clock6                                                                                                              |

| Electrical Design       .7         Midbus LAI       .7         Full-size midbus pin assignment       .12         Half-size midbus pin assignment       .16 |

| Reference Clock 21                                                                                                                                         |

| Appendix A                                                                                                                                                 |

| Appendix B                                                                                                                                                 |

| Support, Services, and Assistance27                                                                                                                        |

### **Objectives**

This document is intended to provide Agilent Technologies customers with insight into the information needed by platform and system design teams for integration of Logic Analyzer Probing for PCI Express™ into their designs. In its complete form, this information provides system designers a mechanical and electrical solution space for Logic Analyzer Interface (LAI) placement for the PCI Express bus. The solutions given here only concern a midbus probing solution in which the LAI footprint is designed into the target system. Agilent provides a low intrusion interposer/extender to support slot connectors on the PCI Express bus.

Although information concerning PCI Express topology and specifications will be given, this document is not intended to take the place of other PCI Express design documentation. It is assumed that a design team utilizing this document for their

design constraints will validate their designs through pre and post route electrical simulation and keepout volume analysis.

To enable proper consideration to the numerous design parameters, a layout/schematic checklist has been developed and is included as an appendix in this document.

### **Nomenclature**

- LAI refers to the analysis probe or Agilent N4220B

- Midbus connection, midbus probe, midbus LAI and midbus footprint refer to the LAI footprint connector or the Agilent N4221A PCI Express compression cable set.

1/2 midbus connection,

1/2 midbus probe, 1/2 midbus

LAI and 8 channel PCI Express

LAI pinout midbus footprint

refer to the LAI footprint

connector or the Agilent

N4228A PCI Express

compression cable set.

### **Overview and Configuration Support**

### **Link configuration support**

A PCI Express LAI provides support for a 16 channel midbus direct probing solution. For the purposes of this document, "channel" refers to either an upstream differential pair OR downstream differential pair for a given lane. A corollary statement is that "channel" refers to either a transmit differential pair OR receive differential pair for a given lane. Flexibility is given to the platform designer to configure a probing solution that best meets the needs of the system. With this 16 channel solution, the following configurations may be made\*:

- Upstream *and* downstream channels of one x8 link

- Upstream *and* downstream channels of up to two x4, x2, or x1 links

- Upstream *or* downstream channels of one x16 link

- Upstream *or* downstream channels of up to four x4, x2, or x1 links

- Other combinations may be available. Contact Agilent Technologies for the latest support configurations.

- As long as the LAI placement within the system requirements are met (see "LAI placement within system topology," page 7). System designers should verify that their system requirements are supported by the LA vendors by contacting Agilent Technologies directly.

### Reference clock(s) to LAI

Each system must provide means of delivering a reference clock (for each PCI Express reference clock domain) for specific cases:

- When an LAI is used with a system that supports Spread Spectrum Clocking (SSC) on the reference clock to all the PCI Express agents and the SSC can not be disabled

- When testing must be done with SSC enabled because a problem does not manifest with SSC disabled

- If the link frequency is intentionally margin tested outside the standard ±300 ppm tolerance.

- If any clock domain reference clock operates outside a ±150 ppm tolerance (note that this is more restrictive than the PCI Express standard of ±300 ppm, but must be considered). For more information, contact Agilent Technologies directly.

Note that this clock can be a dedicated clock, in which case appropriate terminators must be provided on the board.

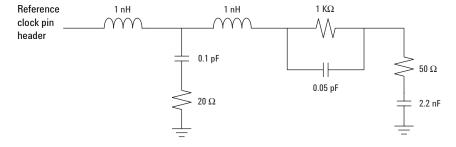

Alternately, the signals may be a tap off an existing clock, since the probes are designed to not significantly load the signals. However, this needs to be verified by the system platform designers to verify proper functionality. See reference clock model (Figure 11) for more information.

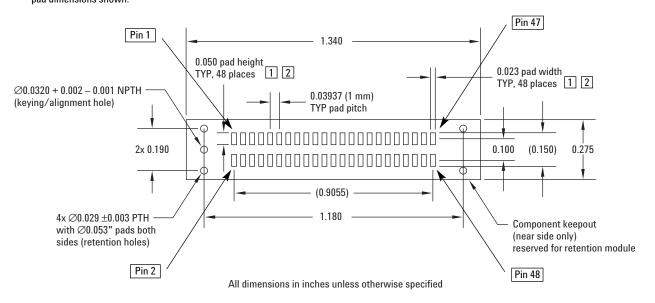

### Midbus LAI

This section contains mechanical design details (footprint dimensions, keepout volumes, and part numbers) of the midbus LAI and the reference clock pin header.

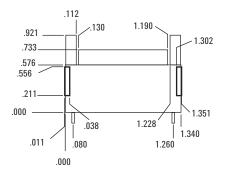

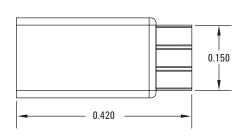

### N4221A – Footprint dimensions and specifications

#### Notes:

- 1 Must maintain a soldermask web between pads when traces are routed between the pads on the same layer. However, soldermask may not encroach onto the pads within the pad dimensions shown.

- 2 Via-in-pad not allowed on these pads. However, via edges may be tangent to the pad edges.

- 3 Permissable surface finishes on pads are HASL, immersion silver, or gold over nickel.

Figure 1. PCI Express LAI footprint dimensions, pin numbering, and specification

### Retention Modules:

A kit of 5 RMs are supplied with each N4221A, N4222A, and N4228A probes.

Additional kits for N4221A and N4222A can be ordered by using Agilent part number N4221-68702 (PI:600-0117-00).

Additional kits for N4228A can be ordered by using Agilent part number N4228-68702 (PI:600-0139-00)

For larger quantities, please contact Precision Interconnect at: 10025 SW Freeman Ct., Wilsonville, OK 97070 (503-685-9300) http://www.precisionint.com

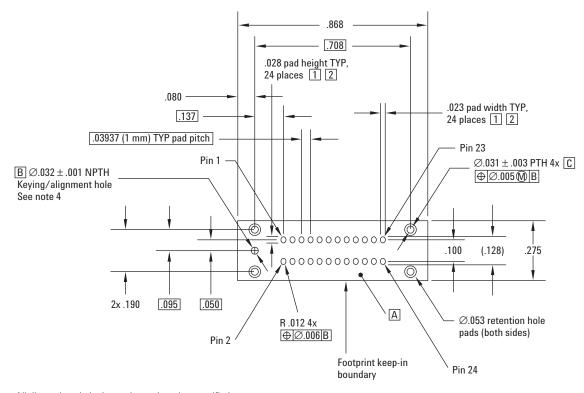

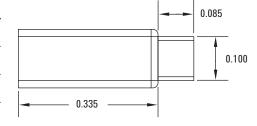

### Midbus LAI

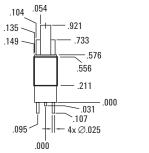

### $N4228A - \frac{1}{2}$ size midbus footprint dimensions and specifications

#### Notes:

- Must maintain a soldermask web between pads when traces are routed between the pads on the same layer. However, soldermask may not encroach onto the pads within the pad dimensions shown.

- 2 Via-in-pad not allowed on these pads. However, via edges may be tangent to the pad edges.

- Permissable surface finishes on pads are HASL, immersion Silver, or Gold over Nickel.

All dimensions in inches unless otherwise specified

Figure 2.

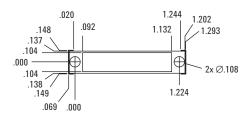

### Midbus LAI

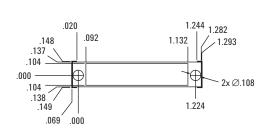

### N4221A – Keepout volume

Coax cable egress

Retention clip

Retention clip

104 .054

Figure 3. PCI Express LAI keepout volume

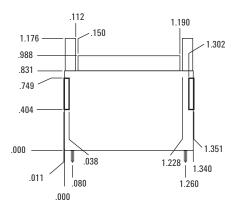

### $N4228A - \frac{1}{2}$ size midbus keepout volume

Retention screws

Retention clip

.104

.054

.138

.149

.988

.831

.749

.404

.000

.000

.001

.007

.000

Figure 4.

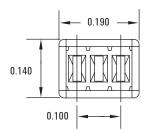

### Reference clock

#### Reference clock header

A 3-pin header (1 by 3, 0.05 inch center spacing) will provide the connection for reference clock to the LAI. A small high impedance clock probe from the LAI will connect to this header to the LAI. Note that an individual reference clock header is required for *each* PCI Express clock domain on the system.

The following are recommended part numbers for through-hole and surface mount versions of the 3-pin header for reference clock:

- Through-hole: Samtec\* TMS-103-02-S-S

- Surface mount: Samtec\* FTR-103-02-S-S

| Signal     | Pin Number            |

|------------|-----------------------|

| REFCLKp    | 1 (or 3) <sup>1</sup> |

| GND or N/C | 2                     |

| REFCLKn    | 3 (or 1) <sup>1</sup> |

<sup>1</sup> The LAI is not sensitive to the polarity of the reference clock. Therefore, the probe can be plugged onto the pin header in either orientation.

Table 1. Reference clock header pinout

# LAI reference clock probe keepout volume

Keepout volumes for the reference clock probes are given in Figure 5. The pin headers reside symmetrically within the keepout volume on the target system. For more specific information on keepout volumes for particular solutions please contact Agilent Technologies.

Figure 5. PCI Express reference clock probe keepout volume

### Midbus LAI

This section contains electrical design details of the midbus LAI and the reference clock pin header. These details include LAI eye requirement definition, system impact due to LAI probe presence, LAI routing suggestions, load models, and pin assignments.

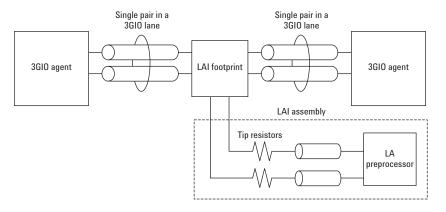

Logical probing of the PCI Express bus is achieved through tapping a small amount of energy off the probed signals and channeling this energy to the logic analyzer. In order to avoid excessive loading conditions, the use of tip resistors, or isolation resistors, is employed. These relatively high impedance tip resistors enable the logic analyzer to sample bus traffic without significantly loading the probed signals. A high-level block diagram of a generic PCI Express bus with a logic analyzer interface is given in Figure 6. Note that this would be repeated for each differential pair within a PCI Express link.

# LAI placement within system topology

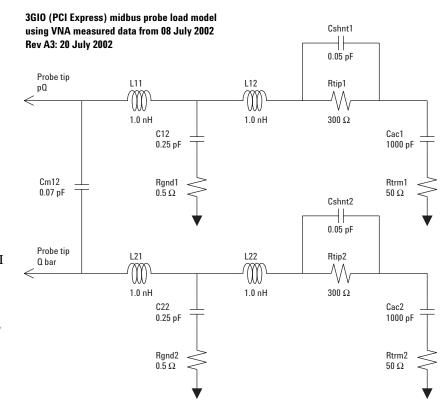

In order for the LA to reliably capture logical transactions on the bus, adequate signal eye must be made available to the LAI. It is incumbent upon the platform designers to ensure that sufficient signal eye is available to the LAI while the LAI load is in place so that proper signal tracing is enabled. This must be verified via electrical simulation utilizing the load model provided in Figure 10.

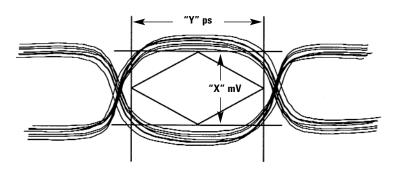

The eye requirements are measured by eye height and eye width, forming a diamond shape. These requirements are described pictorially in Figure 7.

Figure 6. Block diagram example of a generic PCI Express bus with a LAI

Figure 7. Example of eye specifications as seen at the LAI pad

### Midbus LAI

Table 2 details the specific eye requirements for Agilent Technologies. Address questions to Agilent Technologies for the most current eye requirements.

The eye characteristics given in Table 2 must be maintained for all probed links, regardless of direction. Overall, these LAI placement specifications limit the electrical distance between the driver pin and the LAI attach point. Conceivably, probing both directions in lanes of a long PCI Express link may require two separate footprints and LAI assemblies, while probing both directions of relatively short links may be accomplished with one LAI. Regardless of implementation, refer to usage restrictions as listed in the "Overview and Configuration Support" section. The same LAI eye requirements exist for all links substrates (e.g. FR4, cables, etc.).

An additional constraint on LAI footprint placement involves the relative location of the AC coupling capacitors. The capacitors may be placed either between the driver and LAI, or between the LAI and receiver, as long as both capacitors of a differential pair are placed in the same fashion. Other pairs within a link do not need to maintain this capacitor placement configuration.

### **Agilent Technologies Specification**

| Min eye height at LAI pad <sup>1</sup>                         | 175 mV                                                                    |

|----------------------------------------------------------------|---------------------------------------------------------------------------|

| Min eye width at LAI pad                                       | 0.35 UI (140 ps at midbus footprint),<br>i.e. Jitter tolerance of 0.65 UI |

| Length matching requirements - differential pairs <sup>2</sup> | ±5 mil                                                                    |

| Length matching requirements - pair to pair                    | none                                                                      |

Measured in differential units, e.g.  $Vdiff = |2^*(Vp - Vn)|$

Table 2. PCI Express LAI footprint placement interconnect specification

<sup>2</sup> Interconnect must length match ±5 mils from source to LAI footprint pad for each polarity of the differential pair.

### Midbus LAI

# Impact on PCI Express channel due to probe presence

Agilent will provide detailed information on impact as soon as detailed, measured information is available.

### Routing considerations near/through PCI Express LAI footprint

Agilent will provide detailed information on routing and design considerations at a later date.

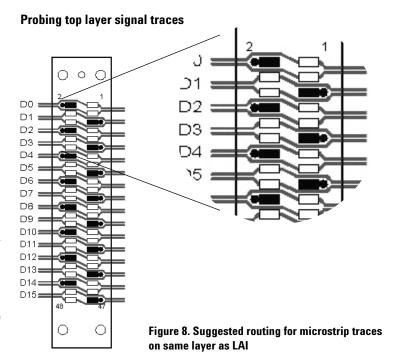

Figure 8 presents suggested routing for footprint negotiation in the case of surface (microstrip) routing when this routing is on the same side of board as LAI.

#

- □ Signal Pads

- Ground Pads

- Top Layer Traces

- Bottom / Inner Layer Traces

### Midbus LAI

### **Load Models**

### Agilent Technologies\* Load Model

The Agilent Technologies load model for the midbus LAI is given in Figure 10. This model is subject to change. For the most current models, it is recommended that the platform designer contact Agilent Technologies directly.

### Load model without LAI installed

The model of the parasitic load on the system due to the LAI midbus footprint only (i.e. no LAI installed) is represented simply by a 0.2 pF capacitor to ground. Note that if vias are associated with tapping the link for the LAI, those via parasitics would also need to be considered here in addition to the 0.2 pF pad load.

Figure 10. Load model for LAI

### Midbus LAI

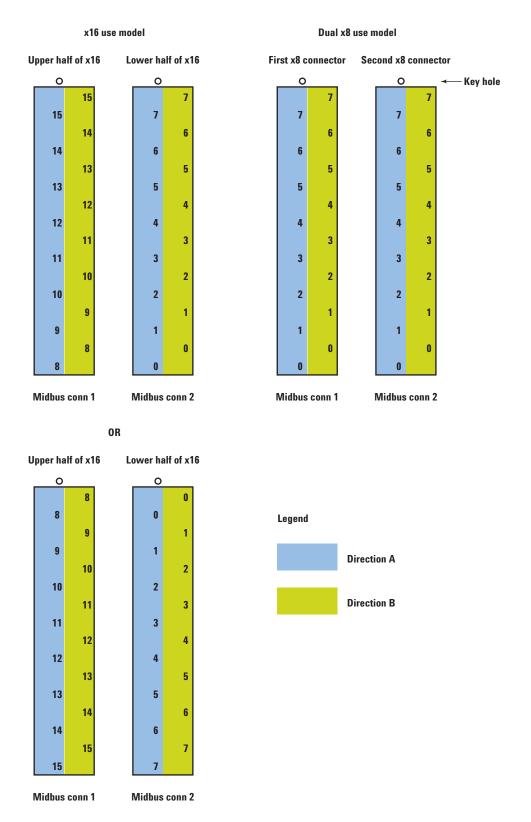

### **PCI Express LAI pin assignments**

There is flexibility in the arrangement and layout of the midbus footprint. Agilent will provide configuration of the LAI to support the following midbus layouts. There is a detailed view of these connections below. Appendix B also contains a high level depiction of the same midbus footprint.

The pinout for the PCI Express LAI is given in "Full-size midbus pin assignment, General PCI Express LAI pinout," Table 3. It is imperative that designers understand there is some freedom associated with the pin/signal assignment relationship. These notes are given here:

| Footprint channel vs. lane/link designations | Channel = either an upstream OR downstream differential pair for a given lane                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                              | C <letter> = the designator for a Channel which accepts a given differential pair of signals</letter>                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                              | C <letter> = the two signals of the differential pair. The signals within a given pair may be assigned to either x or y regardless of polarity</letter>                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| General rules for<br>signal pair assignment  | The differential pairs that make up the PCI Express links must be assigned to specific pins of the footprint. However, there is some freedom in this pair assignment in order to minimize routing constraints on the platform. Additionally, note that the channel to footprint assignment configuration is closely related to the "direction" of the probed link. More specifically, a bi-directional pin assignment is different from a unidirectional pin assignment. See the following tables contained in this section for more information. |  |  |

# Full-size midbus pin assignment

### **General PCI Express LAI pinout**

| Pin# | Signal Name | Pin# | Signal Name |

|------|-------------|------|-------------|

| 2    | GND         | 1    | САр         |

| 4    | СВр         | 3    | CAn         |

| 6    | CBn         | 5    | GND         |

| 8    | GND         | 7    | ССр         |

| 10   | CDp         | 9    | CCn         |

| 12   | CDn         | 11   | GND         |

| 14   | GND         | 13   | СЕр         |

| 16   | CFp         | 15   | CEn         |

| 18   | CFn         | 17   | GND         |

| 20   | GND         | 19   | CGp         |

| 22   | СНр         | 21   | CGn         |

| 24   | CHn         | 23   | GND         |

| 26   | GND         | 25   | Clp         |

| 28   | CJp         | 27   | Cln         |

| 30   | CJn         | 29   | GND         |

| 32   | GND         | 31   | СКр         |

| 34   | CLp         | 33   | CKn         |

| 36   | CLn         | 35   | GND         |

| 38   | GND         | 37   | СМр         |

| 40   | CNp         | 39   | CMn         |

| 42   | CNn         | 41   | GND         |

| 44   | GND         | 43   | СРр         |

| 46   | СОр         | 45   | CPn         |

| 48   | CQn         | 47   | GND         |

|      |             |      |             |

Table 3.

### x16 (standard) PCI Express LAI pinout<sup>1, 2, 3</sup>

| Pin # | Signal Name | Pin# | Signal Name |

|-------|-------------|------|-------------|

| 2     | GND         | 1    | СОр         |

| 4     | C1p         | 3    | C0n         |

| 6     | C1n         | 5    | GND         |

| 8     | GND         | 7    | C2p         |

| 10    | СЗр         | 9    | C2n         |

| 12    | C3n         | 11   | GND         |

| 14    | GND         | 13   | C4p         |

| 16    | С5р         | 15   | C4n         |

| 18    | C5n         | 17   | GND         |

| 20    | GND         | 19   | С6р         |

| 22    | С7р         | 21   | C6n         |

| 24    | C7n         | 23   | GND         |

| 26    | GND         | 25   | С8р         |

| 28    | С9р         | 27   | C8n         |

| 30    | C9n         | 29   | GND         |

| 32    | GND         | 31   | C10p        |

| 34    | C11p        | 33   | C10n        |

| 36    | C11n        | 35   | GND         |

| 38    | GND         | 37   | C12p        |

| 40    | C13p        | 39   | C12n        |

| 42    | C13n        | 41   | GND         |

| 44    | GND         | 43   | C14p        |

| 46    | C15p        | 45   | C14n        |

| 48    | C15n        | 47   | GND         |

|       |             |      |             |

<sup>1</sup> Polarity (p and n) of each differential pair may be swapped.

Table 4.

<sup>2</sup> This configuration can only probe either upstream 16 channels OR 16 downstream channels with one LAI. Please see Table 5 for a configuration that supports interleaved x16 traffic amongst two LAI footprints.

<sup>3</sup> Entire link assignment may be reversed in LAI. For example, channel 0 may be swapped in above table with channel 15, channel 1 with channel 14, etc. If swapping upstream, must also swap downstream (and vice versa).

# Full-size midbus pin assignment

### x16 (split) specific PCI Express LAI pinout<sup>1, 2, 3, 4</sup>

### Midbus connector 1

### Midbus connector 2

| Pin# | Signal Name      | Pin# | Signal Name    | Pin# | Signal Name     | Pin# | Signal Name   |

|------|------------------|------|----------------|------|-----------------|------|---------------|

| 2    | GND              | 1    | C8p- Upstream  | 2    | GND             | 1    | C0p- Upstream |

| 4    | C8p- Downstream  | 3    | C8n- Upstream  | 4    | C0p- Downstream | 3    | C0n- Upstream |

| 6    | C8n- Downstream  | 5    | GND            | 6    | C0n- Downstream | 5    | GND           |

| 8    | GND              | 7    | C9p- Upstream  | 8    | GND             | 7    | C1p- Upstream |

| 10   | C9p- Downstream  | 9    | C9n- Upstream  | 10   | C1p- Downstream | 9    | C1n- Upstream |

| 12   | C9n- Downstream  | 11   | GND            | 12   | C1n- Downstream | 11   | GND           |

| 14   | GND              | 13   | C10p- Upstream | 14   | GND             | 13   | C2p- Upstream |

| 16   | C10p- Downstream | 15   | C10n- Upstream | 16   | C2p- Downstream | 15   | C2n- Upstream |

| 18   | C10n- Downstream | 17   | GND            | 18   | C2n- Downstream | 17   | GND           |

| 20   | GND              | 19   | C11p- Upstream | 20   | GND             | 19   | C3p- Upstream |

| 22   | C11p- Downstream | 21   | C11n- Upstream | 22   | C3p- Downstream | 21   | C3n- Upstream |

| 24   | C11n- Downstream | 23   | GND            | 24   | C3n- Downstream | 23   | GND           |

| 26   | GND              | 25   | C12p- Upstream | 26   | GND             | 25   | C4p- Upstream |

| 28   | C12p- Downstream | 27   | C12n- Upstream | 28   | C4p- Downstream | 27   | C4n- Upstream |

| 30   | C12n- Downstream | 29   | GND            | 30   | C4n- Downstream | 29   | GND           |

| 32   | GND              | 31   | C13p- Upstream | 32   | GND             | 31   | C5p- Upstream |

| 34   | C13p- Downstream | 33   | C13n- Upstream | 34   | C5p- Downstream | 33   | C5n- Upstream |

| 36   | C13n- Downstream | 35   | GND            | 36   | C5n- Downstream | 35   | GND           |

| 38   | GND              | 37   | C14p- Upstream | 38   | GND             | 37   | C6p- Upstream |

| 40   | C14p- Downstream | 39   | C14n- Upstream | 40   | C6p- Downstream | 39   | C6n- Upstream |

| 42   | C14n- Downstream | 41   | GND            | 42   | C6n- Downstream | 41   | GND           |

| 44   | GND              | 43   | C15p- Upstream | 44   | GND             | 43   | C7p- Upstream |

| 46   | C15p- Downstream | 45   | C15n- Upstream | 46   | C7p- Downstream | 45   | C7n- Upstream |

| 48   | C15n- Downstream | 47   | GND            | 48   | C7n- Downstream | 47   | GND           |

<sup>1</sup> Polarity (p and n) of each differential pair may be swapped.

### Table 5.

<sup>2</sup> Entire link assignment may be reversed in LAI. For example, channel 0-upstream may be swapped in above table with channel 7-upstream, channel 1-upstream with channel 6-upstream, etc. If swapping upstream, must also swap downstream (and vice versa).

<sup>3</sup> Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc.

Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

# Full-size midbus pin assignment

### x8 (bi-directional ) specific PCI Express LAI pinout<sup>1, 2, 3, 4</sup>

| Pin# | Signal Name     | Pin# | Signal Name   |

|------|-----------------|------|---------------|

| 2    | GND             | 1    | C0p- Upstream |

| 4    | C0p- Downstream | 3    | C0n- Upstream |

| 6    | C0n- Downstream | 5    | GND           |

| 8    | GND             | 7    | C1p- Upstream |

| 10   | C1p- Downstream | 9    | C1n- Upstream |

| 12   | C1n- Downstream | 11   | GND           |

| 14   | GND             | 13   | C2p- Upstream |

| 16   | C2p- Downstream | 15   | C2n- Upstream |

| 18   | C2n- Downstream | 17   | GND           |

| 20   | GND             | 19   | C3p- Upstream |

| 22   | C3p- Downstream | 21   | C3n- Upstream |

| 24   | C3n- Downstream | 23   | GND           |

| 26   | GND             | 25   | C4p- Upstream |

| 28   | C4p- Downstream | 27   | C4n- Upstream |

| 30   | C4n- Downstream | 29   | GND           |

| 32   | GND             | 31   | C5p- Upstream |

| 34   | C5p- Downstream | 33   | C5n- Upstream |

| 36   | C5n- Downstream | 35   | GND           |

| 38   | GND             | 37   | C6p- Upstream |

| 40   | C6p- Downstream | 39   | C6n- Upstream |

| 42   | C6n- Downstream | 41   | GND           |

| 44   | GND             | 43   | C7p- Upstream |

| 46   | C7p- Downstream | 45   | C7n- Upstream |

| 48   | C7n- Downstream | 47   | GND           |

|      |                 |      |               |

- 1 Polarity (p and n) of each differential pair may be swapped.

- 2 Can probe upstream 8 channels AND downstream 8 channels with one LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-upstream may be swapped in above table with channel 7-upstream, channel 1-upstream with channel 6-upstream, etc. If swapping upstream, must also swap downstream (and vice versa)

- Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

Table 6.

Dual x4 (bi-directional) specific PCI Express LAI pinout<sup>1, 2, 3, 4,5</sup>

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | C0p- Upstream1 |

| 4    | C0p- Downstream1 | 3    | C0n- Upstream1 |

| 6    | C0n- Downstream1 | 5    | GND            |

| 8    | GND              | 7    | C1p- Upstream1 |

| 10   | C1p- Downstream1 | 9    | C1n- Upstream1 |

| 12   | C1n- Downstream1 | 11   | GND            |

| 14   | GND              | 13   | C2p- Upstream1 |

| 16   | C2p- Downstream1 | 15   | C2n- Upstream1 |

| 18   | C2n- Downstream1 | 17   | GND            |

| 20   | GND              | 19   | C3p- Upstream1 |

| 22   | C3p- Downstream1 | 21   | C3n- Upstream1 |

| 24   | C3n- Downstream1 | 23   | GND            |

| 26   | GND              | 25   | C0p- Upstream2 |

| 28   | C0p- Downstream2 | 27   | C0n- Upstream2 |

| 30   | C0n- Downstream2 | 29   | GND            |

| 32   | GND              | 31   | C1p- Upstream2 |

| 34   | C1p- Downstream2 | 33   | C1n- Upstream2 |

| 36   | C1n- Downstream2 | 35   | GND            |

| 38   | GND              | 37   | C2p- Upstream2 |

| 40   | C2p- Downstream2 | 39   | C2n- Upstream2 |

| 42   | C2n- Downstream2 | 41   | GND            |

| 44   | GND              | 43   | C3p- Upstream2 |

| 46   | C3p- Downstream2 | 45   | C3n- Upstream2 |

| 48   | C3n- Downstream2 | 47   | GND            |

|      |                  |      |                |

- 1 Polarity (p and n) of the differential pair may be swapped.

- 2 Can probe upstream 4 channels AND downstream 4 channels of TWO x4 links with one LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-upstream1 may be swapped in above table with channel 3-upstream, channel 1-upstream with channel 2-upstream, etc. If swapping upstream, must also swap downstream (and vice versa).

- 4 Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

- 5 Single link configuration also supported.

### Table 7.

### Full-size midbus pin assignment

# Dual x2 (bi-directional) specific PCI Express LAI pinout<sup>1, 2, 3, 4, 5</sup>

| Signal Name      | Pin#                                                                                                                                                                                                                                                                                                             | Signal Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND              | 1                                                                                                                                                                                                                                                                                                                | C0p- Upstream1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C0p- Downstream1 | 3                                                                                                                                                                                                                                                                                                                | C0n- Upstream1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C0n- Downstream1 | 5                                                                                                                                                                                                                                                                                                                | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 7                                                                                                                                                                                                                                                                                                                | C1p- Upstream1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C1p- Downstream1 | 9                                                                                                                                                                                                                                                                                                                | C1n- Upstream1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C1n- Downstream1 | 11                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 13                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 15                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 17                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 19                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 21                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 23                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 25                                                                                                                                                                                                                                                                                                               | C0p- Upstream2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C0p- Downstream2 | 27                                                                                                                                                                                                                                                                                                               | C0n- Upstream2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C0n- Downstream2 | 29                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 31                                                                                                                                                                                                                                                                                                               | C1p- Upstream2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C1p- Downstream2 | 33                                                                                                                                                                                                                                                                                                               | C1n- Upstream2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C1n- Downstream2 | 35                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 37                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 39                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 41                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND              | 43                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 45                                                                                                                                                                                                                                                                                                               | nc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nc               | 47                                                                                                                                                                                                                                                                                                               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | GND  COp- Downstream1  COn- Downstream1  GND  C1p- Downstream1  C1n- Downstream1  GND  nc  nc  GND  nc  GND  COp- Downstream2  COn- Downstream2  GND  C1p- Downstream2 | GND       1         COp- Downstream1       3         COn- Downstream1       5         GND       7         C1p- Downstream1       9         C1n- Downstream1       11         GND       13         nc       15         nc       17         GND       19         nc       21         nc       23         GND       25         C0p- Downstream2       27         C0n- Downstream2       29         GND       31         C1p- Downstream2       33         C1n- Downstream2       35         GND       37         nc       39         nc       41         GND       43         nc       45 |

- 1 Polarity (p and n) of the differential pair may be swapped.

- 2 Can probe upstream 2 channels AND downstream 2 channels of two x2 links with one LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-upstream1 may be swapped in above table with channel 1-upstream, etc. If swapping upstream, must also swap downstream (and vice versa).

- 4 Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

- 5 Single link configuration also supported.

Table 8.

# Dual x1 (bi-directional) specific PCI Express LAI pinout<sup>1, 2, 3, 4</sup>

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | C0p- Upstream1 |

| 4    | C0p- Downstream1 | 3    | C0n- Upstream1 |

| 6    | C0n- Downstream1 | 5    | GND            |

| 8    | GND              | 7    | nc             |

| 10   | nc               | 9    | nc             |

| 12   | nc               | 11   | GND            |

| 14   | GND              | 13   | nc             |

| 16   | nc               | 15   | nc             |

| 18   | nc               | 17   | GND            |

| 20   | GND              | 19   | nc             |

| 22   | nc               | 21   | nc             |

| 24   | nc               | 23   | GND            |

| 26   | GND              | 25   | C0p- Upstream2 |

| 28   | C0p- Downstream2 | 27   | C0n- Upstream2 |

| 30   | C0n- Downstream2 | 29   | GND            |

| 32   | GND              | 31   | nc             |

| 34   | nc               | 33   | nc             |

| 36   | Nc               | 35   | GND            |

| 38   | GND              | 37   | nc             |

| 40   | Nc               | 39   | nc             |

| 42   | nc               | 41   | GND            |

| 44   | GND              | 43   | nc             |

| 46   | nc               | 45   | nc             |

| 48   | Nc               | 47   | GND            |

- 1 Polarity (p and n) of the differential pair may be swapped.

- 2 Can probe upstream 1 channel AND 1 downstream channel of two x1 links with one LAL

- 3 Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream.

- 4 Single link configuration also supported.

### Table 9.

# Half-size midbus pin assignment

### **General 8 channel PCI Express pinout**

| Pin# | Signal Name | Pin# | Signal Name |

|------|-------------|------|-------------|

| 2    | GND         | 1    | САр         |

| 4    | СВр         | 3    | CAn         |

| 6    | CBn         | 5    | GND         |

| 8    | GND         | 7    | ССр         |

| 10   | CDp         | 9    | CCn         |

| 12   | CDn         | 11   | GND         |

| 14   | GND         | 13   | СЕр         |

| 16   | CFp         | 15   | CEn         |

| 18   | CFn         | 17   | GND         |

| 20   | GND         | 19   | CGp         |

| 22   | СНр         | 21   | CGn         |

| 24   | CHn         | 23   | GND         |

|      | •           |      |             |

Table 10.

# x8 (unidirectional) specific 8 channel PCI Express LAI pinout $^{1,\,2,\,3}$

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | C0p- DirectionA |

| 4    | C1p- DirectionA | 3    | C0n- DirectionA |

| 6    | C1n- DirectionA | 5    | GND             |

| 8    | GND             | 7    | C2p- DirectionA |

| 10   | C3p- DirectionA | 9    | C2n- DirectionA |

| 12   | C3n- DirectionA | 11   | GND             |

| 14   | GND             | 13   | C4p- DirectionA |

| 16   | C5p- DirectionA | 15   | C4n- DirectionA |

| 18   | C5n- DirectionA | 17   | GND             |

| 20   | GND             | 19   | C6p- DirectionA |

| 22   | C7p- DirectionA | 21   | C6n- DirectionA |

| 24   | C7n- DirectionA | 23   | GND             |

|      |                 |      |                 |

Polarity (p and n) of each differential pair may be swapped.

Can probe DirectionA 8 channels with one 8-channel LAI.

Table 11.

<sup>3</sup> Entire link assignment may be reversed in LAI. For example, channel 0-DirectionA may be swapped in above table with channel 7-DirectionA, channel 1-DirectionA with channel 6-DirectionA, etc.

### Half-size midbus pin assignment

# x4 (bi-directional) specific 8 channel PCI Express LAI pinout<sup>1, 2, 3, 4</sup>

| Pin# | Signal Name     | Pin# | Signal Name   |

|------|-----------------|------|---------------|

| 2    | GND             | 1    | COp- Upstream |

| 4    | C0p- Downstream | 3    | COn- Upstream |

| 6    | C0n- Downstream | 5    | GND           |

| 8    | GND             | 7    | C1p- Upstream |

| 10   | C1p- Downstream | 9    | C1n- Upstream |

| 12   | C1n- Downstream | 11   | GND           |

| 14   | GND             | 13   | C2p- Upstream |

| 16   | C2p- Downstream | 15   | C2n- Upstream |

| 18   | C2n- Downstream | 17   | GND           |

| 20   | GND             | 19   | C3p- Upstream |

| 22   | C3p- Downstream | 21   | C3n- Upstream |

| 24   | C3n- Downstream | 23   | GND           |

- 1 Polarity (p and n) of the differential pair may be swapped.

- 2 Can probe Upstream 4 channels AND Downstream 4 channels of ONE x4 link with one 8 channel LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-upstream may be swapped in above table with channel 3-upstream, channel 1-upstream with channel 2-upstream, etc.

- 4 Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

Table 12.

# x4 (2 unidirectional) specific 8 channel PCI Express LAI pinout<sup>1, 2, 3</sup>

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | C0p- DirectionA |

| 4    | C0p- DirectionB | 3    | C0n- DirectionA |

| 6    | C0n- DirectionB | 5    | GND             |

| 8    | GND             | 7    | C1p- DirectionA |

| 10   | C1p- DirectionB | 9    | C1n- DirectionA |

| 12   | C1n- DirectionB | 11   | GND             |

| 14   | GND             | 13   | C2p- DirectionA |

| 16   | C2p- DirectionB | 15   | C2n- DirectionA |

| 18   | C2n- DirectionB | 17   | GND             |

| 20   | GND             | 19   | C3p- DirectionA |

| 22   | C3p- DirectionB | 21   | C3n- DirectionA |

| 24   | C3n- DirectionB | 23   | GND             |

- 1 Polarity (p and n) of the differential pair may be swapped.

- 2 Can probe DirectionA 4 channels and DirectionB 4 channels with one 8 channel LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-DirectionA may be swapped in above table with channel 3-DirectionA, channel 1-DirectionA with channel 2-DirectionA, etc.

Table 13.

### Half-size midbus pin assignment

# x2 (bi-directional) specific 8 channel PCI Express LAI pinout $^{1,\,2,\,3,\,4,\,5}$

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | C0p- Upstream1 |

| 4    | C0p- Downstream1 | 3    | C0n- Upstream1 |

| 6    | C0n- Downstream1 | 5    | GND            |

| 8    | GND              | 7    | C1p- Upstream1 |

| 10   | C1p- Downstream1 | 9    | C1n- Upstream1 |

| 12   | C1n- Downstream1 | 11   | GND            |

| 14   | GND              | 13   | nc             |

| 16   | nc               | 15   | nc             |

| 18   | nc               | 17   | GND            |

| 20   | GND              | 19   | nc             |

| 22   | nc               | 21   | nc             |

| 24   | nc               | 23   | GND            |

|      |                  |      |                |

# x2 (2 unidirectional) specific 8 channel PCI Express LAI pinout $^{1,\,2,\,3,\,4}$

| Pin# | Signal Name     | Pin # | Signal Name     |

|------|-----------------|-------|-----------------|

| 2    | GND             | 1     | C0p- DirectionA |

| 4    | C0p- DirectionB | 3     | C0n- DirectionA |

| 6    | C0n- DirectionB | 5     | GND             |

| 8    | GND             | 7     | C1p- DirectionA |

| 10   | C1p- DirectionB | 9     | C1n- DirectionA |

| 12   | C1n- DirectionB | 11    | GND             |

| 14   | GND             | 13    | nc              |

| 16   | nc              | 15    | nc              |

| 18   | nc              | 17    | GND             |

| 20   | GND             | 19    | nc              |

| 22   | nc              | 21    | nc              |

| 24   | nc              | 23    | GND             |

#### or

| Pin # | Signal Name      | Pin# | Signal Name    |

|-------|------------------|------|----------------|

| 2     | GND              | 1    | nc             |

| 4     | nc               | 3    | nc             |

| 6     | nc               | 5    | GND            |

| 8     | GND              | 7    | nc             |

| 10    | nc               | 9    | nc             |

| 12    | nc               | 11   | GND            |

| 14    | GND              | 13   | C0p- Upstream1 |

| 16    | C0p- Downstream1 | 15   | C0n- Upstream1 |

| 18    | C0n- Downstream1 | 17   | GND            |

| 20    | GND              | 19   | C1p- Upstream1 |

| 22    | C1p- Downstream1 | 21   | C1n- Upstream1 |

| 24    | C1n- Downstream1 | 23   | GND            |

- 1 Polarity (p and n) of the differential pair may be swapped.

- 2 Can probe upstream 2 channels AND downstream 2 channels of ONE x2 link with one 8 Channel LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-upstream1 may be swapped in above tables with channel 1-upstream1, etc.

- 4 Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream, etc. Note that if one channel of upstream swapped with downstream, all channels upstream and downstream channels must be swapped.

- ${\bf 5} \quad \hbox{Consult your LA vendor for capabilities of this configuration}.$

#### or

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | nc              |

| 4    | nc              | 3    | nc              |

| 6    | nc              | 5    | GND             |

| 8    | GND             | 7    | nc              |

| 10   | nc              | 9    | nc              |

| 12   | nc              | 11   | GND             |

| 14   | GND             | 13   | C0p- DirectionA |

| 16   | C0p- DirectionB | 15   | C0n- DirectionA |

| 18   | C0n- DirectionB | 17   | GND             |

| 20   | GND             | 19   | C1p- DirectionA |

| 22   | C1p- DirectionB | 21   | C1n- DirectionA |

| 24   | C1n- DirectionB | 23   | C0p- DirectionA |

|      |                 |      |                 |

- $1\quad \text{ Polarity (p and n) of the differential pair may be swapped.}\\$

- 2 Can probe DirectionA 2 channels AND DirectionB 2 channels of ONE x2 link with one 8 channel LAI.

- 3 Entire link assignment may be reversed in LAI. For example, channel 0-DirectionA may be swapped in above tables with channel 1-DirectionA, etc.

- 4 Consult your LA vendor for capabilities of this configuration.

### Table 15.

### Table 14.

# Half-size midbus pin assignment

# x1 (bi-directional) specific 8 channel PCI Express LAI pinout $^{1,\,2,\,3}$

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | C0p- Upstream1 |

| 4    | C0p- Downstream1 | 3    | C0n- Upstream1 |

| 6    | C0n- Downstream1 | 5    | GND            |

| 8    | GND              | 7    | nc             |

| 10   | nc               | 9    | nc             |

| 12   | nc               | 11   | GND            |

| 14   | GND              | 13   | nc             |

| 16   | nc               | 15   | nc             |

| 18   | nc               | 17   | GND            |

| 20   | GND              | 19   | nc             |

| 22   | nc               | 1    | nc             |

| 24   | nc               | 23   | GND            |

|      | ·                |      |                |

### or D:

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | nc             |

| 4    | nc               | 3    | nc             |

| 6    | nc               | 5    | GND            |

| 8    | GND              | 7    | nc             |

| 10   | nc               | 9    | nc             |

| 12   | nc               | 11   | GND            |

| 14   | GND              | 13   | C0p- Upstream1 |

| 16   | C0p- Downstream1 | 15   | C0n- Upstream1 |

| 18   | C0n- Downstream1 | 17   | GND            |

| 20   | GND              | 19   | nc             |

| 22   | nc               | 21   | nc             |

| 24   | nc               | 23   | GND            |

|      |                  |      |                |

### or

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | nc             |

| 4    | nc               | 3    | nc             |

| 6    | nc               | 5    | GND            |

| 8    | GND              | 7    | C0p- Upstream1 |

| 10   | C0p- Downstream1 | 9    | C0n- Upstream1 |

| 12   | C0n- Downstream1 | 11   | GND            |

| 14   | GND              | 13   | nc             |

| 16   | nc               | 15   | nc             |

| 18   | nc               | 17   | GND            |

| 20   | GND              | 19   | nc             |

| 22   | nc               | 21   | nc             |

| 24   | nc               | 23   | GND            |

### or

| Pin# | Signal Name      | Pin# | Signal Name    |

|------|------------------|------|----------------|

| 2    | GND              | 1    | nc             |

| 4    | nc               | 3    | nc             |

| 6    | nc               | 5    | GND            |

| 8    | GND              | 7    | nc             |

| 10   | nc               | 9    | nc             |

| 12   | nc               | 11   | GND            |

| 14   | GND              | 13   | nc             |

| 16   | nc               | 15   | nc             |

| 18   | nc               | 17   | GND            |

| 20   | GND              | 19   | C0p- Upstream1 |

| 22   | C0p- Downstream1 | 21   | C0n- Upstream1 |

| 24   | C0n- Downstream1 | 23   | GND            |

|      |                  |      |                |

### Table 16.

$<sup>1\</sup>quad \text{ Polarity (p and n) of the differential pair may be swapped.}$

<sup>2</sup> Can probe upstream channel AND downstream channel of ONE x1 link with one 8 channel LAI.

<sup>3</sup> Upstream and downstream pin assignments may be swapped. For example, channel 0-upstream may be swapped with channel 0-downstream.

# Half-size midbus pin assignment

# x1 (2 unidirectional) specific 8 channel PCI Express LAI pinout $^{1,\,2}$

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | C0p- DirectionA |

| 4    | COp- DirectionB | 3    | C0n- DirectionA |

| 6    | C0n- DirectionB | 5    | GND             |

| 8    | GND             | 7    | nc              |

| 10   | nc              | 9    | nc              |

| 12   | nc              | 11   | GND             |

| 14   | GND             | 13   | nc              |

| 16   | nc              | 15   | nc              |

| 18   | nc              | 17   | GND             |

| 20   | GND             | 19   | nc              |

| 22   | nc              | 21   | nc              |

| 24   | nc              | 23   | GND             |

|      |                 |      |                 |

### or

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | nc              |

| 4    | nc              | 3    | nc              |

| 6    | nc              | 5    | GND             |

| 8    | GND             | 7    | C0p- DirectionA |

| 10   | C0p- DirectionB | 9    | C0n- DirectionA |

| 12   | C0n- DirectionB | 11   | GND             |

| 14   | GND             | 13   | nc              |

| 16   | nc              | 15   | nc              |

| 18   | nc              | 17   | GND             |

| 20   | GND             | 19   | nc              |

| 22   | nc              | 21   | nc              |

| 24   | nc              | 23   | GND             |

or

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | nc              |

| 4    | nc              | 3    | nc              |

| 6    | nc              | 5    | GND             |

| 8    | GND             | 7    | nc              |

| 10   | nc              | 9    | nc              |

| 12   | nc              | 11   | GND             |

| 14   | GND             | 13   | C0p- DirectionA |

| 16   | C0p- DirectionB | 15   | C0n- DirectionA |

| 18   | C0n- DirectionB | 17   | GND             |

| 20   | GND             | 19   | nc              |

| 22   | nc              | 21   | nc              |

| 24   | nc              | 23   | GND             |

|      |                 |      |                 |

or

| Pin# | Signal Name     | Pin# | Signal Name     |

|------|-----------------|------|-----------------|

| 2    | GND             | 1    | nc              |

| 4    | nc              | 3    | nc              |

| 6    | nc              | 5    | GND             |

| 8    | GND             | 7    | nc              |

| 10   | nc              | 9    | nc              |

| 12   | nc              | 11   | GND             |

| 14   | GND             | 13   | nc              |

| 16   | nc              | 15   | nc              |

| 18   | nc              | 17   | GND             |

| 20   | GND             | 19   | COp- DirectionA |

| 22   | C0p- DirectionB | 21   | C0n- DirectionA |

| 24   | C0n- DirectionB | 23   | GND             |

|      |                 |      |                 |

### Table 17.

<sup>1</sup> Polarity (p and n) of the differential pair may be swapped.

<sup>2</sup> Can probe DirectionA 1 channel AND DirectionB 1 channel of ONE x1 link with one 8 channel LA.

### **Reference Clock**

### LAI reference clock electrical requirements

| LAI Requirement                                                              | Symbol | Min    | Max     | Comments                             |

|------------------------------------------------------------------------------|--------|--------|---------|--------------------------------------|

| Differential voltage at ref clock attach point                               | Vdiff  | 0.8 V  | 5 V     | Vdiff =  2*(Vrefclockp - Vrefclockn) |

| Reference clock frequency (with SSC and/or frequency margining) <sup>1</sup> | f      | 90 MHz | 110 MHz |                                      |

<sup>1</sup> If reference clock tolerance is less than ±150 ppm, there is no need for providing reference to the LAI.

If the reference clock tolerance is greater than ±150 ppm, there is a need for providing reference to the LAI.

Table 18.

### LAI reference clock probe load model

Load models for the reference clock probe are given in this section. System designers will be expected to perform simulations of the reference clock networks with the header and LAI load models to ensure good signal integrity of the reference clocks at the header to the LAI. The pin header parasitics may be obtained from the connector vendor.

Figure 11. Agilent Technologies PCI Express reference clock probe load model

# Appendix A

# PCI Express probing design review checklist

The following tables serve as a guide to review a platform (schematics and layout) with regard to PCI Express probing.

### **General considerations**

| PASS | FAIL | NA | ISSUE                                                                                                                                                      |

|------|------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |    | Ideally, all PCI Express links in the system should be observable with LA tools either using "midbus" probing or through a add-in card interposer.         |

|      |      |    | If any PCI Express links are not observable with LA tools (see previous item) then the design and validation team(s) should agree that this is acceptable. |

### Midbus probing configurations

| PASS | FAIL | NA | ISSUE                                                                                                                                                                                                                                                                                                                                                                         |

|------|------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |    | For each midbus footprint in the system, the number of links and sizes of those links within a footprint must meet the requirements of the "Link configuration support" section (page 2) of the probing design guide. (For example, a single midbus footprint can contain the upstream channels of one x16 link or both the upstream and downstream channels of one x8 link.) |

|      |      |    | If the configuration of the links within a midbus footprint does not meet the requirements of the previous item, then this configuration must be confirmed with Agilent.                                                                                                                                                                                                      |

|      |      |    | If a reference clock is required by the LAI then a connector for the reference clock must be provided for each PCI Express reference clock domain.                                                                                                                                                                                                                            |

|      |      |    | Reference clock is required if spread spectrum clocking (SSC) is used and can't be disabled in the system.                                                                                                                                                                                                                                                                    |

|      |      |    | Reference clock is required if testing with SSC is needed (because problem does not manifest with SSC disabled.)                                                                                                                                                                                                                                                              |