# **Multicycles Explained**

**Using TimeQuest Timing Analyzer**

### Introduction

To properly constrain a design, it is important to provide multicycle assignments to timing-driven compilation. Multicycle assignments relax the timing requirements, thus allowing the fitter a greater degree of freedom. As such, they reduce the overall compilation time and provide greater quality of results. Multicycle assignments are often misunderstood and poorly applied. This Tech Note aims to do the following:

- 1. Provide a concise definition for multicycles

- 2. Show the basic types of multicycles with examples

- 3. Illustrate applications of multicycles in common circuits

All examples will be provided with accompanying analysis in the Altera<sup>®</sup> Quartus<sup>®</sup> II TimeQuest Timing Analyzer. It is assumed the reader is familiar with static timing analysis and operation of TimeQuest.

## **Multicycle Defined**

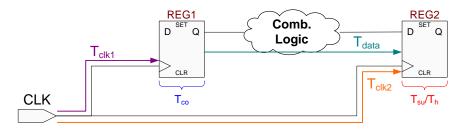

Figure 1 shows a simple circuit<sup>1</sup> for setup and hold slack:

Figure 1. Simple Register-Register Path

Let's begin with a setup check:

Setup slack<sup>2</sup> = Data Required Time – Data Arrival Time [1]

= (Latch Edge +

$$T_{clk2}^3 - T_{su}$$

) – (Launch Edge +  $T_{clk1}^4 + T_{co} + T_{data}^4$ ) [2]

= (Latch Edge – Launch Edge) + ( $T_{clk2} - T_{clk1}$ ) – ( $T_{co} + T_{data} + T_{su}$ ) [3]

Setup Relationship Clock Data Path Skew

Simplified circuit shown. REG1/REG2 may be internal or external to FPGA. For example, REG1 could be in an upstream external device or REG2 could be in a downstream external device. Clock source for REG1/REG2 do not necessarily need to be the same. Examples of non-similar clock sources will be shown later in this document.

<sup>&</sup>lt;sup>2</sup> Clock uncertainty, early & late clock latency ignored for the sake of simplicity.

<sup>&</sup>lt;sup>3</sup> Minimum delay used

<sup>4</sup> Maximum delay used

where, T<sub>clk1</sub> - propagation delay from clock source to clock input on source register

T<sub>clk2</sub> - propagation delay from clock source to clock input on destination register

T<sub>data</sub> - propagation delay from source register to data input on destination register

T<sub>co</sub> - Clock to output delay of source register

T<sub>su</sub> - Setup requirement of destination register

Hold requirement of destination register

From equation [3] the setup relationship is the number of clock periods between the latch edge and the launch edge.

Typically for single cycle setup analysis: Latch Edge – Launch Edge = 1 clock cycle

When this relationship is greater than one clock period and an integer multiple of the clock period, then a multicycle setup relationship is said to exist.

TimeQuest timing analyzer defaults to single cycle setup analysis. If your design has multicycle relationships, then applying multicycle assignments reduces the timing burden placed upon the fitter. By applying multicycle setup constraints, the setup slack equation is loosened by integer multiples of the clock period.

Multicycle setup constraint is defined as the integer number of clock periods, N, where N>1, to relax the setup slack equation. The default value is one.

Next, let's examine a hold check:

Hold slack<sup>5</sup> = Data Arrival Time - Data Required Time = (Launch Edge +

$$T_{clk1}^6$$

+  $T_{co}$  +  $T_{data}^6$ ) - (Latch Edge +  $T_{clk2}^7$  -  $T_h$ ) [6] = (Launch Edge - Latch Edge) - ( $T_{clk2}$  -  $T_{clk1}$ ) + ( $T_{co}$  +  $T_{data}$  -  $T_h$ ) [7] Hold Relationship Clock Skew

From equation [7], the hold relationship is the number of clock periods between the latch edge and the launch edge.

Typically for single cycle hold analysis: Launch Edge – Latch Edge = 0 clock cycles

When this relationship is greater than zero clock periods and an integer multiple of the clock period, then a multicycle hold relationship is said to exist.

Multicycle Hold Relationship: (Launch Edge – Latch Edge) = N\*(clock period), N>0 [8]

<sup>&</sup>lt;sup>5</sup> Clock uncertainty, early & late clock latency ignored for sake of simplicity

<sup>&</sup>lt;sup>6</sup> Minimum delay used

Maximum delay used

As with setup, TimeQuest timing analyzer will default to single cycle hold analysis. If your design has multicycle relationships, then applying multicycle assignments reduces the timing burden placed upon the fitter. By applying multicycle hold constraints, the hold slack equation is loosened by integer multiples of the clock period.

Multicycle hold constraint is defined as the integer number of clock periods, N, where N>0, to relax the hold slack equation. The default value is zero.

## **TimeQuest Timing Analyzer**

TimeQuest timing analyzer will examine all register-to-register paths and perform setup and hold checks. These checks are based upon evaluating the launch and latch edge relationships.

When performing setup checks, for each and every latch edge at the destination register, TimeQuest uses the closest previous clock edge at the source register as the launch edge.

When performing hold checks, TimeQuest performs two checks. The first hold check determines that the data launched by the current launch edge is not captured by the previous latch edge. The second hold check determines that the data launched by the next launch edge is not captured by the current latch edge.

TimeQuest will perform hold checks for every possible setup relationship and not just the worst case setup relationship. Note though, only the worst case relationship is reported.

If hold check overlaps a setup check, then the hold check is ignored.

## **Types of Multicycles**

There are two categories of multicycles:

- 1. Destination Multicycles: This type of multicycle loosens the slack equation by changing the destination clock edge. i.e. relaxing the latch edge

- 2. Source Multicycles: This type of multicycle loosens the slack equation by changing the source clock edge. i.e. relaxing the launch edge

For each of these categories, it is further possible to define setup and hold variants. Table 1 summarizes common types of multicycles<sup>8</sup>.

**Table 1 Multicycle Types**

| Type                         | Clock       | Timing Check | Shorthand |

|------------------------------|-------------|--------------|-----------|

| Destination Multicycle Setup | Destination | Setup        | DMS       |

| Destination Multicycle Hold  | Destination | Hold         | DMH       |

| Source Multicycle Setup      | Source      | Setup        | SMS       |

| Source Multicycle Hold       | Source      | Hold         | SMH       |

The shorthand in Table 1 will be used for the remainder of this document.

<sup>&</sup>lt;sup>8</sup> The most commonly used types are shown in Table 1. The set\_multicycle\_path constraint will support other variants

### **Basic Cases**

In this section, we will examine the application of multicycle assignments to the simple register-register circuit shown in Figure 1. We will go thru the analysis of the type of multicycle assignments defined in Table 1.

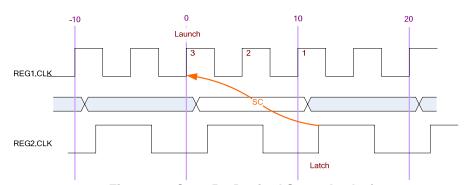

## Basic Case: Single Cycle

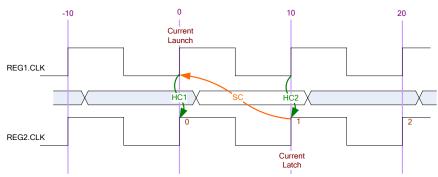

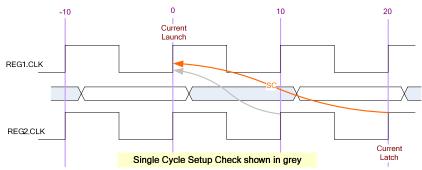

Let's first look at the setup and hold checks performed by TimeQuest during single cycle analysis.

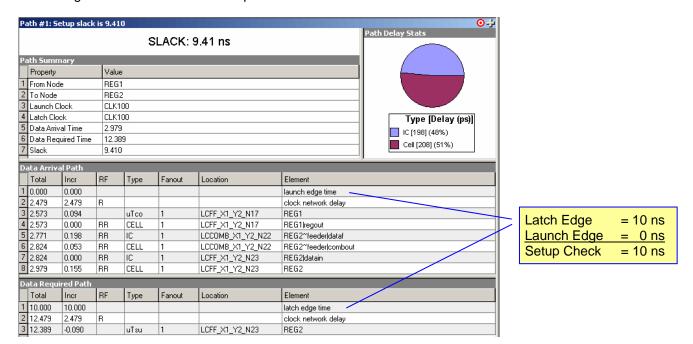

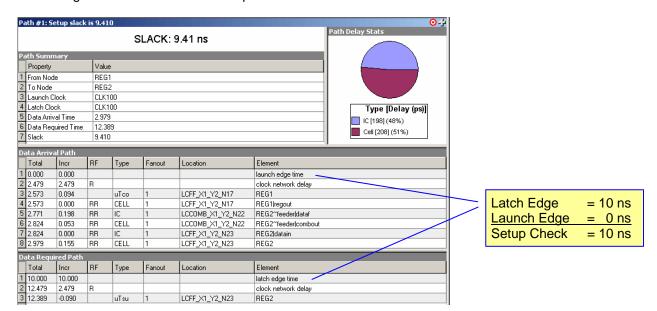

Figure 2 Single Cycle Analysis

Applying equations 9, 10, and 11:

Note that both Hold Checks are equivalent in magnitude.

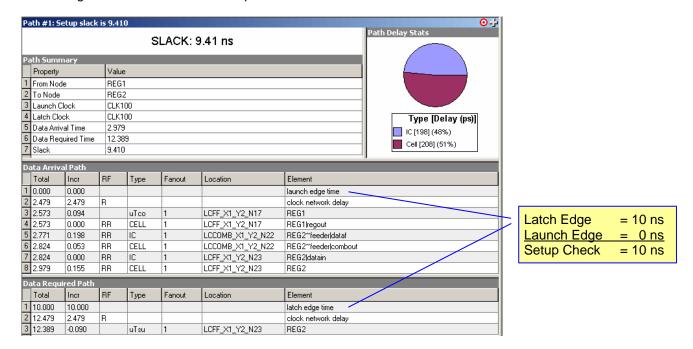

#### Examining TimeQuest results for setup:

#### Examining TimeQuest results for hold:

TimeQuest timing analyzer does not report both hold checks. It will display the worst case check.

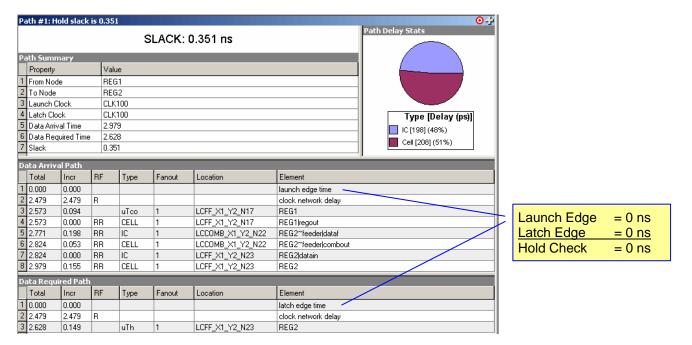

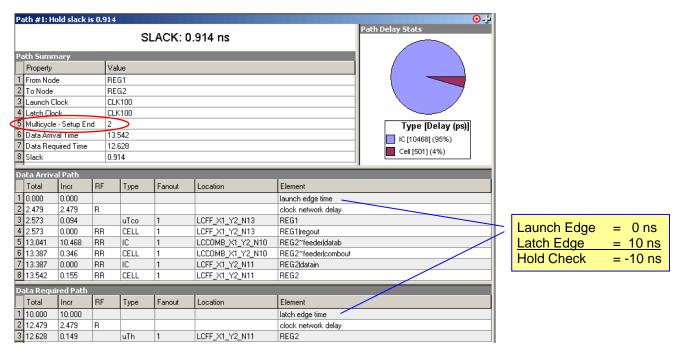

#### Basic Case: DMS = 2 & DMH = 0

In this case we have a Destination Multicycle Setup, DMS, of 2 and a Destination Multicycle Hold, DMH, of zero. We are relaxing the setup slack equation by latching the data a clock cycle later than the single cycle case. Hold analysis remains single cycle<sup>9</sup>.

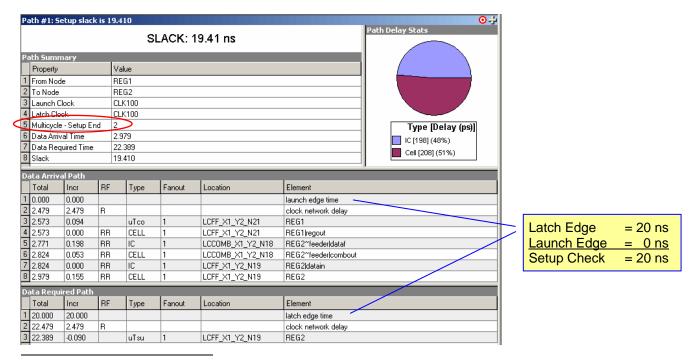

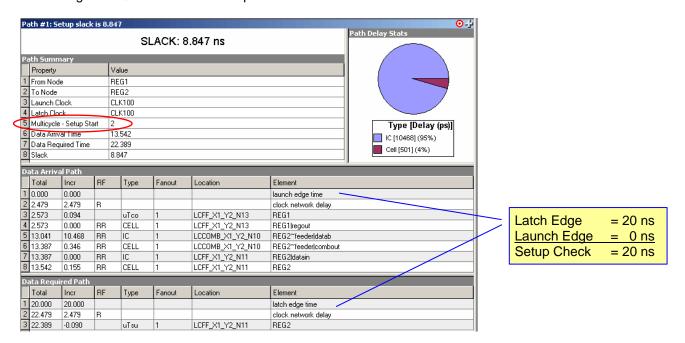

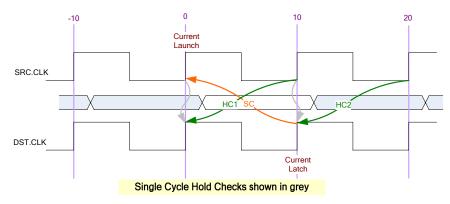

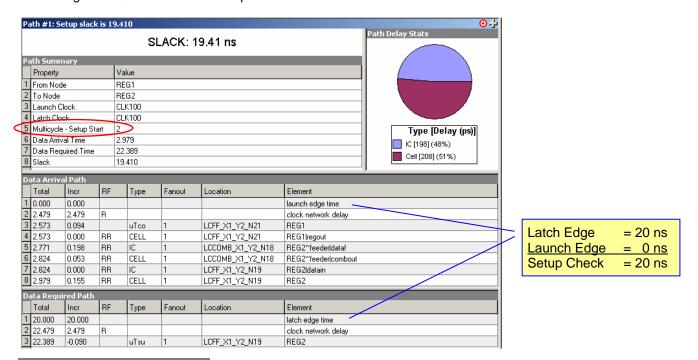

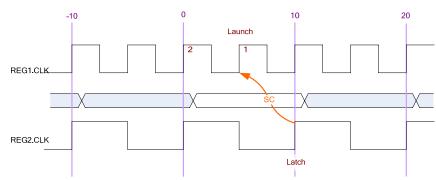

Figure 3 displays the setup check for this case. Note the latch edge is now a cycle later than the default single cycle analysis. By applying a DMS= 2, the setup relationship will be 20 ns for each and every latch edge.

Figure 3 DMS=2, DMH=0 Setup Check

#### Applying equation 9:

Setup Check = Current Latch Edge<sup>10</sup> – Closest Previous Launch Edge = 20 ns – 0 ns = 20 ns

Examining TimeQuest results for setup: Path #1: Setup slack is 8.847 Path Delay Stats SLACK: 8.847 ns Path Summary Property Value 1 From Node REG1 2 To Node 3 Launch Clock REG2 CLK100 4 Latch Clock CLK100 5 Multicycle - Setup End Type [Delay (ps)] 6 Data Arrival Time 7 Data Required Time 8 Slack 13.542 IC [10468] (95%) 22.389 Cell [501] (4%) 8.847 Data Arrival Path Total Fanout Location Element Incr Туре 1 0.000 0.000 launch edge time 2 2.479 3 2.573 4 2.573 5 13.041 2.479 clock network delay 0.094 uTco LCFF\_X1\_Y2\_N13 REG1 RR LCFF\_X1\_Y2\_N13 REG1|regout 0.000 CELL LCCOMB\_X1\_Y2\_N10 10.468 RR REG2~feeder|datab 6 13.387 7 13.387 0.346 BB CELL LCCOMB\_X1\_Y2\_N10 REG2~feederlcombout LCFF\_X1\_Y2\_N11 REG2ldatain 0.000 BB 8 13.542 0.155 BB CELL LCFF\_X1\_Y2\_N11 REG2 Data Req Total Incr Туре Fanoul Location 1 20.000 20,000 latch edge time 2 22.479 2.479 R clock network delay 3 22.389 LCFF\_X1\_Y2\_N11 -0.090 uTsu REG2

Launch Edge = 20 ns Launch Edge = 0 ns Setup Check = 20 ns

<sup>10</sup> Adjusted for multicycle assignment

<sup>&</sup>lt;sup>9</sup> Recall from earlier definition, the default value for hold multicycle is zero.

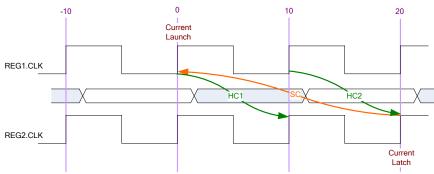

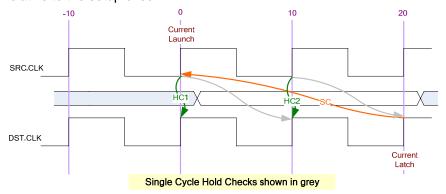

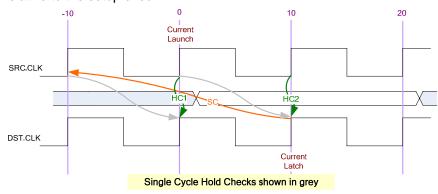

Since Hold analysis remains single cycle, analysis will be consistent with previous discussions on single cycle hold. Figure 4 displays the hold checks for this case. Note hold checks are relative to the setup check. In general Hold checks are performed on every possible setup check and not just to the most conservative setup check edges.

Figure 4 DMS=2, DMH=0 Hold Checks

Applying equations 10 and 11:

#### Basic Case: DMS = 1 & DMH = 1

In this case we have a Destination Multicycle Setup, DMS, of 1 and a Destination Multicycle Hold, DMH, of 1. Setup analysis remains single cycle. For hold slack equation, we are latching the data a clock cycle later than the single cycle case.

Since setup analysis remains single cycle, analysis will be consistent with previous discussions on single cycle setup. Figure 5 displays the setup check for this case.

Figure 5 DMS=1, DMH=1 Setup Check

#### Applying equation 9:

Examining TimeQuest results for Setup:

By applying a DMH=1, the hold relationship will be 10 ns for each and every latch edge. Recall that for single cycle analysis, the hold relationship is 0 ns. Figure 6 displays the hold checks for this case. Note hold checks are relative to the setup check.

Figure 6 DMS=1, DMH=1 Hold Checks

Applying equations 10 and 11:

<sup>&</sup>lt;sup>11</sup> Adjusted for multicycle assignment

<sup>&</sup>lt;sup>12</sup> Hold timing is relaxed by moving the clock edge in the opposite direction to Setup.

#### Basic Case: DMS = 2 & DMH = 1

In this case we have a Destination Multicycle Setup, DMS, of 2 and a Destination Multicycle Hold, DMH, of 1. For both setup and hold slack equations, we are latching the data a clock cycle later than the single cycle case.

Figure 7 displays the setup check for this case. Note the latch edge is now a cycle later than the default single cycle analysis. By applying a DMS= 2, the setup relationship will be 20 ns for each and every latch edge.

Figure 7 DMS=2, DMH=1 Setup Check

#### Applying equation 9:

Examining TimeQuest results for setup:

<sup>&</sup>lt;sup>13</sup> Adjusted for multicycle assignment

By applying a DMH=1, the hold relationship will be 10 ns for each and every latch edge. Recall that for single cycle analysis, the hold relationship is 0 ns. Figure 8 displays the hold checks for this case. Note hold checks are relative to the setup check.

Figure 8 DMS=2, DMH=1 Hold Checks

Applying equations 10 and 11:

Hold Check 1 = Current Launch Edge – Previous Latch Edge<sup>14</sup>

=

$$0 \text{ ns} - 0 \text{ ns}^{15}$$

=  $0 \text{ ns}$

Hold Check 2 = Next Launch Edge – Current Latch Edge<sup>14</sup>

=  $10 \text{ ns} - 10 \text{ ns}^{15}$

=  $0 \text{ ns}$

<sup>&</sup>lt;sup>14</sup> Adjusted for multicycle assignment

<sup>&</sup>lt;sup>15</sup> Hold timing is relaxed by moving the clock edge in the opposite direction to Setup.

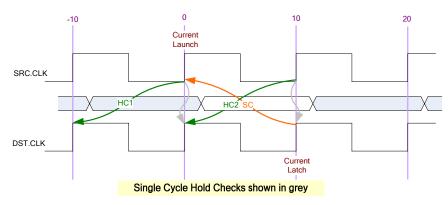

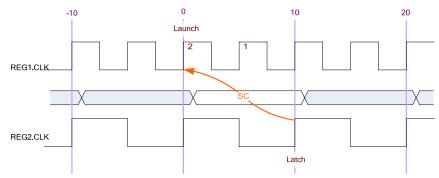

#### Basic Case: SMS = 2 & SMH = 0

In this case we have a Source Multicycle Setup, SMS, of 2 and a Source Multicycle Hold, SMH, of 0. We are relaxing the setup slack equation by launching the data a clock cycle earlier than the single cycle case. Hold analysis remains single cycle.

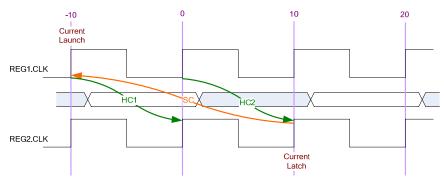

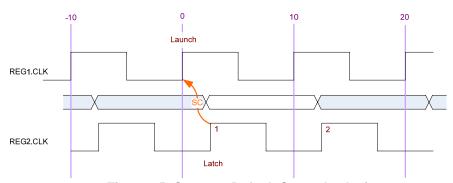

Figure 9 displays the setup check for this case. Note the launch edge is now a cycle earlier than the default single cycle analysis. By applying a SMS= 2, the setup relationship will be 20 ns for each and every launch edge.

Figure 9 SMS=2, SMH=0 Setup Check

#### Applying equation 9:

Examining TimeQuest results for setup:

<sup>&</sup>lt;sup>16</sup> Adjusted for multicycle assignment

Since Hold analysis remains single cycle, analysis will be consistent with previous discussions on single cycle hold. Figure 10 displays the hold checks for this case. Note hold checks are relative to the setup check.

Figure 10 SMS=2, SMH=0 Hold Checks

Applying equations 10 and 11:

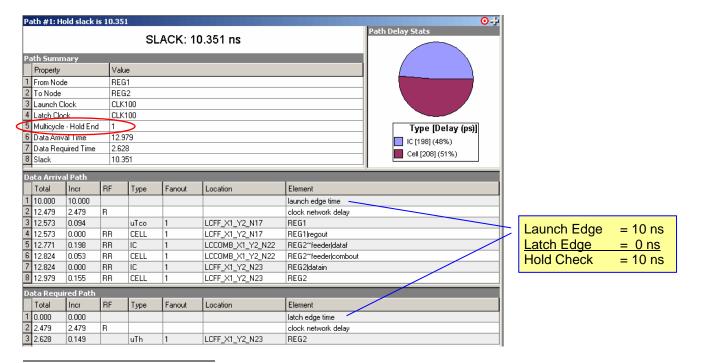

#### Basic Case: SMS = 1 & SMH = 1

In this case we have a Source Multicycle Setup, SMS, of 1 and a Source Multicycle Hold, SMH, of 1. Setup analysis remains single cycle. For hold slack equation, we are launching the data a clock cycle earlier than the single cycle case.

Since setup analysis remains single cycle, analysis will be consistent with previous discussions on single cycle setup. Figure 11 displays the setup check for this case.

Figure 11 SMS=1, SMH=1 Setup Check

#### Applying equation 9:

Setup Check = Current Latch Edge - Closest Previous Launch Edge = 10 ns - 0 ns = 10 ns

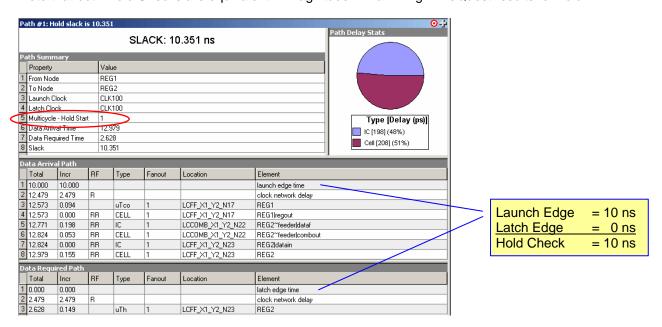

#### Examining TimeQuest results for Setup:

By applying a SMH=1, the hold relationship will be 10 ns for each and every launch edge. Recall that for single cycle analysis, the hold relationship is 0 ns. Figure 12 displays the hold checks for this case. Note hold checks are relative to the setup check.

Figure 12 SMS=1, SMH=1 Hold Checks

Applying equations 10 and 11:

<sup>&</sup>lt;sup>17</sup> Adjusted for multicycle assignment

<sup>&</sup>lt;sup>18</sup> Hold timing is relaxed by moving the clock edge in the opposite direction to Setup.

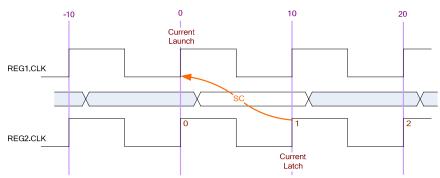

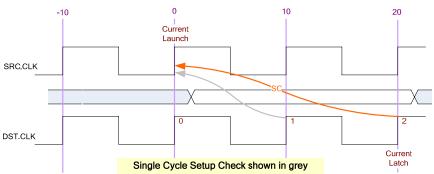

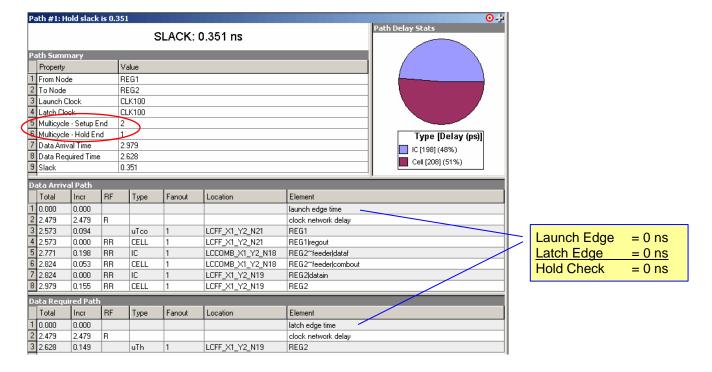

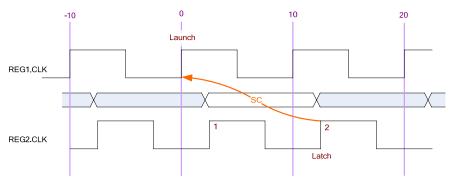

#### Basic Case: SMS = 2 & SMH = 1

In this case we have a Source Multicycle Setup, SMS, of 2 and a Source Multicycle Hold, SMH, of 1. For both setup and hold slack equations, we are launching the data a clock cycle earlier than the single cycle case.

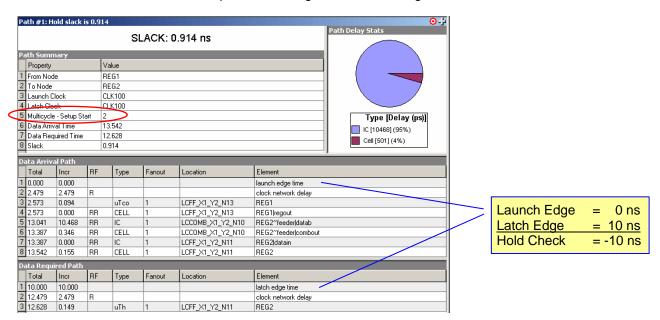

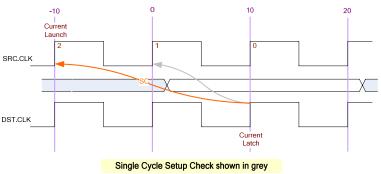

Figure 13 displays the setup check for this case. Note the latch edge is now a cycle later than the default single cycle analysis. By applying a SMS= 2, the setup relationship will be 20 ns for each and every launch edge.

Figure 13 SMS=2, SMH=1 Setup Check

#### Applying equation 9:

Setup Check = Current Latch Edge – Closest Previous Launch Edge<sup>19</sup> = 10 ns – (-10 ns) = 20 ns

Examining TimeQuest results for setup:

<sup>&</sup>lt;sup>19</sup> Adjusted for multicycle assignment

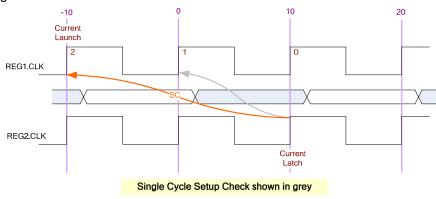

By applying a SMH=1, the hold relationship will be 10 ns for each and every launch edge. Recall that for single cycle analysis, the hold relationship is 0 ns. Figure 14 displays the hold checks for this case. Note hold checks are relative to the setup check.

Figure 14 SMS=2, SMH=1 Hold Checks

Applying equations 10 and 11:

Hold Check 1 = Current Launch Edge<sup>20</sup> – Previous Latch Edge

=

$$0 \text{ ns}^{21} - 0 \text{ ns}$$

=  $0 \text{ ns}$

Hold Check 2 = Next Launch Edge<sup>20</sup> – Current Latch Edge

=  $10 \text{ ns}^{21} - 10 \text{ ns}$

=  $0 \text{ ns}$

<sup>&</sup>lt;sup>20</sup> Adjusted for multicycle assignment

<sup>&</sup>lt;sup>21</sup> Hold timing is relaxed by moving the clock edge in the opposite direction to Setup.

## **Applications**

In this section, we will examine common cases where multicycle constraints should be applied. All of these cases are between related clock domains. If your design contains related clocks, for example PLL clocks and there are paths between the related clock domains, then multicycle constraints are applicable.

### Case 1: $Freq_{DST} = Freq_{SRC} + Offset$

In this case, the source and destination clocks are the same frequency. However the destination clock is offset with a positive phase shift.

Figure 15 shows the default setup analysis performed by TimeQuest. Assume 2 ns offset for the purposes of this discussion.

Figure 15 Case 1 - Default Setup Analysis

Applying equation 9:

In general, the setup relationship shown in Figure 15 is not the correct setup relationship required for typical circuits. Usually the desired setup relationship is as shown in Figure 16:

Figure 16 Case 1 – Desired Setup Analysis

To correct the default analysis, multicycle setup assignments must be applied.

For Desired Setup Analysis, DMS = 2 must be applied.

Next, let's look at the hold analysis for this case with DMS=2 applied. Figure 17 shows the hold analysis:

Figure 17 Case 1 - Hold Analysis

Applying equations 10 and 11:

The default hold analysis is correct. As such nothing further needs to be done. A DMH = 0 can be applied for completeness.

Now the question needs to be asked: What if there is a negative phase shift?

Figure 18 depicts this case and the associated setup and hold analysis.

Figure 18 Negative Phase Offset Case

Clearly the default analysis is correct. No multicycles assignments are needed in this case.

## Summary

- Destination clock is a positive phase shifted version of the source clock

- For correct analysis, the following are applicable:

- o DMS = 2

- o DMH = 0

- For negative phase shift, depending on amount of shift, multicycles may not be required.

## Case 2: $Freq_{DST} = N*Freq_{SRC}$ , N>1

In this case, the destination clock is an integer multiple of the source clock frequency. Figure 19 shows the default setup analysis performed by TimeQuest.

Figure 19 Case 2 – Default Setup Analysis

#### Applying equation 9:

Note that the data is not changing at edge 1 but rather at edge 2. Therefore, it is possible to relax the setup requirement by shifting the latch edge one clock period. The desired setup relationship is as shown in Figure 20:

Figure 20 Case 2 – Desired Setup Analysis

To correct the default analysis, multicycle setup assignments must be applied.

(B)

For Desired Setup Analysis, DMS = 2 must be applied.

Or For the more general case, DMS = N, where N>1 & N = integer multiplication factor.

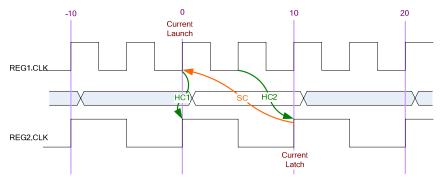

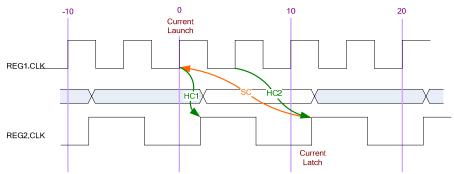

Next, let's look at the hold analysis for this case with DMS=2 applied. Figure 21 shows the default hold analysis.

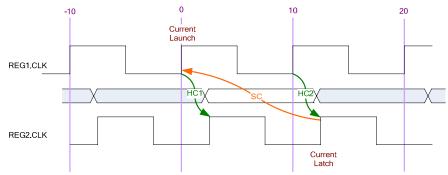

Figure 21 Case 2 – Default Hold Analysis

Applying equations 10 and 11:

Note Hold Check 1 is too restrictive. The data is launched by the edge at time 0 ns and should check against data capture by the previous latch edge at time 0 ns, not as depicted by HC1. To correct this, multicycle hold assignments must be applied.

For Desired Hold Analysis, DMH = 1 must be applied. Or For the more general case, DMH = N-1, where N>1& N = integer multiplication factor

## **Summary**

- Destination clock is an integer multiple, N, of the source clock

- For correct analysis, the following are applicable:

- $\circ$  DMS = N

- o DMH = N-1

## Case 3: $Freq_{DST} = N*Freq_{SRC} + Offset, N>1$

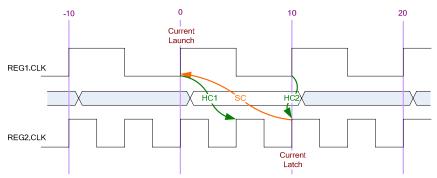

In this case, we have a combination of case 1 and case 2. The destination clock is an integer multiple of the source clock frequency with a positive phase shift. Figure 22 shows the default setup analysis performed by TimeQuest. Assume 2 ns offset for the purposes of this discussion.

Figure 22 Case 3 – Default Setup Analysis

Applying equation 9:

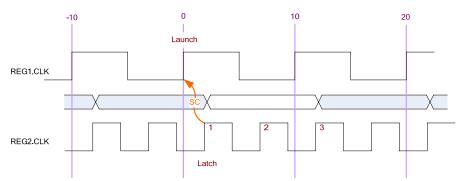

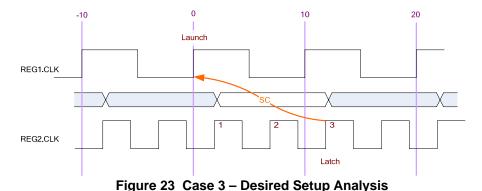

As with the previous cases, it is possible to relax the setup requirement by correcting for the offset and shifting the latch edge two clock periods. The desired setup relationship is as shown in Figure 23

To correct the default analysis, multicycle setup assignments must be applied.

For Desired Setup Analysis, DMS = 3 must be applied.

Or For the more general case, DMS = N+1, where N>1 & N = integer multiplication factor.

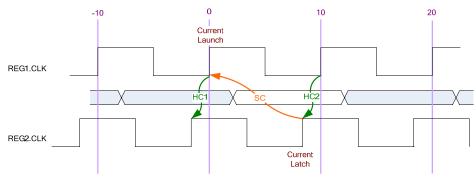

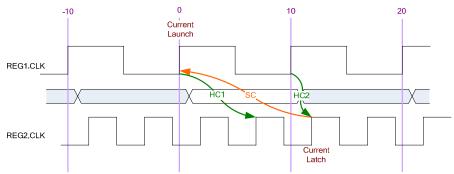

Next, let's look at the hold analysis for this case with DMS=2 applied. Figure 21 shows the default hold analysis.

Figure 24 Case 2 - Default Hold Analysis

Applying equations 10 and 11:

Note Hold Check 1 is too restrictive. The data is launched by the edge at time 0 ns and should check against data capture by the previous latch edge at time 2 ns, not as depicted by HC1. To correct this, multicycle hold assignments must be applied.

For Desired Hold Analysis, DMH = 1 must be applied. Or For the more general case, DMH = N-1, where N>1 & N = integer multiplication factor

## **Summary**

- Destination clock is an integer multiple, N, of the source clock with positive offset

- For correct analysis, the following are applicable:

- o DMS = N+1

- o DMH = N-1

## Case 4: $Freq_{DST} = Freq_{SRC}/N$ , N>1

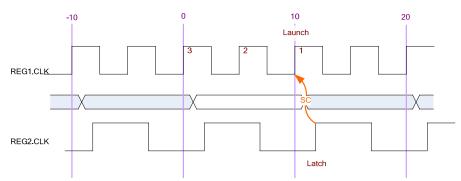

In this case, the destination clock is an integer divisor of the source clock frequency. Figure 25 shows the default setup analysis performed by TimeQuest.

Figure 25 Case 4 – Default Setup Analysis

#### Applying equation 9:

Note that the data is not launched at edge 1 but rather at edge 2. Therefore it is possible to relax the setup requirement by shifting the launch edge one clock period. The desired setup relationship is as shown in Figure 26

Figure 26 Case 4 – Desired Setup Analysis

To correct the default analysis, multicycle setup assignments must be applied.

(8)

For Desired Setup Analysis, SMS = 2 must be applied. Or For the more general case, SMS = N, where N>1 & N = integer divisor factor.

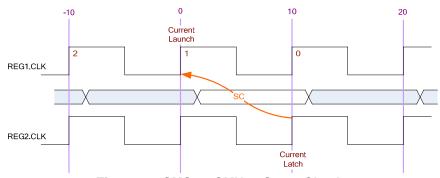

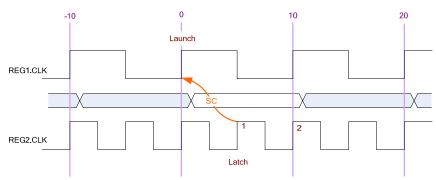

Next, let's look at the hold analysis for this case with SMS=2 applied. Figure 27 shows the default hold analysis.

Figure 27 Case 4 – Default Hold Analysis

Applying equations 10 and 11:

Note Hold Check 2 is too restrictive. The data is launched next by the edge at time 10 ns and should check against data capture by the current latch edge at time 10 ns, not as depicted by HC2. To correct this, multicycle hold assignments must be applied.

For Desired Hold Analysis, SMH = 1 must be applied. Or For the more general case, SMH = N-1, where N>1 & N = integer divisor factor

## **Summary**

- Destination clock is an integer divisor, N, of the source clock

- For correct analysis, the following are applicable:

- $\circ$  SMS = N

- o SMH = N-1

### Case 5: $Freq_{DST} = Freq_{SRC}/N + Offset, N>1$

In this case, the destination clock is an integer divisor of the source clock frequency plus positive phase offset. Figure 28 shows the default setup analysis performed by TimeQuest. Assume 2 ns offset for the purposes of this discussion.

Figure 28 Case 5 – Default Setup Analysis

Applying equation 9:

Note that the data is not launched at edge 1 but rather at edge 3. Therefore it is possible to relax the setup requirement by shifting the launch edge two clock periods. The desired setup relationship is as shown in Figure 29:

Figure 29 Case 5 – Desired Setup Analysis

To correct the default analysis, multicycle assignments must be applied.

Or

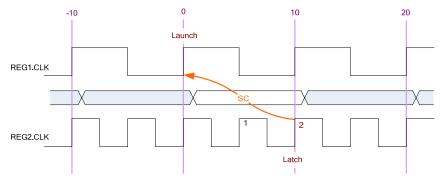

For Desired Setup Analysis, SMS = 3 must be applied. For the more general case, SMS = N+1, where N>1 & N = integer divisor factor. Next, let's look at the hold analysis for this case with SMS=3 applied. Figure 30 shows the default hold analysis.

Figure 30 Case 5 – Default Hold Analysis

Applying equations 10 and 11:

Note Hold Check 2 is too restrictive. The data is launched next by the edge at time 10 ns and should check against data capture by the current latch edge at time 12 ns, not as depicted by HC2. To correct this, multicycle hold assignments must be applied.

For Desired Hold Analysis, SMH = 1 must be applied.

Or For the more general case, SMH = N-1, where N>1 & N=integer divisor factor

## **Summary**

- Destination clock is an integer divisor, N, of the source clock

- For correct analysis, the following are applicable:

- SMS = N+1

- o SMH = N-1