Rock87

Участник-

Постов

10 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Rock87

- День рождения 28.08.1987

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

-

Помогите выбрать одноплатник

Rock87 ответил Rock87 тема в В помощь начинающему

А почему использовать Windows для промышленной автоматике глупо? -

Помогите выбрать одноплатник

Rock87 ответил Rock87 тема в В помощь начинающему

Не встречал у обычного компьютера входа/выхода. Думаете есть такие? -

Помогите выбрать одноплатник

Rock87 опубликовал тема в В помощь начинающему

Здравствуйте! Занимаюсь промышленной автоматикой, недавно закончил курсы по С++ и захотелось как-нибудь применить полученные знания. Нужен одноплатный компьютер с поддержкой ОС Windows (программку собираюсь писать на CBuilder), хоть каким-нибудь количеством портов ввода-вывода и периферийными интерфейсами (UART, USB, VGA). Нет ли чего такого? Желательно уложиться в 5-10 тысяч. -

Помогите найти контакты

Rock87 опубликовал тема в Пайка и монтаж

Хотим скопировать "забугровскую" приспособу. Никто не знает где можно взять (купить, своровать) контакты, что на фото? Контакты подпружинены. Буду признателен за "пинок" в верном направлении. -

Warnings от ISE

Rock87 ответил Rock87 тема в Работаем с ПЛИС, области применения, выбор

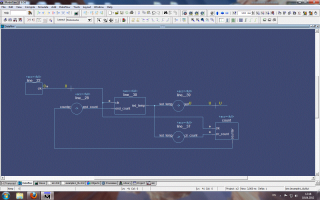

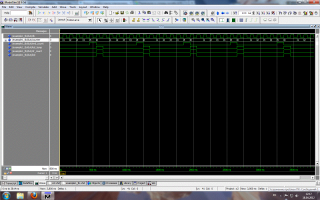

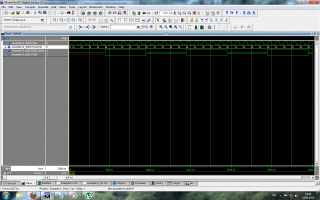

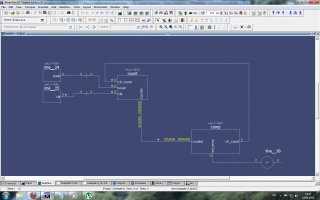

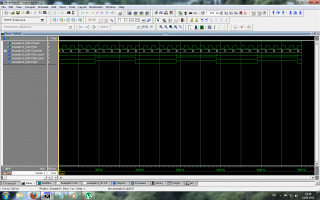

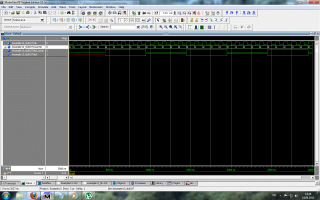

to Mad_max По поводу триггера понял, спасибо. По поводу кода, который Вы предложили: USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity Example1 is Port ( clk : in STD_LOGIC; -- входной сигнал генератора led : out STD_LOGIC); -- выходной сигнал на светодиод end Example1; architecture Behavioral of Example1 is signal counter: std_logic_vector (31 downto 0):=(others=>'0');-- объявляем сигнал counter в котором будем считать тики генератора signal led_temp: std_logic:='0'; -- вспомогательный сигнал signal clr_count: std_logic:='0'; -- сигнал сброса счетчика при совпадении компаратора signal end_count: std_logic:='0'; begin count: process(clk, clr_count) -- процесс"СЧЕТЧИК" begin if(clr_count='1') then -- если сигнал сброса счетчика установлен в 1 counter <= (others=>'0'); -- обнуляем счетчик elsif(rising_edge(clk)) then -- если нет, то по фронту сигнала clk считаем тики генератора counter <= counter + 1; end if; end process; end_count <= '1' when (counter = 5) else '0'; --компаратор process(clk) -- выходной триггер begin if (rising_edge(clk)) then led_temp <= end_count; end if; end process; clr_count <= led_temp; -- сигнал сброса led<=led_temp; -- соединяем led_temp с выходным сигналом led end Behavioral; Логика работы этого кода отлична от заданной (мигание светодиодом). К примеру вот результат моей программы: Вот Ваш вариант Или я чего-то не понял или неверно изложил? Тогда прошу поправить меня. На всякий ссылка на предъидущий пост to dsmv Попробовал второй вариант. comp: process(counter) -- процесс"КОМПАРАТОР" begin if(rising_edge(clk)) then if(counter= 5) then -- если счетчик = уставке clr_count<='1'; -- активируем сигнал сброса счетчика led_temp<=not led_temp; -- переключаем вспомогательный сигнал else clr_count<='0'; -- иначе "на всякий" обнуляем сигнал сброса end if; end if; end process; Синтезеатор снял свое предупреждение, спасибо. -

Warnings от ISE

Rock87 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Имеем ISE 13.3, пишем на VHDL. При синтезе следующего кода library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; library UNISIM; use UNISIM.VComponents.all; entity rrd3_top is Port ( G1_CLK : in STD_LOGIC; --Тактовый сигнал доп. генератора 10 МГц EXT_LED_N : out STD_LOGIC_VECTOR (5 downto 0) --Управление светодиодами ); end rrd3_top; architecture Structural of rrd3_top is signal clk1 : STD_LOGIC := '0'; --Тактовый сигнал доп. генератора 10 МГц signal led_n : STD_LOGIC_VECTOR (5 downto 0) := (others => '1');--Управление светодиодами signal counter: std_logic_vector (31 downto 0):=(others=>'0');-- объявляем сигнал counter в котором будем считать тики генератора signal led_temp: std_logic:='0'; -- триггер выходного сигнала led signal clr_count: std_logic:='0'; -- сброс счетчика при совпадении компаратора begin ibufg_clk1 : ibufg port map(clk1,G1_CLK); -- 10 MHz obuf_led_gen: --светодиоды for i in 0 to 5 generate obuf_led : obuf port map(EXT_LED_N(i),led_n(i)); end generate; count: process(clk1, clr_count) -- процесс"СЧЕТЧИК" begin if(clr_count='1') then -- если нажата кнопка reset или сигнал сброса счетчика установлен в 1 counter <= (others=>'0'); -- обнуляем счетчик elsif(rising_edge(clk1)) then -- если нет, то по фронту сигнала clk считаем тики генератора counter <= counter + 1; end if; end process; comp: process(counter) -- процесс"КОМПАРАТОР" begin if(counter= 5) then -- если счетчик = уставке clr_count<='1'; -- активируем сигнал сброса счетчика led_temp<=not led_temp; -- переключаем триггер выходного сигнала else clr_count<='0'; -- иначе "на всякий" обнуляем сигнал сброса end if; end process; led_n(0)<=led_temp; end Structural; Имеем следующее предупреждение от ISE Xst:737 - Found 1-bit latch for signal <led_temp>. Latches may be generated from incomplete case or if statements. We do not recommend the use of latches in FPGA/CPLD designs, as they may lead to timing problems. Я понял так: синтезатору не нравится неопределенность следующей конструкции if(counter= 5) then -- если счетчик = уставке clr_count<='1'; -- активируем сигнал сброса счетчика led_temp<=not led_temp; -- переключаем триггер выходного сигнала else clr_count<='0'; -- иначе "на всякий" обнуляем сигнал сброса end if; Т. е. led_temp<=not led_temp при counter=5, а вот чему равен led_temp при counter(не равно)5 фиг его знает. Вопрос. Правильно ли я понял и во что это может вылиться? Вообще насколько критичны предупреждения выдаваемые компилятором? -

Оно. Спасибо!

-

Мигание светодиодом

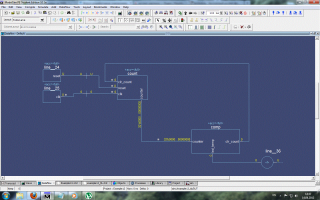

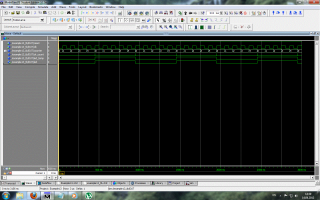

Rock87 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Потихоньку "въезжаю" в ПЛИС. Т. к. общение с преподователем ограничено, просьба покритиковать мой проект. Суть работы заключается в "моргании" светодиодом. Текст проекта на VHDL: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity Example13 is Port ( reset : in STD_LOGIC; -- сигнал сброса reset clk : in STD_LOGIC; -- входной сигнал генератора led : out STD_LOGIC); -- выходной сигнал на светодиод end Example13; architecture Behavioral of Example13 is signal counter: std_logic_vector (31 downto 0):=(others=>'0');-- объявляем сигнал counter в котором будем считать тики генератора signal led_temp: std_logic:='0'; -- триггер выходного сигнала led signal clr_count: std_logic:='0'; -- сброс счетчика при совпадении компаратора begin count: process(clk, reset, clr_count) -- процесс"СЧЕТЧИК" begin if(reset='0' or clr_count='1') then -- если нажата кнопка reset или сигнал сброса счетчика установлен в 1 counter <= (others=>'0'); -- обнуляем счетчик elsif(rising_edge(clk)) then -- если нет, то по фронту сигнала clk считаем тики генератора counter <= counter + 1; end if; end process; comp: process(counter) -- процесс"КОМПАРАТОР" begin if(counter= 5) then -- если счетчик = уставке clr_count<='1'; -- активируем сигнал сброса счетчика led_temp<=not led_temp; -- переключаем триггер выходного сигнала else clr_count<='0'; -- иначе "на всякий" обнуляем сигнал сброса end if; end process; led<=led_temp; -- соединяем триггер led_temp с выходным сигналом led end Behavioral; В принципе работает. И сразу одна "непонятка" если перенести строку led<=led_temp в процесс comp, после строчки led_temp<=not led_temp, то при симуляции получается какая то фигня. Что это такое? Да и еще. А здесь можно большие куски текста под спойлер сворачивать? -

Как свернуть часть текста в блок?

Rock87 опубликовал тема в Среды разработки - обсуждаем САПРы

Подскажите как можно свернуть часть текста в блок и разворачивать его или сворачивать щелкая по "+" или "-"? -

"обнуление" сигнала

Rock87 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Потихоньку разбираюсь с ПЛИС. Пишу на VHDL. Допустим имеем сигнал signal sig std_logic_vector (7 downto 0); и в какой то момент нужно записать во все его разряды нули (обнулить). Вижу два варианта: 1. sig<=X"00"; -- в этом случае при изменении разрядности сигнала придется изменять и разрядность данных X"00". -- А что делать есть ли разрядность сигнала не кратна байту? 2. sig<=(other=>0); -- работает, но смущает описание: Ключевое слово others употребляется в нескольких случаях. 1. Имеется возможность использовать слово "others", которое назначает значение всем другим элементам массива, которые не были определены. signal X : bit_vector (3 downto 0); signal A, B, C, D : bit; signal BYTE : bit_vector (7 downto 0); X <= (3=>’1’, 1=>’O’, others => B); 2. В операторе case. process (A, В, С, X) begin case X is when 0 to 4 => Z <= B; when 5 => Z <= C; when 7 | 9 => Z <= A; when others => Z <= 0; end case; end process; Внимание, вопрос! :rolleyes: А как Вы делаете?