SamuraY

Участник-

Постов

67 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о SamuraY

-

Звание

Участник

- День рождения 12.02.1986

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

2 064 просмотра профиля

-

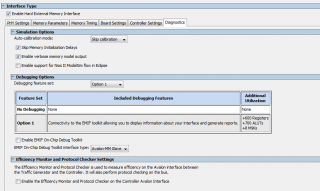

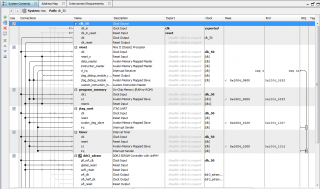

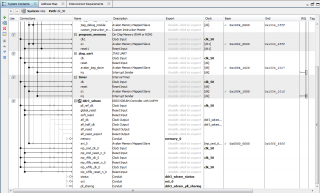

Вот настройки моего работающего проекта. С рекомендациями форума Altera заработало сразу. Изначально у меня был выключен ODT и стояли другие тайминги (из пресетов для MT41J128M16HA-15E, которая ближайший аналог MT41J128M16JT-125)

-

Заработало с настройками, которые посоветовали на форуме Altera: http://www.alteraforum.com/forum/showthrea...88&p=219645

-

А проблема может быть в том, что к FPGA подключено два х16 чипа MT41J128M16JT-125 с общими шинами команд и адреса, а я подключил контроллер только к одному чипу? И FPGA сейчас драйвит шины комманд и адреса того второго чипа, но не шину данных.

-

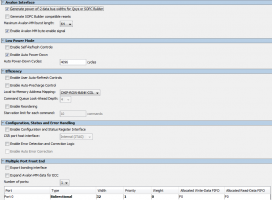

Здравствуйте, уважаемые коллеги! Помогите пожалуйста решить проблему. Есть кастомная плата с CycloneV и DDR3 (MT41J128M16JT-125). В Quartus II v14.1.0 (64bit) делаю SoC (NIOSII + block ram + hard SDRAM Uniphy controller + внешняя DDR3 + всякая мелочь). Программа грузится из блочной памяти и должна проверять DDR3 SDRAM. Все вешается при попытке доступа к SDRAM (до этого момента код выполняется из блочной памяти нормально). Установлено, что контроллер памяти не заканчивает этап калибровки (DDR3 calibration fail). Сигналы local_init_done и local_cal_success неактивны. Сигнал local_cal_fail активен. Из положительных моментов: 1) RTL тестбенч сгенерированный QSYS работает с памятью нормально (local_init_done=local_cal_success=1, видны транзакции), 2) PLL контроллера памяти стартует (pll_sharing_pll_locked активен. Контролирую через светодиод). 3) External Memory Interface Toolkit память видит и подключается к ней (значит транзакции на авалоне проходят нормально?). Можно делать ресет памяти (После этого сигнал local_cal_fail становится на мгновение неактивным и потом снова возвращается в активное состояние. Контролирую светодиодом). По результатам репортов External Memory Interface Toolkit фейл происходит на этапе Write Calibration - Per-bit write deskew failure. Частота работы с памятью 400 МГц. Тайминги брал из пресетов на MT41J128M16HA-125 (на плате MT41J128M16JT-125. Но ведь разница по сути только в типе корпуса?) Board Settings кастомной платы не известны. Оставил по умолчанию. Сейчас пробую их узнать, но пока информации нет. Не знаю на сколько это важно, но RZQ резистор IO банка FPGA, к которому подключены выводы DDR, имеет сопротивление 240 Ом. Вроде все симптомы описал. В аттаче скрины QSYS, репорт External Memory Interface Toolkit, архив с проектом. Буду очень признателен за подсказки и уделенное время! ddr3.rar linux_soc_Calibration_Report.rar

-

Как раз недавно столкнулся с подобнной ситуацией. Как правильно указали выше, все ломалось на попытке загрузить через JTAG прогу на выполнение из DDR SDRAM, при неправильно работающем контроллере памяти. Если добавить в SoC внутреннюю блочную память и в настройках linker script BSP указать эту самую блочную память для всех сегментов, программа запустится из блочной памяти. Но проблема с неработающей DDR SDRAM останется. Причин тому может быть миллион (но скорее всего неправильные настройки контроллера памяти).

-

Вопрос по TCAD

SamuraY опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

Здравствуйте. Разбираюсь с Sentaurus TCAD 2012. Пробую делать диод на основе p-n перехода: https://vk.com/doc2272082_323153276?hash=6a...7b8a769437b8604 Все что написано в инструкции получается. Но захотелось поексперементировать. После нанесения алюминия добавил в конец командного файла строчку: diffuse time=10 temp=900 А диффузия алюминия в кремний не происходит. Пробовал нагревать до 1200 градусов на протяжении 60 минут - все равно ничего не меняется. Скажите пожалуйста, почему алюминий не дифундирует в кремний? Что делаю не так? -- С уважением, Короткий Женя -

Проблема решилась. Внимательно просмотрел логи и увидел, что не выполняются placement optimization, preCTS и postCTS оптимизации. Вместо выполнения выдается ошибка Badly placed ()'s. Как я понял это ошибка одного из Tcl скриптов Encounter. Оказалось так происходит из-за имени директории - "Task#14(Q-pipe)" Возможно все дело в круглых скобках. Изменил имя директории на "g_pipe", оптимизации заработали и топология развелась на первой же итерации. Вывод такой, что скорее всего placement, без оптимизаций, выполняется довольно коряво, возможно пины ячеек не совпадают с сеткой трассировки, вследствие чего возникают проблемы с автоматической разводкой топологии.

-

Здравствуйте! Изучаю place&route в Encounter 11.12 В RTL Compiler синтезировал простейшую схему (RTL описание в приложенном архиве) и пытаюсь сделать place&route в Encounter. Скрипты, которые использую для P&R тоже в архиве. Посмотрите их если не сложно, нет ли там глобальных косяков, т.к. я в этом деле вообще зеленый. Так вот, никак не хочет делаться роутинг без DRC violations. Играюсь коэффициентом заполнения флурплана - минимальное кол-во violations получается для значения 0.7 (2 violations). Однако устранить их никак не получается. Видимо из-за того, что я ноль в P&R. Примерная картина этих DRC violations изображена в файле DRC_violations.JPG Как видно там присутствуют и закоротки и нарушения минимального расстояния между объектами. Как я понял, внутренняя топология стандартных ячеек разводится тоже в металле 1 и когда Encounter тулит межсоединение между первым и вторым металлом, оно очень часто закорачивается с проводниками разводки внутри стандартной ячейки. Заполнение проводниками 4-го металла получается минимальным. Основную разводку Encounter делает во втором и третьем металлах. Все DRC violations вылазят в первом металле и имеют характер, описанный выше. Само устройство элементарное. Не понимаю откуда проблемы в разводке топологии. Подскажите пожалуйста, что делаю не так. Буду очень признателен за любую помощь! xxx.rar

-

2 Tiro: "Сколько всего регистров на запись? Квартус тебя за это не обругал?" 31 регистр на запись. Для нулевого адреса квартус ставит логику, опускающую we в ноль. Ворнингов тоже не выдает. С точки зрения корректности Verilog кода, поскольку нулевой индекс в массиве отсутствует, это явно указывает на то, что писать по такому адресу не нужно. Так что здесь не вижу проблемы. Поправьте, если ошибаюсь. 2 Sefo: Спасибо большое за ликбез! :)

-

Quartus непонятно синтезирует Verilog код

SamuraY опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте, уважаемые форумчане. Синтезирую в Quartus II v.9.1. sp1 регистровый файл для MIPS процессора: module regFile(i_clk, i_raddr1, i_raddr2, i_waddr, i_wdata, i_we, o_rdata1, o_rdata2 ); input i_clk, i_we; input [4:0] i_raddr1, i_raddr2, i_waddr; input [31:0] i_wdata; output [31:0] o_rdata1, o_rdata2; reg [31:0] regs[31:1]; always @(posedge i_clk) if(i_we) regs[i_waddr] <= i_wdata; assign o_rdata1 = (i_raddr1 != 0) ? regs[i_raddr1] : 32'd0; assign o_rdata2 = (i_raddr2 != 0) ? regs[i_raddr2] : 32'd0; endmodule Поскольку из нулевого регистра всегда должен считываться ноль, аппаратно его не хочу реализовать и описываю массив для хранения регистров, как reg [31:0] regs[31:1] Quartus же из такого кода синтезирует не 31, а 32 регистра. Не подскажете почему? -

Вот проект MIPS32, созданный в Electric: http://www4.hmc.edu:8001/Engineering/158/0...ject/index.html а потом изготовленный через MOSIS. На страничке куча исходников, в т.ч. и для Electric.

-

Спасибо за ссылку. Всю эту теорию я знаю. Если вы имели в виду цитату "Эти токи направлены в разные стороны и в отсутствие внешнего электрического поля компенсируют друг друга. Поэтому полный ток через переход равен нулю", то она не дает полного ответа на мой вопрос, т.к. в этой цитате имеется в виду разомкнутая цепь, а меня интересовала замкнутая. Но я таки наконец понял почему вольтметр не показывает эту внутреннюю разность потенциалов. И помогло ваше разъяснение на счет того, что в диоде который не подвергается электромагнитному облучению отсутствует ЭДС которая снабжает электронами n область и обедняет ими p-область. Другими словами объемный пространственный заряд (ОПЗ) ионов примесей в области pn-перехода создает разность потенциалов, но эта разность потенциалов не приводит к появлению тока в замкнутой цепи, поскольку внутри ОПЗ отсутствует электродвижущая сила (ОПЗ - это диэлектрик). Возьмем диод, замкнет его через резистор и допустим, что под действием внутреннего поля, которое создается нескомпенсированными положительными ионами примесей в n области и отр. ионами в p области, электроны будут двигаться через резистор из p области в n. Но когда эти электроны попадут в n область их будет тормозить это же поле которое якобы приводит их в движение. Пришли к противоречию. Ну а раз ток не течет, то и потенциальный барьер нельзя измерить при помощи вольтметра и нужно использовать другие методы.

-

Так в том то и дело, что вечного двигателя не существует и вольтметр показывает 0. Мне интересно понять физику процесса, почему там 0 вольт, а теория говорит о существовании внутри pn-перехода потенциального барьера 0.5 - 0.8 вольт в зависимости от температуры и концентрации примесей в p и n областях. Какие силы экранируют/компенсируют эту встроенную разность потенциалов?

-

Да, эт я ошибся, прошу прощения. Внутри неосвещенного p-n перехода эдс нет, но напряжение даже при отсутствии внешнего смещения есть. Почему вольтметр не показывает это напряжение?

-

Но в учебниках по твердотельной электронике пишут, что эти положительные и отрицательные ионы даже при отсутствии внешнего смещения создают в области p-n перехода разность потенциалов (потенциальный барьер) и электрическое поле, которое препятствует диффузии основных носителей и переносит неосновные носители из одной области в другую. Правильно? Почему это внутреннее поле не является источником ЭДС? Оно же создает дрейфовый ток неосновных носителей из одной области в другую.